This is Webservice SDK for mbed. LPCXpresso1769/LPC1768/FRDM-K64F/LPC4088

Dependents: MbedFileServer_1768MiniDK2 RedWireBridge IssueDebug_gcc MiMicRemoteMCU-for-Mbed ... more

libMiMic(MiMic library for mbed)は、WebService機能を提供するSDKです。 mbedでWebAPIに対応したネットワークデバイスを簡単に作ることが出来ます。

libMiMicはMiMic projectで開発しています。MiMic projectについてはこちらをご覧ください。 http://nyatla.jp/mimic/wp/

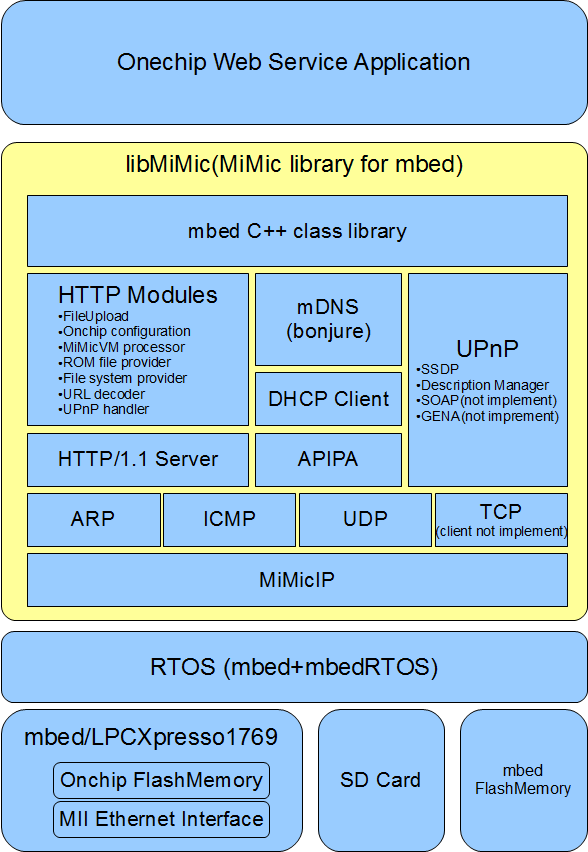

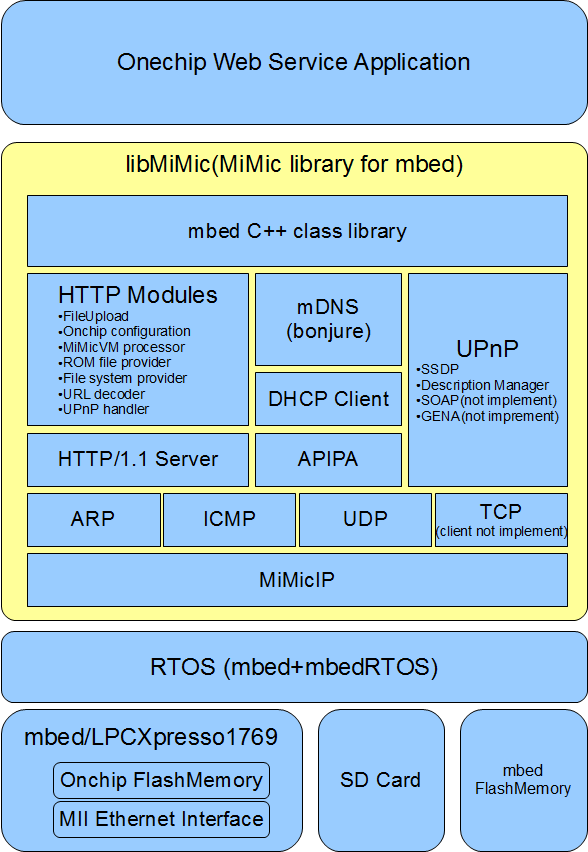

構成

libMiMicはmbedRTOS上で動作し、ユーザアプリケーションにAPIを提供します。コアAPIはC言語で記述されていますが、使用頻度の高いものについてはmbed向けのC++APIが準備されています。

※libMiMicはmbedの標準イーサネットドライバをしようしていません。

標準イーサネットドライバと同時に使用することはできません。

- MiMicIP - IPv4スタックです。レテンシとメモリ消費量を抑えたuipベースのライブラリです。

- ARP/ICMP/UDP/TCP - 基礎的なソケットAPIを提供します。APIは独自です。

- HTTP/1.1 Server - HTTP/1.1に対応したサーバです。マルチセッション・Chunked・持続性接続に対応しています。

- HTTP Modules - HTTP/1.1の機能モジュールです。以下のモジュールがあります。

- ROM file provider - ROMに格納したファイルイメージを公開します。

- File system provider - mbedファイルシステムを公開します。

- Onchip configuration - プログラムフラッシュを利用して設定を保存します。

- MiMicVM processor - RPCリクエスト(MiMicVM)を処理します。

- FileUpload - ファイルアップロードを受け取ります。

- URL decoder - HTTPリクエストを解析します。

- UPnP handler -UPnPメッセージを処理します。

- WebSocket - Websocketサーバです。

- mDNS - マルチキャストDNSサービスです。

- UPnP - UPnP/1.0の機能を提供します。UPnP handlerと協調して動作します。(現在はデバイス探索(SSDP)・デスクリプション(Description)のみ実装してあります。)

- DHCP/APIPA - ゼロコンフィギュレーション用のモジュールです。

- HTTP/1.1 Client

- mbed C++ class library - mbed向けのC++CPIです。C言語のものより簡単です。

対応機種

- mbed(mbed LPC1768)

- LPCXpresso1769

プログラム

Import programMiMicRemoteMCU-for-Mbed

MiMic RemoteMCU for mbed. This program provides MCU control API over REST API. It can control MCU from Javascript,PHP or any HTTP rest client directly. And, The application has self development environment.

Import programMbedFileServer

The program publishes files at local directory and SD filesystem. It is a full-fledged webServer somewhat.

サンプル

Import programMiMicSimpleHttpd

This is a simplest HTTP server made of libMiMic. It will echo back a request path.

Import programUPnPBasicDevice

Simplest UPnP basic device example. This program to run UPnP basic device on the mbed.

Import programWebSocketSample

MiMicSDK Websocket module sample program.

Import programHttpClientSamlpe

A http client sample program.

Import programTcpSocketClientSamlpe

MiMicSDK Tcp client socket sample program.

Import programUdpSocketSamlpe

Udp socket sample program. This program will send back the received packet.

チュートリアル

- HTTPD解説

- UPnPデバイスの作り方

- MiMicRemoteMCUの紹介(pdf)

- MiMicRemoteMCUのマニュアル(pdf)

English

libMiMic(MiMic library for mbed) is SDK which provides Webservice functions. It can be created networking device easily using mbed.

See more MiMic information, See MiMic project website. http://nyatla.jp/mimic/wp/

Structure

libMiMic run on mbed RTOS and provides networking API to user application. This library has C++ class API for the mbed, and low-level C language API.

For WebService general, it can be written in a simple C + + API.

libMiMic does not have the standard Ethernet driver of mbed. It is not possible that will be used with the standard Ethernet driver.

- MiMicIP - IPv4 protocol stack. This is based uip which is reduced memory and latency.

- ARP / ICMP / UDP / TCP - Those are provide basic IP protocols.

- HTTP/1.1 Server - The Http server compatible HTTP/1.1. It supports multi-session, chunked transport, persistent connection.

- HTTP Modules - There are addon-module for HTTP server. The following modules.

- ROM file module - Publish the file images in ROM.

- File system module - Publish thefiles in mbed file system.

- Onchip configuration module - To save the network settings to the program flash via REST.

- MiMicVM module - To handle the (MiMicVM) RPC request.

- FileUpload module - Accept a file via HTTP POST.

- URL dedoce module - A versatility URL decoder.

- UPnP handle module - To handle UPnP messages.

- UPnP - This provides UPnP/1.0 device functions. It works together with UPnP handler.

- Websocket - websocket (version13) server

- mDNS Service - DNS-SD protocol server.

- UPnP - This provides UPnP/1.0 device functions which works with UPnP handler. (You have been implemented (SSDP) ? description only (Description) device search now.) It is a module zero configuration for - DHCP / APIPA. mbed C + + class library - C of mbed for + + is the CPI. It is simple than that of the C language.

- DHCP/APIPA - It support zero-cpnfigulation.

- mbed C++ class library. Almost APIs for Web applications are available.

- HTTP/1.1 Client

Supported target

- mbed(mbed LPC1768)

- LPCXpresso1769

Application

Import programMiMicRemoteMCU-for-Mbed

MiMic RemoteMCU for mbed. This program provides MCU control API over REST API. It can control MCU from Javascript,PHP or any HTTP rest client directly. And, The application has self development environment.

Import programMbedFileServer

The program publishes files at local directory and SD filesystem. It is a full-fledged webServer somewhat.

Sample

Import programMiMicSimpleHttpd

This is a simplest HTTP server made of libMiMic. It will echo back a request path.

Import programUPnPBasicDevice

Simplest UPnP basic device example. This program to run UPnP basic device on the mbed.

Import programWebSocketSample

MiMicSDK Websocket module sample program.

Import programHttpClientSamlpe

A http client sample program.

Import programTcpSocketClientSamlpe

MiMicSDK Tcp client socket sample program.

Import programUdpSocketSamlpe

Udp socket sample program. This program will send back the received packet.

Tutorial

- HTTPD hello world.

- How to make own UPnP device.

- MiMicRemoteMCUの紹介(pdf)

- MiMicRemoteMCUのマニュアル(pdf)

core/driver/ethernet/lpc17xx/EtherDev_DP83848C.c@68:f7def7eb5504, 2014-05-22 (annotated)

- Committer:

- nyatla

- Date:

- Thu May 22 12:59:50 2014 +0000

- Revision:

- 68:f7def7eb5504

- Child:

- 69:8c5f220441f5

MiMic-core ?344???;

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| nyatla | 68:f7def7eb5504 | 1 | /* |

| nyatla | 68:f7def7eb5504 | 2 | FreeRTOS V7.0.0 - Copyright (C) 2011 Real Time Engineers Ltd. |

| nyatla | 68:f7def7eb5504 | 3 | |

| nyatla | 68:f7def7eb5504 | 4 | |

| nyatla | 68:f7def7eb5504 | 5 | *************************************************************************** |

| nyatla | 68:f7def7eb5504 | 6 | * * |

| nyatla | 68:f7def7eb5504 | 7 | * FreeRTOS tutorial books are available in pdf and paperback. * |

| nyatla | 68:f7def7eb5504 | 8 | * Complete, revised, and edited pdf reference manuals are also * |

| nyatla | 68:f7def7eb5504 | 9 | * available. * |

| nyatla | 68:f7def7eb5504 | 10 | * * |

| nyatla | 68:f7def7eb5504 | 11 | * Purchasing FreeRTOS documentation will not only help you, by * |

| nyatla | 68:f7def7eb5504 | 12 | * ensuring you get running as quickly as possible and with an * |

| nyatla | 68:f7def7eb5504 | 13 | * in-depth knowledge of how to use FreeRTOS, it will also help * |

| nyatla | 68:f7def7eb5504 | 14 | * the FreeRTOS project to continue with its mission of providing * |

| nyatla | 68:f7def7eb5504 | 15 | * professional grade, cross platform, de facto standard solutions * |

| nyatla | 68:f7def7eb5504 | 16 | * for microcontrollers - completely free of charge! * |

| nyatla | 68:f7def7eb5504 | 17 | * * |

| nyatla | 68:f7def7eb5504 | 18 | * >>> See http://www.FreeRTOS.org/Documentation for details. <<< * |

| nyatla | 68:f7def7eb5504 | 19 | * * |

| nyatla | 68:f7def7eb5504 | 20 | * Thank you for using FreeRTOS, and thank you for your support! * |

| nyatla | 68:f7def7eb5504 | 21 | * * |

| nyatla | 68:f7def7eb5504 | 22 | *************************************************************************** |

| nyatla | 68:f7def7eb5504 | 23 | |

| nyatla | 68:f7def7eb5504 | 24 | |

| nyatla | 68:f7def7eb5504 | 25 | This file is part of the FreeRTOS distribution. |

| nyatla | 68:f7def7eb5504 | 26 | |

| nyatla | 68:f7def7eb5504 | 27 | FreeRTOS is free software; you can redistribute it and/or modify it under |

| nyatla | 68:f7def7eb5504 | 28 | the terms of the GNU General Public License (version 2) as published by the |

| nyatla | 68:f7def7eb5504 | 29 | Free Software Foundation AND MODIFIED BY the FreeRTOS exception. |

| nyatla | 68:f7def7eb5504 | 30 | >>>NOTE<<< The modification to the GPL is included to allow you to |

| nyatla | 68:f7def7eb5504 | 31 | distribute a combined work that includes FreeRTOS without being obliged to |

| nyatla | 68:f7def7eb5504 | 32 | provide the source code for proprietary components outside of the FreeRTOS |

| nyatla | 68:f7def7eb5504 | 33 | kernel. FreeRTOS is distributed in the hope that it will be useful, but |

| nyatla | 68:f7def7eb5504 | 34 | WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY |

| nyatla | 68:f7def7eb5504 | 35 | or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for |

| nyatla | 68:f7def7eb5504 | 36 | more details. You should have received a copy of the GNU General Public |

| nyatla | 68:f7def7eb5504 | 37 | License and the FreeRTOS license exception along with FreeRTOS; if not it |

| nyatla | 68:f7def7eb5504 | 38 | can be viewed here: http://www.freertos.org/a00114.html and also obtained |

| nyatla | 68:f7def7eb5504 | 39 | by writing to Richard Barry, contact details for whom are available on the |

| nyatla | 68:f7def7eb5504 | 40 | FreeRTOS WEB site. |

| nyatla | 68:f7def7eb5504 | 41 | |

| nyatla | 68:f7def7eb5504 | 42 | 1 tab == 4 spaces! |

| nyatla | 68:f7def7eb5504 | 43 | |

| nyatla | 68:f7def7eb5504 | 44 | http://www.FreeRTOS.org - Documentation, latest information, license and |

| nyatla | 68:f7def7eb5504 | 45 | contact details. |

| nyatla | 68:f7def7eb5504 | 46 | |

| nyatla | 68:f7def7eb5504 | 47 | http://www.SafeRTOS.com - A version that is certified for use in safety |

| nyatla | 68:f7def7eb5504 | 48 | critical systems. |

| nyatla | 68:f7def7eb5504 | 49 | |

| nyatla | 68:f7def7eb5504 | 50 | http://www.OpenRTOS.com - Commercial support, development, porting, |

| nyatla | 68:f7def7eb5504 | 51 | licensing and training services. |

| nyatla | 68:f7def7eb5504 | 52 | */ |

| nyatla | 68:f7def7eb5504 | 53 | |

| nyatla | 68:f7def7eb5504 | 54 | /* Originally adapted from file written by Andreas Dannenberg. Supplied with permission. */ |

| nyatla | 68:f7def7eb5504 | 55 | /* |

| nyatla | 68:f7def7eb5504 | 56 | * Modified for MiMic by R.Iizuka. 2011.08.27 |

| nyatla | 68:f7def7eb5504 | 57 | * http://nyatla.jp/mimic |

| nyatla | 68:f7def7eb5504 | 58 | */ |

| nyatla | 68:f7def7eb5504 | 59 | |

| nyatla | 68:f7def7eb5504 | 60 | #include "NyLPC_config.h" |

| nyatla | 68:f7def7eb5504 | 61 | #if NyLPC_MCU==NyLPC_MCU_LPC17xx |

| nyatla | 68:f7def7eb5504 | 62 | |

| nyatla | 68:f7def7eb5504 | 63 | |

| nyatla | 68:f7def7eb5504 | 64 | /* Kernel includes. */ |

| nyatla | 68:f7def7eb5504 | 65 | #include "../NyLPC_cEthernetMM.h" |

| nyatla | 68:f7def7eb5504 | 66 | #include "EtherDev_DP83848C_protected.h" |

| nyatla | 68:f7def7eb5504 | 67 | #include "LPC17xx.h" |

| nyatla | 68:f7def7eb5504 | 68 | #include "NyLPC_os.h" |

| nyatla | 68:f7def7eb5504 | 69 | |

| nyatla | 68:f7def7eb5504 | 70 | |

| nyatla | 68:f7def7eb5504 | 71 | #define DP83848C_ID 0x20005C90 /* PHY Identifier */ |

| nyatla | 68:f7def7eb5504 | 72 | |

| nyatla | 68:f7def7eb5504 | 73 | /* DP83848C PHY Registers */ |

| nyatla | 68:f7def7eb5504 | 74 | #define PHY_REG_BMCR 0x00 /* Basic Mode Control Register */ |

| nyatla | 68:f7def7eb5504 | 75 | #define PHY_REG_BMSR 0x01 /* Basic Mode Status Register */ |

| nyatla | 68:f7def7eb5504 | 76 | #define PHY_REG_IDR1 0x02 /* PHY Identifier 1 */ |

| nyatla | 68:f7def7eb5504 | 77 | #define PHY_REG_IDR2 0x03 /* PHY Identifier 2 */ |

| nyatla | 68:f7def7eb5504 | 78 | #define PHY_REG_ANAR 0x04 /* Auto-Negotiation Advertisement */ |

| nyatla | 68:f7def7eb5504 | 79 | #define PHY_REG_ANLPAR 0x05 /* Auto-Neg. Link Partner Abitily */ |

| nyatla | 68:f7def7eb5504 | 80 | #define PHY_REG_ANER 0x06 /* Auto-Neg. Expansion Register */ |

| nyatla | 68:f7def7eb5504 | 81 | #define PHY_REG_ANNPTR 0x07 /* Auto-Neg. Next Page TX */ |

| nyatla | 68:f7def7eb5504 | 82 | |

| nyatla | 68:f7def7eb5504 | 83 | /* PHY Extended Registers */ |

| nyatla | 68:f7def7eb5504 | 84 | #define PHY_REG_STS 0x10 /* Status Register */ |

| nyatla | 68:f7def7eb5504 | 85 | #define PHY_REG_MICR 0x11 /* MII Interrupt Control Register */ |

| nyatla | 68:f7def7eb5504 | 86 | #define PHY_REG_MISR 0x12 /* MII Interrupt Status Register */ |

| nyatla | 68:f7def7eb5504 | 87 | #define PHY_REG_FCSCR 0x14 /* False Carrier Sense Counter */ |

| nyatla | 68:f7def7eb5504 | 88 | #define PHY_REG_RECR 0x15 /* Receive Error Counter */ |

| nyatla | 68:f7def7eb5504 | 89 | #define PHY_REG_PCSR 0x16 /* PCS Sublayer Config. and Status */ |

| nyatla | 68:f7def7eb5504 | 90 | #define PHY_REG_RBR 0x17 /* RMII and Bypass Register */ |

| nyatla | 68:f7def7eb5504 | 91 | #define PHY_REG_LEDCR 0x18 /* LED Direct Control Register */ |

| nyatla | 68:f7def7eb5504 | 92 | #define PHY_REG_PHYCR 0x19 /* PHY Control Register */ |

| nyatla | 68:f7def7eb5504 | 93 | #define PHY_REG_10BTSCR 0x1A /* 10Base-T Status/Control Register */ |

| nyatla | 68:f7def7eb5504 | 94 | #define PHY_REG_CDCTRL1 0x1B /* CD Test Control and BIST Extens. */ |

| nyatla | 68:f7def7eb5504 | 95 | #define PHY_REG_EDCR 0x1D /* Energy Detect Control Register */ |

| nyatla | 68:f7def7eb5504 | 96 | |

| nyatla | 68:f7def7eb5504 | 97 | #define PHY_FULLD_100M 0x2100 /* Full Duplex 100Mbit */ |

| nyatla | 68:f7def7eb5504 | 98 | #define PHY_HALFD_100M 0x2000 /* Half Duplex 100Mbit */ |

| nyatla | 68:f7def7eb5504 | 99 | #define PHY_FULLD_10M 0x0100 /* Full Duplex 10Mbit */ |

| nyatla | 68:f7def7eb5504 | 100 | #define PHY_HALFD_10M 0x0000 /* Half Duplex 10MBit */ |

| nyatla | 68:f7def7eb5504 | 101 | #define PHY_AUTO_NEG 0x3000 /* Select Auto Negotiation */ |

| nyatla | 68:f7def7eb5504 | 102 | #define PHY_AUTO_NEG_COMPLETE 0x0020 /* Auto negotiation have finished. */ |

| nyatla | 68:f7def7eb5504 | 103 | #define ETHDEV_PHY_DEF_ADR 0x0100 /* Default PHY device address */ |

| nyatla | 68:f7def7eb5504 | 104 | |

| nyatla | 68:f7def7eb5504 | 105 | |

| nyatla | 68:f7def7eb5504 | 106 | #ifndef configEMAC_INTERRUPT_PRIORITY |

| nyatla | 68:f7def7eb5504 | 107 | #define configEMAC_INTERRUPT_PRIORITY 5 |

| nyatla | 68:f7def7eb5504 | 108 | #endif |

| nyatla | 68:f7def7eb5504 | 109 | |

| nyatla | 68:f7def7eb5504 | 110 | /* Time to wait between each inspection of the link status. */ |

| nyatla | 68:f7def7eb5504 | 111 | #define emacWAIT_FOR_LINK_TO_ESTABLISH_MS 500 |

| nyatla | 68:f7def7eb5504 | 112 | |

| nyatla | 68:f7def7eb5504 | 113 | /* Short delay used in several places during the initialisation process. */ |

| nyatla | 68:f7def7eb5504 | 114 | #define emacSHORT_DELAY_MS 10 |

| nyatla | 68:f7def7eb5504 | 115 | |

| nyatla | 68:f7def7eb5504 | 116 | /* Hardware specific bit definitions. */ |

| nyatla | 68:f7def7eb5504 | 117 | #define emacPINSEL2_VALUE ( 0x50150105 ) |

| nyatla | 68:f7def7eb5504 | 118 | |

| nyatla | 68:f7def7eb5504 | 119 | /* If no buffers are available, then wait this long before looking again.... */ |

| nyatla | 68:f7def7eb5504 | 120 | #define emacBUFFER_WAIT_DELAY_MS 3 |

| nyatla | 68:f7def7eb5504 | 121 | #define emacBUFFER_WAIT_EMPTY_MS 10 |

| nyatla | 68:f7def7eb5504 | 122 | |

| nyatla | 68:f7def7eb5504 | 123 | /* ...and don't look more than this many times. */ |

| nyatla | 68:f7def7eb5504 | 124 | #define emacBUFFER_WAIT_ATTEMPTS ( 30 ) |

| nyatla | 68:f7def7eb5504 | 125 | |

| nyatla | 68:f7def7eb5504 | 126 | /* Index to the Tx descriptor that is always used first for every Tx. The second |

| nyatla | 68:f7def7eb5504 | 127 | descriptor is then used to re-send in order to speed up the uIP Tx process. */ |

| nyatla | 68:f7def7eb5504 | 128 | #define emacTX_DESC_INDEX ( 0 ) |

| nyatla | 68:f7def7eb5504 | 129 | |

| nyatla | 68:f7def7eb5504 | 130 | /*-----------------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 131 | |

| nyatla | 68:f7def7eb5504 | 132 | /* Setup the IO and peripherals required for Ethernet communication.*/ |

| nyatla | 68:f7def7eb5504 | 133 | static void prvSetupEMACHardware( void ); |

| nyatla | 68:f7def7eb5504 | 134 | /* Control the auto negotiate process.*/ |

| nyatla | 68:f7def7eb5504 | 135 | static void prvConfigurePHY( void ); |

| nyatla | 68:f7def7eb5504 | 136 | /* |

| nyatla | 68:f7def7eb5504 | 137 | * Wait for a link to be established, then setup the PHY according to the link |

| nyatla | 68:f7def7eb5504 | 138 | * parameters. |

| nyatla | 68:f7def7eb5504 | 139 | */ |

| nyatla | 68:f7def7eb5504 | 140 | static NyLPC_TBool prvSetupLinkStatus( void ); |

| nyatla | 68:f7def7eb5504 | 141 | /* |

| nyatla | 68:f7def7eb5504 | 142 | * Send lValue to the lPhyReg within the PHY. |

| nyatla | 68:f7def7eb5504 | 143 | */ |

| nyatla | 68:f7def7eb5504 | 144 | static NyLPC_TBool prvWritePHY( long lPhyReg, long lValue ); |

| nyatla | 68:f7def7eb5504 | 145 | /* |

| nyatla | 68:f7def7eb5504 | 146 | * Read a value from ucPhyReg within the PHY. *plStatus will be set to |

| nyatla | 68:f7def7eb5504 | 147 | * pdFALSE if there is an error. |

| nyatla | 68:f7def7eb5504 | 148 | */ |

| nyatla | 68:f7def7eb5504 | 149 | static unsigned short prvReadPHY( unsigned int ucPhyReg, long *plStatus ); |

| nyatla | 68:f7def7eb5504 | 150 | |

| nyatla | 68:f7def7eb5504 | 151 | |

| nyatla | 68:f7def7eb5504 | 152 | |

| nyatla | 68:f7def7eb5504 | 153 | static NyLPC_TBool start(const struct NyLPC_TEthAddr* i_eth_addr,NyLPC_TiEthernetDevice_onEvent i_handler,void* i_param); |

| nyatla | 68:f7def7eb5504 | 154 | static void stop(void); |

| nyatla | 68:f7def7eb5504 | 155 | static struct NyLPC_TTxBufferHeader* allocTxBuf(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size); |

| nyatla | 68:f7def7eb5504 | 156 | static void releaseTxBuf(struct NyLPC_TTxBufferHeader* i_buf); |

| nyatla | 68:f7def7eb5504 | 157 | /*-----------------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 158 | #define ETH_TX_BUF_BASE (void*)(ETH_BUF_BASE+ETH_FRAG_SIZE*NUM_RX_FRAG) |

| nyatla | 68:f7def7eb5504 | 159 | |

| nyatla | 68:f7def7eb5504 | 160 | |

| nyatla | 68:f7def7eb5504 | 161 | const static struct TiEthernetDevice _interface= |

| nyatla | 68:f7def7eb5504 | 162 | { |

| nyatla | 68:f7def7eb5504 | 163 | "DP83848C", |

| nyatla | 68:f7def7eb5504 | 164 | start, |

| nyatla | 68:f7def7eb5504 | 165 | stop, |

| nyatla | 68:f7def7eb5504 | 166 | EthDev_LPC17xx_getRxEthFrame, |

| nyatla | 68:f7def7eb5504 | 167 | EthDev_LPC17xx_nextRxEthFrame, |

| nyatla | 68:f7def7eb5504 | 168 | allocTxBuf, |

| nyatla | 68:f7def7eb5504 | 169 | releaseTxBuf, |

| nyatla | 68:f7def7eb5504 | 170 | EthDev_LPC17xx_sendTxEthFrame, |

| nyatla | 68:f7def7eb5504 | 171 | EthDev_LPC17xx_processTx |

| nyatla | 68:f7def7eb5504 | 172 | }; |

| nyatla | 68:f7def7eb5504 | 173 | |

| nyatla | 68:f7def7eb5504 | 174 | static void* _event_param; |

| nyatla | 68:f7def7eb5504 | 175 | static NyLPC_TiEthernetDevice_onEvent _event_handler; |

| nyatla | 68:f7def7eb5504 | 176 | |

| nyatla | 68:f7def7eb5504 | 177 | /** EMAC ISRハンドラ*/ |

| nyatla | 68:f7def7eb5504 | 178 | static void emacIsrHandler(unsigned long i_status); |

| nyatla | 68:f7def7eb5504 | 179 | |

| nyatla | 68:f7def7eb5504 | 180 | /* |

| nyatla | 68:f7def7eb5504 | 181 | * EthernetDeviceのファクトリー関数 |

| nyatla | 68:f7def7eb5504 | 182 | */ |

| nyatla | 68:f7def7eb5504 | 183 | |

| nyatla | 68:f7def7eb5504 | 184 | NyLPC_TBool EthDev_DP83848C_getInterface( |

| nyatla | 68:f7def7eb5504 | 185 | const struct TiEthernetDevice** o_dev) |

| nyatla | 68:f7def7eb5504 | 186 | { |

| nyatla | 68:f7def7eb5504 | 187 | unsigned long ulID1, ulID2; |

| nyatla | 68:f7def7eb5504 | 188 | NyLPC_TBool lReturn = NyLPC_TBool_TRUE; |

| nyatla | 68:f7def7eb5504 | 189 | //Reset MCU Interface. and wait for reset. |

| nyatla | 68:f7def7eb5504 | 190 | prvSetupEMACHardware(); |

| nyatla | 68:f7def7eb5504 | 191 | //Check peripheral name |

| nyatla | 68:f7def7eb5504 | 192 | ulID1 = prvReadPHY( PHY_REG_IDR1, &lReturn ); |

| nyatla | 68:f7def7eb5504 | 193 | ulID2 = prvReadPHY( PHY_REG_IDR2, &lReturn ); |

| nyatla | 68:f7def7eb5504 | 194 | if( ( (ulID1 << 16UL ) | ( ulID2 & 0xFFF0UL ) ) != DP83848C_ID) |

| nyatla | 68:f7def7eb5504 | 195 | { |

| nyatla | 68:f7def7eb5504 | 196 | return NyLPC_TBool_FALSE; |

| nyatla | 68:f7def7eb5504 | 197 | } |

| nyatla | 68:f7def7eb5504 | 198 | *o_dev=&_interface; |

| nyatla | 68:f7def7eb5504 | 199 | LPC_EMAC->TxProduceIndex = 0; |

| nyatla | 68:f7def7eb5504 | 200 | LPC_EMAC->RxConsumeIndex = 0; |

| nyatla | 68:f7def7eb5504 | 201 | return NyLPC_TBool_TRUE; |

| nyatla | 68:f7def7eb5504 | 202 | } |

| nyatla | 68:f7def7eb5504 | 203 | |

| nyatla | 68:f7def7eb5504 | 204 | |

| nyatla | 68:f7def7eb5504 | 205 | static NyLPC_TBool start(const struct NyLPC_TEthAddr* i_eth_addr,NyLPC_TiEthernetDevice_onEvent i_handler,void* i_param) |

| nyatla | 68:f7def7eb5504 | 206 | { |

| nyatla | 68:f7def7eb5504 | 207 | _event_handler=i_handler; |

| nyatla | 68:f7def7eb5504 | 208 | _event_param=i_param; |

| nyatla | 68:f7def7eb5504 | 209 | NyLPC_cIsr_setEnetISR(emacIsrHandler); |

| nyatla | 68:f7def7eb5504 | 210 | /* Set the Ethernet MAC Address registers */ |

| nyatla | 68:f7def7eb5504 | 211 | LPC_EMAC->SA0 = (((uint32_t)(i_eth_addr->addr[0])) << 8 ) | i_eth_addr->addr[1]; |

| nyatla | 68:f7def7eb5504 | 212 | LPC_EMAC->SA1 = (((uint32_t)(i_eth_addr->addr[2])) << 8 ) | i_eth_addr->addr[3]; |

| nyatla | 68:f7def7eb5504 | 213 | LPC_EMAC->SA2 = (((uint32_t)(i_eth_addr->addr[4])) << 8 ) | i_eth_addr->addr[5]; |

| nyatla | 68:f7def7eb5504 | 214 | |

| nyatla | 68:f7def7eb5504 | 215 | //TXメモリマネージャの準備 |

| nyatla | 68:f7def7eb5504 | 216 | NyLPC_cEthernetMM_initialize(ETH_TX_BUF_BASE); |

| nyatla | 68:f7def7eb5504 | 217 | |

| nyatla | 68:f7def7eb5504 | 218 | /* Initialize Tx and Rx DMA Descriptors */ |

| nyatla | 68:f7def7eb5504 | 219 | EthDev_LPC17xx_prevRxDescriptor(); |

| nyatla | 68:f7def7eb5504 | 220 | EthDev_LPC17xx_prevTxDescriptor(); |

| nyatla | 68:f7def7eb5504 | 221 | |

| nyatla | 68:f7def7eb5504 | 222 | /* Setup the PHY. */ |

| nyatla | 68:f7def7eb5504 | 223 | prvConfigurePHY(); |

| nyatla | 68:f7def7eb5504 | 224 | |

| nyatla | 68:f7def7eb5504 | 225 | //wait for Link up... |

| nyatla | 68:f7def7eb5504 | 226 | while(!prvSetupLinkStatus()) |

| nyatla | 68:f7def7eb5504 | 227 | { |

| nyatla | 68:f7def7eb5504 | 228 | NyLPC_cThread_sleep(100); |

| nyatla | 68:f7def7eb5504 | 229 | } |

| nyatla | 68:f7def7eb5504 | 230 | |

| nyatla | 68:f7def7eb5504 | 231 | /* Receive Broadcast and Perfect Match Packets */ |

| nyatla | 68:f7def7eb5504 | 232 | LPC_EMAC->RxFilterCtrl = RFC_BCAST_EN | RFC_PERFECT_EN | RFC_MCAST_EN; |

| nyatla | 68:f7def7eb5504 | 233 | |

| nyatla | 68:f7def7eb5504 | 234 | //Ethernetの割込み開始設定 |

| nyatla | 68:f7def7eb5504 | 235 | NyLPC_cIsr_enterCritical(); |

| nyatla | 68:f7def7eb5504 | 236 | { |

| nyatla | 68:f7def7eb5504 | 237 | /* Reset all interrupts */ |

| nyatla | 68:f7def7eb5504 | 238 | LPC_EMAC->IntClear = 0xffff; |

| nyatla | 68:f7def7eb5504 | 239 | LPC_EMAC->IntEnable = ( INT_RX_DONE | INT_TX_DONE ); |

| nyatla | 68:f7def7eb5504 | 240 | |

| nyatla | 68:f7def7eb5504 | 241 | /* Enable receive and transmit mode of MAC Ethernet core */ |

| nyatla | 68:f7def7eb5504 | 242 | LPC_EMAC->Command |= ( CR_RX_EN | CR_TX_EN ); |

| nyatla | 68:f7def7eb5504 | 243 | LPC_EMAC->MAC1 |= MAC1_REC_EN; |

| nyatla | 68:f7def7eb5504 | 244 | |

| nyatla | 68:f7def7eb5504 | 245 | /* Set the interrupt priority to the max permissible to cause some |

| nyatla | 68:f7def7eb5504 | 246 | interrupt nesting. */ |

| nyatla | 68:f7def7eb5504 | 247 | NVIC_SetPriority( ENET_IRQn, configEMAC_INTERRUPT_PRIORITY ); |

| nyatla | 68:f7def7eb5504 | 248 | |

| nyatla | 68:f7def7eb5504 | 249 | /* Enable the interrupt. */ |

| nyatla | 68:f7def7eb5504 | 250 | NVIC_EnableIRQ( ENET_IRQn ); |

| nyatla | 68:f7def7eb5504 | 251 | } |

| nyatla | 68:f7def7eb5504 | 252 | NyLPC_cIsr_exitCritical(); |

| nyatla | 68:f7def7eb5504 | 253 | |

| nyatla | 68:f7def7eb5504 | 254 | return NyLPC_TBool_TRUE; |

| nyatla | 68:f7def7eb5504 | 255 | |

| nyatla | 68:f7def7eb5504 | 256 | } |

| nyatla | 68:f7def7eb5504 | 257 | static void stop(void) |

| nyatla | 68:f7def7eb5504 | 258 | { |

| nyatla | 68:f7def7eb5504 | 259 | NyLPC_cIsr_enterCritical(); |

| nyatla | 68:f7def7eb5504 | 260 | { |

| nyatla | 68:f7def7eb5504 | 261 | LPC_EMAC->IntEnable = (~(INT_RX_DONE|INT_TX_DONE))&LPC_EMAC->IntEnable; |

| nyatla | 68:f7def7eb5504 | 262 | NVIC_DisableIRQ( ENET_IRQn ); |

| nyatla | 68:f7def7eb5504 | 263 | } |

| nyatla | 68:f7def7eb5504 | 264 | NyLPC_cIsr_exitCritical(); |

| nyatla | 68:f7def7eb5504 | 265 | LPC_EMAC->Command &= ~( CR_RX_EN | CR_TX_EN ); |

| nyatla | 68:f7def7eb5504 | 266 | LPC_EMAC->MAC1 &= ~MAC1_REC_EN; |

| nyatla | 68:f7def7eb5504 | 267 | //ISR割り込み解除 |

| nyatla | 68:f7def7eb5504 | 268 | NyLPC_cIsr_setEnetISR(NULL); |

| nyatla | 68:f7def7eb5504 | 269 | //TXメモリマネージャの終了 |

| nyatla | 68:f7def7eb5504 | 270 | NyLPC_cEthernetMM_finalize(); |

| nyatla | 68:f7def7eb5504 | 271 | return; |

| nyatla | 68:f7def7eb5504 | 272 | } |

| nyatla | 68:f7def7eb5504 | 273 | |

| nyatla | 68:f7def7eb5504 | 274 | static struct NyLPC_TTxBufferHeader* allocTxBuf(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size) |

| nyatla | 68:f7def7eb5504 | 275 | { |

| nyatla | 68:f7def7eb5504 | 276 | return NyLPC_cEthernetMM_alloc(i_hint,o_size); |

| nyatla | 68:f7def7eb5504 | 277 | } |

| nyatla | 68:f7def7eb5504 | 278 | static void releaseTxBuf(struct NyLPC_TTxBufferHeader* i_buf) |

| nyatla | 68:f7def7eb5504 | 279 | { |

| nyatla | 68:f7def7eb5504 | 280 | NyLPC_cEthernetMM_release(i_buf); |

| nyatla | 68:f7def7eb5504 | 281 | } |

| nyatla | 68:f7def7eb5504 | 282 | |

| nyatla | 68:f7def7eb5504 | 283 | |

| nyatla | 68:f7def7eb5504 | 284 | |

| nyatla | 68:f7def7eb5504 | 285 | /******************************************************************************** |

| nyatla | 68:f7def7eb5504 | 286 | * Private functions |

| nyatla | 68:f7def7eb5504 | 287 | *******************************************************************************/ |

| nyatla | 68:f7def7eb5504 | 288 | |

| nyatla | 68:f7def7eb5504 | 289 | /*-----------------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 290 | |

| nyatla | 68:f7def7eb5504 | 291 | /*-----------------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 292 | |

| nyatla | 68:f7def7eb5504 | 293 | static void prvSetupEMACHardware( void ) |

| nyatla | 68:f7def7eb5504 | 294 | { |

| nyatla | 68:f7def7eb5504 | 295 | unsigned short us; |

| nyatla | 68:f7def7eb5504 | 296 | long x; |

| nyatla | 68:f7def7eb5504 | 297 | NyLPC_TBool lDummy; |

| nyatla | 68:f7def7eb5504 | 298 | |

| nyatla | 68:f7def7eb5504 | 299 | /* Power Up the EMAC controller. */ |

| nyatla | 68:f7def7eb5504 | 300 | LPC_SC->PCONP |= 0x40000000; |

| nyatla | 68:f7def7eb5504 | 301 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS); |

| nyatla | 68:f7def7eb5504 | 302 | |

| nyatla | 68:f7def7eb5504 | 303 | /* Enable P1 Ethernet Pins. */ |

| nyatla | 68:f7def7eb5504 | 304 | LPC_PINCON->PINSEL2 = emacPINSEL2_VALUE; |

| nyatla | 68:f7def7eb5504 | 305 | LPC_PINCON->PINSEL3 = ( LPC_PINCON->PINSEL3 & ~0x0000000F ) | 0x00000005; |

| nyatla | 68:f7def7eb5504 | 306 | |

| nyatla | 68:f7def7eb5504 | 307 | /* Reset all EMAC internal modules. */ |

| nyatla | 68:f7def7eb5504 | 308 | LPC_EMAC->MAC1 = MAC1_RES_TX | MAC1_RES_MCS_TX | MAC1_RES_RX | MAC1_RES_MCS_RX | MAC1_SIM_RES | MAC1_SOFT_RES; |

| nyatla | 68:f7def7eb5504 | 309 | LPC_EMAC->Command = CR_REG_RES | CR_TX_RES | CR_RX_RES| CR_PASS_RUNT_FRM; |

| nyatla | 68:f7def7eb5504 | 310 | /* A short delay after reset. */ |

| nyatla | 68:f7def7eb5504 | 311 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS ); |

| nyatla | 68:f7def7eb5504 | 312 | |

| nyatla | 68:f7def7eb5504 | 313 | /* Initialize MAC control registers. */ |

| nyatla | 68:f7def7eb5504 | 314 | LPC_EMAC->MAC1 = MAC1_PASS_ALL; |

| nyatla | 68:f7def7eb5504 | 315 | LPC_EMAC->MAC2 = MAC2_CRC_EN | MAC2_PAD_EN; |

| nyatla | 68:f7def7eb5504 | 316 | LPC_EMAC->MAXF = ETH_MAX_FLEN; |

| nyatla | 68:f7def7eb5504 | 317 | LPC_EMAC->CLRT = CLRT_DEF; |

| nyatla | 68:f7def7eb5504 | 318 | LPC_EMAC->IPGR = IPGR_DEF; |

| nyatla | 68:f7def7eb5504 | 319 | |

| nyatla | 68:f7def7eb5504 | 320 | /*PCLK=18MHz, clock select=6, MDC=18/6=3MHz */ // I don't think so! |

| nyatla | 68:f7def7eb5504 | 321 | /* Enable Reduced MII interface. */ |

| nyatla | 68:f7def7eb5504 | 322 | LPC_EMAC->MCFG = MCFG_CLK_DIV20 | MCFG_RES_MII; |

| nyatla | 68:f7def7eb5504 | 323 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS ); |

| nyatla | 68:f7def7eb5504 | 324 | LPC_EMAC->MCFG = MCFG_CLK_DIV20; |

| nyatla | 68:f7def7eb5504 | 325 | |

| nyatla | 68:f7def7eb5504 | 326 | /* Enable Reduced MII interface. */ |

| nyatla | 68:f7def7eb5504 | 327 | LPC_EMAC->Command = CR_RMII | CR_PASS_RUNT_FRM | CR_PASS_RX_FILT; |

| nyatla | 68:f7def7eb5504 | 328 | |

| nyatla | 68:f7def7eb5504 | 329 | /* Reset Reduced MII Logic. */ |

| nyatla | 68:f7def7eb5504 | 330 | LPC_EMAC->SUPP = SUPP_RES_RMII | SUPP_SPEED; |

| nyatla | 68:f7def7eb5504 | 331 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS ); |

| nyatla | 68:f7def7eb5504 | 332 | LPC_EMAC->SUPP = SUPP_SPEED; |

| nyatla | 68:f7def7eb5504 | 333 | |

| nyatla | 68:f7def7eb5504 | 334 | /* Put the PHY in reset mode */ |

| nyatla | 68:f7def7eb5504 | 335 | prvWritePHY( PHY_REG_BMCR, MCFG_RES_MII ); |

| nyatla | 68:f7def7eb5504 | 336 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5); |

| nyatla | 68:f7def7eb5504 | 337 | |

| nyatla | 68:f7def7eb5504 | 338 | /* Wait for hardware reset to end. */ |

| nyatla | 68:f7def7eb5504 | 339 | for( x = 0; x < 100; x++ ) |

| nyatla | 68:f7def7eb5504 | 340 | { |

| nyatla | 68:f7def7eb5504 | 341 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5 ); |

| nyatla | 68:f7def7eb5504 | 342 | us = prvReadPHY( PHY_REG_BMCR, &lDummy ); |

| nyatla | 68:f7def7eb5504 | 343 | if( !( us & MCFG_RES_MII ) ) |

| nyatla | 68:f7def7eb5504 | 344 | { |

| nyatla | 68:f7def7eb5504 | 345 | /* Reset complete */ |

| nyatla | 68:f7def7eb5504 | 346 | break; |

| nyatla | 68:f7def7eb5504 | 347 | } |

| nyatla | 68:f7def7eb5504 | 348 | } |

| nyatla | 68:f7def7eb5504 | 349 | } |

| nyatla | 68:f7def7eb5504 | 350 | /*-----------------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 351 | |

| nyatla | 68:f7def7eb5504 | 352 | |

| nyatla | 68:f7def7eb5504 | 353 | /*-----------------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 354 | |

| nyatla | 68:f7def7eb5504 | 355 | static NyLPC_TBool prvWritePHY( long lPhyReg, long lValue ) |

| nyatla | 68:f7def7eb5504 | 356 | { |

| nyatla | 68:f7def7eb5504 | 357 | const long lMaxTime = 10; |

| nyatla | 68:f7def7eb5504 | 358 | long x; |

| nyatla | 68:f7def7eb5504 | 359 | |

| nyatla | 68:f7def7eb5504 | 360 | LPC_EMAC->MCMD = 0; |

| nyatla | 68:f7def7eb5504 | 361 | LPC_EMAC->MADR = ETHDEV_PHY_DEF_ADR | lPhyReg; |

| nyatla | 68:f7def7eb5504 | 362 | LPC_EMAC->MWTD = lValue; |

| nyatla | 68:f7def7eb5504 | 363 | |

| nyatla | 68:f7def7eb5504 | 364 | for( x = 0; x < lMaxTime; x++ ) |

| nyatla | 68:f7def7eb5504 | 365 | { |

| nyatla | 68:f7def7eb5504 | 366 | if( ( LPC_EMAC->MIND & MIND_BUSY ) == 0 ) |

| nyatla | 68:f7def7eb5504 | 367 | { |

| nyatla | 68:f7def7eb5504 | 368 | /* Operation has finished. */ |

| nyatla | 68:f7def7eb5504 | 369 | break; |

| nyatla | 68:f7def7eb5504 | 370 | } |

| nyatla | 68:f7def7eb5504 | 371 | |

| nyatla | 68:f7def7eb5504 | 372 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS ); |

| nyatla | 68:f7def7eb5504 | 373 | } |

| nyatla | 68:f7def7eb5504 | 374 | |

| nyatla | 68:f7def7eb5504 | 375 | if( x < lMaxTime ) |

| nyatla | 68:f7def7eb5504 | 376 | { |

| nyatla | 68:f7def7eb5504 | 377 | return NyLPC_TBool_TRUE; |

| nyatla | 68:f7def7eb5504 | 378 | } |

| nyatla | 68:f7def7eb5504 | 379 | else |

| nyatla | 68:f7def7eb5504 | 380 | { |

| nyatla | 68:f7def7eb5504 | 381 | return NyLPC_TBool_FALSE; |

| nyatla | 68:f7def7eb5504 | 382 | } |

| nyatla | 68:f7def7eb5504 | 383 | } |

| nyatla | 68:f7def7eb5504 | 384 | /*-----------------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 385 | |

| nyatla | 68:f7def7eb5504 | 386 | static unsigned short prvReadPHY( unsigned int ucPhyReg, NyLPC_TBool* plStatus ) |

| nyatla | 68:f7def7eb5504 | 387 | { |

| nyatla | 68:f7def7eb5504 | 388 | long x; |

| nyatla | 68:f7def7eb5504 | 389 | const long lMaxTime = 10; |

| nyatla | 68:f7def7eb5504 | 390 | |

| nyatla | 68:f7def7eb5504 | 391 | LPC_EMAC->MCMD = 1; |

| nyatla | 68:f7def7eb5504 | 392 | LPC_EMAC->MADR = ETHDEV_PHY_DEF_ADR | ucPhyReg; |

| nyatla | 68:f7def7eb5504 | 393 | LPC_EMAC->MCMD = MCMD_READ; |

| nyatla | 68:f7def7eb5504 | 394 | |

| nyatla | 68:f7def7eb5504 | 395 | for( x = 0; x < lMaxTime; x++ ) |

| nyatla | 68:f7def7eb5504 | 396 | { |

| nyatla | 68:f7def7eb5504 | 397 | /* Operation has finished. */ |

| nyatla | 68:f7def7eb5504 | 398 | if( ( LPC_EMAC->MIND & MIND_BUSY ) == 0 ) |

| nyatla | 68:f7def7eb5504 | 399 | { |

| nyatla | 68:f7def7eb5504 | 400 | break; |

| nyatla | 68:f7def7eb5504 | 401 | } |

| nyatla | 68:f7def7eb5504 | 402 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS ); |

| nyatla | 68:f7def7eb5504 | 403 | } |

| nyatla | 68:f7def7eb5504 | 404 | |

| nyatla | 68:f7def7eb5504 | 405 | LPC_EMAC->MCMD = 0; |

| nyatla | 68:f7def7eb5504 | 406 | |

| nyatla | 68:f7def7eb5504 | 407 | if( x >= lMaxTime ) |

| nyatla | 68:f7def7eb5504 | 408 | { |

| nyatla | 68:f7def7eb5504 | 409 | *plStatus = NyLPC_TBool_FALSE; |

| nyatla | 68:f7def7eb5504 | 410 | } |

| nyatla | 68:f7def7eb5504 | 411 | |

| nyatla | 68:f7def7eb5504 | 412 | return( LPC_EMAC->MRDD ); |

| nyatla | 68:f7def7eb5504 | 413 | } |

| nyatla | 68:f7def7eb5504 | 414 | /*------------------------------------------------ |

| nyatla | 68:f7def7eb5504 | 415 | * Private function depend on device. |

| nyatla | 68:f7def7eb5504 | 416 | * デバイス依存部分 |

| nyatla | 68:f7def7eb5504 | 417 | ------------------------------------------------*/ |

| nyatla | 68:f7def7eb5504 | 418 | |

| nyatla | 68:f7def7eb5504 | 419 | |

| nyatla | 68:f7def7eb5504 | 420 | /*for mbed |

| nyatla | 68:f7def7eb5504 | 421 | */ |

| nyatla | 68:f7def7eb5504 | 422 | #define emacLINK_ESTABLISHED ( 0x0001 ) |

| nyatla | 68:f7def7eb5504 | 423 | #define emacFULL_DUPLEX_ENABLED ( 0x0004 ) |

| nyatla | 68:f7def7eb5504 | 424 | #define emac10BASE_T_MODE ( 0x0002 ) |

| nyatla | 68:f7def7eb5504 | 425 | |

| nyatla | 68:f7def7eb5504 | 426 | |

| nyatla | 68:f7def7eb5504 | 427 | static void prvConfigurePHY( void ) |

| nyatla | 68:f7def7eb5504 | 428 | { |

| nyatla | 68:f7def7eb5504 | 429 | unsigned short us; |

| nyatla | 68:f7def7eb5504 | 430 | long x; |

| nyatla | 68:f7def7eb5504 | 431 | NyLPC_TBool lDummy; |

| nyatla | 68:f7def7eb5504 | 432 | |

| nyatla | 68:f7def7eb5504 | 433 | /* Auto negotiate the configuration. */ |

| nyatla | 68:f7def7eb5504 | 434 | if( prvWritePHY( PHY_REG_BMCR, PHY_AUTO_NEG ) ) |

| nyatla | 68:f7def7eb5504 | 435 | { |

| nyatla | 68:f7def7eb5504 | 436 | NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5 ); |

| nyatla | 68:f7def7eb5504 | 437 | |

| nyatla | 68:f7def7eb5504 | 438 | for( x = 0; x < 10; x++ ) |

| nyatla | 68:f7def7eb5504 | 439 | { |

| nyatla | 68:f7def7eb5504 | 440 | us = prvReadPHY( PHY_REG_BMSR, &lDummy ); |

| nyatla | 68:f7def7eb5504 | 441 | |

| nyatla | 68:f7def7eb5504 | 442 | if( us & PHY_AUTO_NEG_COMPLETE ) |

| nyatla | 68:f7def7eb5504 | 443 | { |

| nyatla | 68:f7def7eb5504 | 444 | break; |

| nyatla | 68:f7def7eb5504 | 445 | } |

| nyatla | 68:f7def7eb5504 | 446 | |

| nyatla | 68:f7def7eb5504 | 447 | NyLPC_cThread_sleep( emacWAIT_FOR_LINK_TO_ESTABLISH_MS); |

| nyatla | 68:f7def7eb5504 | 448 | } |

| nyatla | 68:f7def7eb5504 | 449 | } |

| nyatla | 68:f7def7eb5504 | 450 | } |

| nyatla | 68:f7def7eb5504 | 451 | |

| nyatla | 68:f7def7eb5504 | 452 | static NyLPC_TBool prvSetupLinkStatus( void ) |

| nyatla | 68:f7def7eb5504 | 453 | { |

| nyatla | 68:f7def7eb5504 | 454 | NyLPC_TBool lReturn = NyLPC_TBool_FALSE; |

| nyatla | 68:f7def7eb5504 | 455 | long x; |

| nyatla | 68:f7def7eb5504 | 456 | unsigned short usLinkStatus; |

| nyatla | 68:f7def7eb5504 | 457 | |

| nyatla | 68:f7def7eb5504 | 458 | /* Wait with timeout for the link to be established. */ |

| nyatla | 68:f7def7eb5504 | 459 | for( x = 0; x < 10; x++ ) |

| nyatla | 68:f7def7eb5504 | 460 | { |

| nyatla | 68:f7def7eb5504 | 461 | usLinkStatus = prvReadPHY( PHY_REG_STS, &lReturn ); |

| nyatla | 68:f7def7eb5504 | 462 | if( usLinkStatus & emacLINK_ESTABLISHED ) |

| nyatla | 68:f7def7eb5504 | 463 | { |

| nyatla | 68:f7def7eb5504 | 464 | /* Link is established. */ |

| nyatla | 68:f7def7eb5504 | 465 | lReturn = NyLPC_TBool_TRUE; |

| nyatla | 68:f7def7eb5504 | 466 | break; |

| nyatla | 68:f7def7eb5504 | 467 | } |

| nyatla | 68:f7def7eb5504 | 468 | |

| nyatla | 68:f7def7eb5504 | 469 | NyLPC_cThread_sleep( emacWAIT_FOR_LINK_TO_ESTABLISH_MS); |

| nyatla | 68:f7def7eb5504 | 470 | } |

| nyatla | 68:f7def7eb5504 | 471 | |

| nyatla | 68:f7def7eb5504 | 472 | if( lReturn == NyLPC_TBool_TRUE ) |

| nyatla | 68:f7def7eb5504 | 473 | { |

| nyatla | 68:f7def7eb5504 | 474 | /* Configure Full/Half Duplex mode. */ |

| nyatla | 68:f7def7eb5504 | 475 | if( usLinkStatus & emacFULL_DUPLEX_ENABLED ) |

| nyatla | 68:f7def7eb5504 | 476 | { |

| nyatla | 68:f7def7eb5504 | 477 | /* Full duplex is enabled. */ |

| nyatla | 68:f7def7eb5504 | 478 | LPC_EMAC->MAC2 |= MAC2_FULL_DUP; |

| nyatla | 68:f7def7eb5504 | 479 | LPC_EMAC->Command |= CR_FULL_DUP; |

| nyatla | 68:f7def7eb5504 | 480 | LPC_EMAC->IPGT = IPGT_FULL_DUP; |

| nyatla | 68:f7def7eb5504 | 481 | } |

| nyatla | 68:f7def7eb5504 | 482 | else |

| nyatla | 68:f7def7eb5504 | 483 | { |

| nyatla | 68:f7def7eb5504 | 484 | /* Half duplex mode. */ |

| nyatla | 68:f7def7eb5504 | 485 | LPC_EMAC->IPGT = IPGT_HALF_DUP; |

| nyatla | 68:f7def7eb5504 | 486 | } |

| nyatla | 68:f7def7eb5504 | 487 | |

| nyatla | 68:f7def7eb5504 | 488 | /* Configure 100MBit/10MBit mode. */ |

| nyatla | 68:f7def7eb5504 | 489 | if( usLinkStatus & emac10BASE_T_MODE ) |

| nyatla | 68:f7def7eb5504 | 490 | { |

| nyatla | 68:f7def7eb5504 | 491 | /* 10MBit mode. */ |

| nyatla | 68:f7def7eb5504 | 492 | LPC_EMAC->SUPP = 0; |

| nyatla | 68:f7def7eb5504 | 493 | } |

| nyatla | 68:f7def7eb5504 | 494 | else |

| nyatla | 68:f7def7eb5504 | 495 | { |

| nyatla | 68:f7def7eb5504 | 496 | /* 100MBit mode. */ |

| nyatla | 68:f7def7eb5504 | 497 | LPC_EMAC->SUPP = SUPP_SPEED; |

| nyatla | 68:f7def7eb5504 | 498 | } |

| nyatla | 68:f7def7eb5504 | 499 | } |

| nyatla | 68:f7def7eb5504 | 500 | |

| nyatla | 68:f7def7eb5504 | 501 | return lReturn; |

| nyatla | 68:f7def7eb5504 | 502 | } |

| nyatla | 68:f7def7eb5504 | 503 | |

| nyatla | 68:f7def7eb5504 | 504 | /** |

| nyatla | 68:f7def7eb5504 | 505 | * EMACからのハンドラ |

| nyatla | 68:f7def7eb5504 | 506 | */ |

| nyatla | 68:f7def7eb5504 | 507 | static void emacIsrHandler(unsigned long i_status) |

| nyatla | 68:f7def7eb5504 | 508 | { |

| nyatla | 68:f7def7eb5504 | 509 | if( i_status & INT_RX_DONE ) |

| nyatla | 68:f7def7eb5504 | 510 | { |

| nyatla | 68:f7def7eb5504 | 511 | _event_handler(_event_param,NyLPC_TiEthernetDevice_EVENT_ON_RX); |

| nyatla | 68:f7def7eb5504 | 512 | } |

| nyatla | 68:f7def7eb5504 | 513 | if( i_status & INT_TX_DONE ) |

| nyatla | 68:f7def7eb5504 | 514 | { |

| nyatla | 68:f7def7eb5504 | 515 | _event_handler(_event_param,NyLPC_TiEthernetDevice_EVENT_ON_TX); |

| nyatla | 68:f7def7eb5504 | 516 | } |

| nyatla | 68:f7def7eb5504 | 517 | } |

| nyatla | 68:f7def7eb5504 | 518 | |

| nyatla | 68:f7def7eb5504 | 519 | #endif |

| nyatla | 68:f7def7eb5504 | 520 |

MiMic Webservice library

MiMic Webservice library