This is Webservice SDK for mbed. LPCXpresso1769/LPC1768/FRDM-K64F/LPC4088

Dependents: MbedFileServer_1768MiniDK2 RedWireBridge IssueDebug_gcc MiMicRemoteMCU-for-Mbed ... more

libMiMic(MiMic library for mbed)は、WebService機能を提供するSDKです。 mbedでWebAPIに対応したネットワークデバイスを簡単に作ることが出来ます。

libMiMicはMiMic projectで開発しています。MiMic projectについてはこちらをご覧ください。 http://nyatla.jp/mimic/wp/

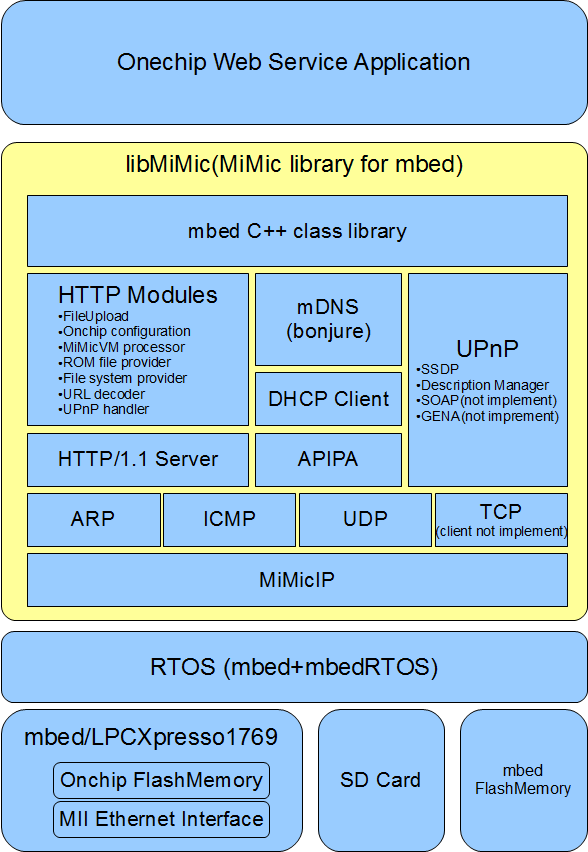

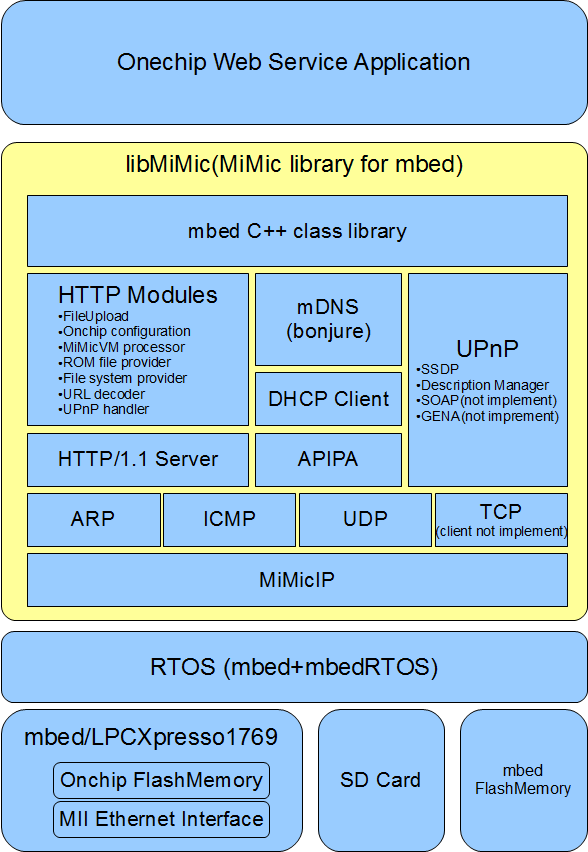

構成

libMiMicはmbedRTOS上で動作し、ユーザアプリケーションにAPIを提供します。コアAPIはC言語で記述されていますが、使用頻度の高いものについてはmbed向けのC++APIが準備されています。

※libMiMicはmbedの標準イーサネットドライバをしようしていません。

標準イーサネットドライバと同時に使用することはできません。

- MiMicIP - IPv4スタックです。レテンシとメモリ消費量を抑えたuipベースのライブラリです。

- ARP/ICMP/UDP/TCP - 基礎的なソケットAPIを提供します。APIは独自です。

- HTTP/1.1 Server - HTTP/1.1に対応したサーバです。マルチセッション・Chunked・持続性接続に対応しています。

- HTTP Modules - HTTP/1.1の機能モジュールです。以下のモジュールがあります。

- ROM file provider - ROMに格納したファイルイメージを公開します。

- File system provider - mbedファイルシステムを公開します。

- Onchip configuration - プログラムフラッシュを利用して設定を保存します。

- MiMicVM processor - RPCリクエスト(MiMicVM)を処理します。

- FileUpload - ファイルアップロードを受け取ります。

- URL decoder - HTTPリクエストを解析します。

- UPnP handler -UPnPメッセージを処理します。

- WebSocket - Websocketサーバです。

- mDNS - マルチキャストDNSサービスです。

- UPnP - UPnP/1.0の機能を提供します。UPnP handlerと協調して動作します。(現在はデバイス探索(SSDP)・デスクリプション(Description)のみ実装してあります。)

- DHCP/APIPA - ゼロコンフィギュレーション用のモジュールです。

- HTTP/1.1 Client

- mbed C++ class library - mbed向けのC++CPIです。C言語のものより簡単です。

対応機種

- mbed(mbed LPC1768)

- LPCXpresso1769

プログラム

Import programMiMicRemoteMCU-for-Mbed

MiMic RemoteMCU for mbed. This program provides MCU control API over REST API. It can control MCU from Javascript,PHP or any HTTP rest client directly. And, The application has self development environment.

Import programMbedFileServer

The program publishes files at local directory and SD filesystem. It is a full-fledged webServer somewhat.

サンプル

Import programMiMicSimpleHttpd

This is a simplest HTTP server made of libMiMic. It will echo back a request path.

Import programUPnPBasicDevice

Simplest UPnP basic device example. This program to run UPnP basic device on the mbed.

Import programWebSocketSample

MiMicSDK Websocket module sample program.

Import programHttpClientSamlpe

A http client sample program.

Import programTcpSocketClientSamlpe

MiMicSDK Tcp client socket sample program.

Import programUdpSocketSamlpe

Udp socket sample program. This program will send back the received packet.

チュートリアル

- HTTPD解説

- UPnPデバイスの作り方

- MiMicRemoteMCUの紹介(pdf)

- MiMicRemoteMCUのマニュアル(pdf)

English

libMiMic(MiMic library for mbed) is SDK which provides Webservice functions. It can be created networking device easily using mbed.

See more MiMic information, See MiMic project website. http://nyatla.jp/mimic/wp/

Structure

libMiMic run on mbed RTOS and provides networking API to user application. This library has C++ class API for the mbed, and low-level C language API.

For WebService general, it can be written in a simple C + + API.

libMiMic does not have the standard Ethernet driver of mbed. It is not possible that will be used with the standard Ethernet driver.

- MiMicIP - IPv4 protocol stack. This is based uip which is reduced memory and latency.

- ARP / ICMP / UDP / TCP - Those are provide basic IP protocols.

- HTTP/1.1 Server - The Http server compatible HTTP/1.1. It supports multi-session, chunked transport, persistent connection.

- HTTP Modules - There are addon-module for HTTP server. The following modules.

- ROM file module - Publish the file images in ROM.

- File system module - Publish thefiles in mbed file system.

- Onchip configuration module - To save the network settings to the program flash via REST.

- MiMicVM module - To handle the (MiMicVM) RPC request.

- FileUpload module - Accept a file via HTTP POST.

- URL dedoce module - A versatility URL decoder.

- UPnP handle module - To handle UPnP messages.

- UPnP - This provides UPnP/1.0 device functions. It works together with UPnP handler.

- Websocket - websocket (version13) server

- mDNS Service - DNS-SD protocol server.

- UPnP - This provides UPnP/1.0 device functions which works with UPnP handler. (You have been implemented (SSDP) ? description only (Description) device search now.) It is a module zero configuration for - DHCP / APIPA. mbed C + + class library - C of mbed for + + is the CPI. It is simple than that of the C language.

- DHCP/APIPA - It support zero-cpnfigulation.

- mbed C++ class library. Almost APIs for Web applications are available.

- HTTP/1.1 Client

Supported target

- mbed(mbed LPC1768)

- LPCXpresso1769

Application

Import programMiMicRemoteMCU-for-Mbed

MiMic RemoteMCU for mbed. This program provides MCU control API over REST API. It can control MCU from Javascript,PHP or any HTTP rest client directly. And, The application has self development environment.

Import programMbedFileServer

The program publishes files at local directory and SD filesystem. It is a full-fledged webServer somewhat.

Sample

Import programMiMicSimpleHttpd

This is a simplest HTTP server made of libMiMic. It will echo back a request path.

Import programUPnPBasicDevice

Simplest UPnP basic device example. This program to run UPnP basic device on the mbed.

Import programWebSocketSample

MiMicSDK Websocket module sample program.

Import programHttpClientSamlpe

A http client sample program.

Import programTcpSocketClientSamlpe

MiMicSDK Tcp client socket sample program.

Import programUdpSocketSamlpe

Udp socket sample program. This program will send back the received packet.

Tutorial

- HTTPD hello world.

- How to make own UPnP device.

- MiMicRemoteMCUの紹介(pdf)

- MiMicRemoteMCUのマニュアル(pdf)

Revision 68:f7def7eb5504, committed 2014-05-22

- Comitter:

- nyatla

- Date:

- Thu May 22 12:59:50 2014 +0000

- Parent:

- 64:258e84040262

- Child:

- 69:8c5f220441f5

- Commit message:

- MiMic-core ?344???;

Changed in this revision

--- a/core/NyLPC_cStr.c Wed Oct 23 04:49:08 2013 +0000

+++ b/core/NyLPC_cStr.c Thu May 22 12:59:50 2014 +0000

@@ -50,7 +50,7 @@

{

NyLPC_TChar* p;

for(p=NyLPC_cStr_str(i_inst);*p!=0;p++){

- *p=(NyLPC_TChar)toupper(*p);

+ *p=(NyLPC_TChar)toupper((int)*p);

}

return;

}

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/EthDev.h Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,43 @@

+/*

+ * @file: EthDev.h

+ * @purpose: Ethernet Device Definitions

+ * @version: V1.10

+ * @date: 24. Feb. 2009

+ *----------------------------------------------------------------------------

+ *

+ * Copyright (C) 2009 ARM Limited. All rights reserved.

+ *

+ * ARM Limited (ARM) is supplying this software for use with Cortex-M3

+ * processor based microcontrollers. This file can be freely distributed

+ * within development tools that are supporting such ARM based processors.

+ *

+ * THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED

+ * OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF

+ * MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE.

+ * ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR

+ * CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

+ *

+ */

+/*

+ * Modified for MiMic by R.Iizuka. 2011.08.27

+ * http://nyatla.jp/mimic

+ */

+

+#ifndef _ETHDEV__H

+#define _ETHDEV__H

+#include "NyLPC_stdlib.h"

+#include "NyLPC_IEthernetDevice.h"

+

+#ifdef __cplusplus

+extern "C" {

+#endif /* __cplusplus */

+

+const struct TiEthernetDevice* getEthernetDevicePnP(void);

+

+

+#ifdef __cplusplus

+}

+#endif /* __cplusplus */

+

+#endif

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/NyLPC_IEthernetDevice.h Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,167 @@

+/*

+ * NyLPC_IEthernetDevice.h

+ *

+ * Created on: 2011/12/06

+ * MiMicのイーサネットドライバインタフェイスを定義する。

+ */

+#ifndef NyLPC_IEthernetDevice_h

+#define NyLPC_IEthernetDevice_h

+#include "NyLPC_stdlib.h"

+#include "NyLPC_uipService.h"

+

+#ifdef __cplusplus

+extern "C" {

+#endif /* __cplusplus */

+

+typedef struct NyLPC_TiEthernetDevice NyLPC_TiEthernetDevice_t;

+

+/**非同期イベントのメッセージタイプ*/

+typedef unsigned int NyLPC_TiEthernetDevice_EVENT;

+/**TXが到達した*/

+#define NyLPC_TiEthernetDevice_EVENT_ON_TX 1

+/**RXが到達した*/

+#define NyLPC_TiEthernetDevice_EVENT_ON_RX 2

+

+

+typedef void (*NyLPC_TiEthernetDevice_onEvent)(void* i_param,NyLPC_TiEthernetDevice_EVENT i_type);

+

+/**

+ * 送信バッフメモリのヘッダ。

+ * この構造体は、TXバッファメモリブロックのヘッダーです。

+ * TXバッファメモリブロックは、この構造体の後ろに、sizeに一致したメモリを連結したもので表現します。

+ * <pre>

+ * buffer=[struct NyLPC_TTxBufferHeader][n]

+ * </pre>

+ */

+struct NyLPC_TTxBufferHeader

+{

+ //メモリブロックの参照カウンタ。

+ NyLPC_TInt8 ref;

+ //送信用にロックしたかを示すフラグ

+ NyLPC_TUInt8 is_lock;

+ //32ビット境界に合わせるためのパディング。

+ NyLPC_TUInt16 padding;

+};

+

+

+

+/**

+ * 受信キューの先頭にあるデータを返す。

+ * 関数は、受信キューのポインタを操作しない。続けて読み出したとしても、同じポインターを返す。

+ * 次のデータを得るには、nextRxEthFrameを呼び出す。

+ * #制限として、返却したポインタの内容は、一時的に書き換え可としてください。(この制限は将来削除します。)

+ * @return

+ * 成功した場合、受信データを格納したバッファポインタ。返却値は、nextRxEthFrameをコールするまで有効である。

+ * 存在しない場合NULL。

+ */

+#define NyLPC_iEthernetDevice_getRxEthFrame(i,p) (i)->getRxEthFrame(p)

+typedef void* (*NyLPC_TiEthernetDevice_getRxEthFrame)(unsigned short* o_len_of_data);

+

+

+

+/**

+ * getRxEthFrameで得たメモリを破棄して、次のRXデータを準備する。

+ * getRxEthFrameで返したメモリの内容の有効期間はここで終了するので注意すること。

+ */

+#define NyLPC_iEthernetDevice_nextRxEthFrame(i) (i)->nextRxEthFrame()

+typedef void (*NyLPC_TiEthernetDevice_nextRxEthFrame)(void);

+

+

+/**

+ * 送信バッファを得る。

+ * 関数は、i_hintで示されるサイズのメモリブロックを確保しようとするが、実際にはそれよりも小さいことがある。

+ * @param i_hint

+ * 確保してほしいメモリサイズ

+ * @param o_size

+ * 実際に割り当てたメモリのサイズ

+ * @return

+ * 割り当てたメモリブロックのヘッダ。

+ */

+#define NyLPC_iEthernetDevice_allocTxBuf(i,h,s) (i)->allocTxBuf((h),(s))

+typedef struct NyLPC_TTxBufferHeader* (*NyLPC_TiEthernetDevice_allocTxBuf)(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size);

+

+

+/**

+ * alloc_TxBufで得た送信バッファを開放する。

+ * 関数は、メモリブロックの参照カウンタを1減算する。

+ */

+#define NyLPC_iEthernetDevice_releaseTxBuf(i,b) (i)->releaseTxBuf(b)

+typedef void (*NyLPC_TiEthernetDevice_releaseTxBuf)(struct NyLPC_TTxBufferHeader* i_buf);

+

+

+

+/**

+ * イーサネットパケット構造体i_bufの内容を送信する。

+ * @param i_buf

+ * allocTxBufで得たメモリか、初期化したNyLPC_TTxBufferHeaderメモリブロックを指定する。

+ * 送信が終わるまでの間、メモリを開放してはならない。

+ * #外部で確保したメモリについては、利用不能なケースがあるかもしれない。現在のMiMicでは、使用できることを前提としている。

+ * @oaram i_size

+ * i_bufの後ろに連結されているデータメモリの長さ

+ */

+#define NyLPC_iEthernetDevice_sendTxEthFrame(i,b,s) (i)->sendTxEthFrame((b),(s))

+typedef void (*NyLPC_TiEthernetDevice_sendTxEthFrame)(struct NyLPC_TTxBufferHeader* i_buf,unsigned short i_size);

+

+

+/**

+ * この関数は、送信キューの状態を進行させるタイミングを与える。

+ * 外部関数が、送信キューにセットしたパケットの送信待ちをするときに呼び出す。

+ */

+#define NyLPC_iEthernetDevice_processTx(i) (i)->processTx()

+typedef void (*NyLPC_TiEthernetDevice_processTx)(void);

+

+

+

+/**

+ * この関数は、ドライバを開始します。

+ * @param i_eth_addr

+ * イーサネットアドレス

+ * @param i_handler

+ * 通知ハンドラ

+ * @param i_param

+ * 通知ハンドラに渡るパラメータ

+ */

+#define NyLPC_iEthernetDevice_start(i,a,h,p) (i)->start((a),(h),(p))

+typedef NyLPC_TBool(*NyLPC_TiEthernetDevice_start)(const struct NyLPC_TEthAddr* i_eth_addr,NyLPC_TiEthernetDevice_onEvent i_handler,void* i_param);

+

+

+/**

+ * この関数はドライバを停止します。

+ */

+#define NyLPC_iEthernetDevice_stop(i) (i)->stop()

+typedef void(*NyLPC_TiEthernetDevice_stop)(void);

+

+

+/**

+ * デバイス名を返します。

+ */

+#define NyLPC_iEthernetDevice_getDevicName(i) ((i)->_device_name)

+

+/**

+ * イーサネットデバイスのアクセスインターフェイス

+ * イーサネットデバイスの管理するメモリブロック、ペリフェラル制御のインタフェイスを提供する。

+ *

+ */

+struct TiEthernetDevice

+{

+ /** NyLPC_iEthernetDevice_getDevicNameで返却する値*/

+ const char* _device_name;//pointer to device name.

+ NyLPC_TiEthernetDevice_start start;

+ NyLPC_TiEthernetDevice_stop stop;

+ NyLPC_TiEthernetDevice_getRxEthFrame getRxEthFrame;

+ NyLPC_TiEthernetDevice_nextRxEthFrame nextRxEthFrame; //nextRxEthFrame;

+ NyLPC_TiEthernetDevice_allocTxBuf allocTxBuf;

+ NyLPC_TiEthernetDevice_releaseTxBuf releaseTxBuf;

+ NyLPC_TiEthernetDevice_sendTxEthFrame sendTxEthFrame;

+ NyLPC_TiEthernetDevice_processTx processTx;

+};

+

+

+

+

+#ifdef __cplusplus

+}

+#endif /* __cplusplus */

+

+#endif

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/NyLPC_cEthernetMM.c Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,177 @@

+#include "NyLPC_cEthernetMM.h"

+/**

+ * メモリブロックの数

+ */

+#define NUM_OF_MAX_BUF 3

+#define NUM_OF_512_BUF 3

+#define NUM_OF_256_BUF 4

+#define NUM_OF_128_BUF 16

+

+/**

+ * FULLサイズのEthernetFrame送信メモリのサイズ。

+ * ここで最大送信サイズを制限する。

+ * 通常は1460+20+20+14=1514バイト

+ */

+#define MAX_TX_ETHERNET_FRAME_SIZE 1514

+

+/**

+ * TXメモリブロックの配置

+ * 9246バイト

+ */

+struct TTxMemoryBlock

+{

+ struct{

+ struct NyLPC_TTxBufferHeader h;

+ NyLPC_TUInt8 b[MAX_TX_ETHERNET_FRAME_SIZE];

+ }buf_max[NUM_OF_MAX_BUF];//(4+MAX_TX_ETHERNET_FRAME_SIZE(1514))*3=? default=4554

+ struct{

+ struct NyLPC_TTxBufferHeader h;

+ NyLPC_TUInt8 b[512];

+ }buf_512[NUM_OF_512_BUF];//(4+512)*3=1548

+ struct{

+ struct NyLPC_TTxBufferHeader h;

+ NyLPC_TUInt8 b[256];

+ }buf_256[NUM_OF_256_BUF];//(4+256)*4=1560

+ struct{

+ struct NyLPC_TTxBufferHeader h;

+ NyLPC_TUInt8 b[128];

+ }buf_128[NUM_OF_128_BUF];//(4+128)*16=1584

+};

+/**

+ * メモリブロックの配置

+ */

+static struct TTxMemoryBlock* _mem_addr;

+

+

+

+/**

+ * デバック用。使用中のTxブロックの数を返す。

+ */

+int NyLPC_cEthernetMM_dbg_getNumofUsedTx(void)

+{

+ int x;

+ NyLPC_TUInt8 r1,r2,r3,r4;

+ r1=r2=r3=r4=0;

+ for(x=0;x<NUM_OF_MAX_BUF;x++){

+ if(_mem_addr->buf_max[x].h.is_lock || _mem_addr->buf_max[x].h.ref>0){

+ r1++;

+ continue;

+ }

+ }

+ for(x=0;x<NUM_OF_512_BUF;x++){

+ if(_mem_addr->buf_512[x].h.is_lock || _mem_addr->buf_512[x].h.ref>0){

+ r2++;

+ continue;

+ }

+ }

+ for(x=0;x<NUM_OF_256_BUF;x++){

+ if(_mem_addr->buf_256[x].h.is_lock || _mem_addr->buf_256[x].h.ref>0){

+ r3++;

+ continue;

+ }

+ }

+ for(x=0;x<NUM_OF_128_BUF;x++){

+ if(_mem_addr->buf_128[x].h.is_lock || _mem_addr->buf_128[x].h.ref>0){

+ r4++;

+ continue;

+ }

+ }

+ return r1+r2+r3+r4;

+}

+

+

+void NyLPC_cEthernetMM_initialize(void* i_memblock_addr)

+{

+ int x;

+ _mem_addr=i_memblock_addr;

+ //TXバッファを初期化

+ for(x=0;x<NUM_OF_MAX_BUF;x++){

+ _mem_addr->buf_max[x].h.is_lock=NyLPC_TUInt8_FALSE;

+ _mem_addr->buf_max[x].h.ref=0;

+ }

+ for(x=0;x<NUM_OF_512_BUF;x++){

+ _mem_addr->buf_512[x].h.is_lock=NyLPC_TUInt8_FALSE;

+ _mem_addr->buf_512[x].h.ref=0;

+ }

+ for(x=0;x<NUM_OF_256_BUF;x++){

+ _mem_addr->buf_256[x].h.is_lock=NyLPC_TUInt8_FALSE;

+ _mem_addr->buf_256[x].h.ref=0;

+ }

+ for(x=0;x<NUM_OF_128_BUF;x++){

+ _mem_addr->buf_128[x].h.is_lock=NyLPC_TUInt8_FALSE;

+ _mem_addr->buf_128[x].h.ref=0;

+ }

+}

+

+/**

+ * 空のTxバッファのポインタを返します。

+ */

+struct NyLPC_TTxBufferHeader* NyLPC_cEthernetMM_alloc(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size)

+{

+ int buf_type;

+ int i;

+ //ヒントから、割り当てるメモリブロックを決定

+ if(i_hint<=128){

+ buf_type=0;

+ }else if(i_hint<=256){

+ buf_type=1;

+ }else if(i_hint<=512){

+ buf_type=2;

+ }else{

+ buf_type=3;

+ }

+ switch(buf_type){

+ case 3:

+ for(i=0;i<NUM_OF_MAX_BUF;i++){

+ //未参照かつ送信中でないもの。

+ if(_mem_addr->buf_max[i].h.ref>0 || _mem_addr->buf_max[i].h.is_lock){

+ continue;

+ }

+ _mem_addr->buf_max[i].h.ref++;

+ *o_size=MAX_TX_ETHERNET_FRAME_SIZE;

+ return &(_mem_addr->buf_max[i].h);

+ }

+ case 2:

+ for(i=0;i<NUM_OF_512_BUF;i++){

+ //未参照かつ送信中でないもの。

+ if(_mem_addr->buf_512[i].h.ref>0 || _mem_addr->buf_512[i].h.is_lock){

+ continue;

+ }

+ *o_size=512;

+ _mem_addr->buf_512[i].h.ref++;

+ return &(_mem_addr->buf_512[i].h);

+ }

+ case 1:

+ for(i=0;i<NUM_OF_256_BUF;i++){

+ //未参照かつ送信中でないもの。

+ if(_mem_addr->buf_256[i].h.ref>0 || (_mem_addr->buf_256[i].h.is_lock)){

+ continue;

+ }

+ *o_size=256;

+ _mem_addr->buf_256[i].h.ref++;

+ return &(_mem_addr->buf_256[i].h);

+ }

+ default:

+ for(i=0;i<NUM_OF_128_BUF;i++){

+ //未参照かつ送信中でないもの。

+ if(_mem_addr->buf_128[i].h.ref>0 || (_mem_addr->buf_128[i].h.is_lock)){

+ continue;

+ }

+ *o_size=128;

+ _mem_addr->buf_128[i].h.ref++;

+ return &(_mem_addr->buf_128[i].h);

+ }

+ }

+ return NULL;

+}

+

+

+void NyLPC_cEthernetMM_release(struct NyLPC_TTxBufferHeader* i_buf)

+{

+ //参照カウンタを1減算

+ NyLPC_Assert(i_buf->ref>0);

+ i_buf->ref--;

+ return;

+}

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/NyLPC_cEthernetMM.h Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,68 @@

+/*********************************************************************************

+ * PROJECT: MiMic

+ * --------------------------------------------------------------------------------

+ *

+ * This file is part of MiMic

+ * Copyright (C)2011 Ryo Iizuka

+ *

+ * MiMic is free software: you can redistribute it and/or modify

+ * it under the terms of the GNU Lesser General Public License as published

+ * by the Free Software Foundation, either version 3 of the License, or

+ * (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU Lesser General Public License

+ * along with this program. If not, see <http://www.gnu.org/licenses/>.

+ *

+ * For further information please contact.

+ * http://nyatla.jp/

+ * <airmail(at)ebony.plala.or.jp> or <nyatla(at)nyatla.jp>

+ *

+ *********************************************************************************/

+

+#ifndef NyLPC_cEthernetMM_protected_h

+#define NyLPC_cEthernetMM_protected_h

+

+#include "NyLPC_stdlib.h"

+#include "NyLPC_IEthernetDevice.h"

+

+#ifdef __cplusplus

+extern "C" {

+#endif /* __cplusplus */

+

+/**

+ * @file

+ * このファイルは、イーサネットメモリマネージャクラスを定義します。

+ */

+

+int NyLPC_cEthernetMM_dbg_getNumofUsedTx(void);

+

+/**

+ * メモリブロックを初期化してメモリマネージャを構築します。

+ * メモリサイズはsizeof(struct TTxMemoryBlock)以上である必要があります。

+ */

+void NyLPC_cEthernetMM_initialize(void* i_memblock_addr);

+#define NyLPC_cEthernetMM_finalize(i)

+/**

+ * メモリを割り当てます。

+ * @return

+ * 割り当て不能な場合はNULLが帰ります。

+ * @bug

+ * 戻り値、メモリブロックヘッダ不要では?

+ */

+struct NyLPC_TTxBufferHeader* NyLPC_cEthernetMM_alloc(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size);

+/**

+ * NyLPC_EthernetMM_allocで得たメモリを解放します。

+ */

+void NyLPC_cEthernetMM_release(struct NyLPC_TTxBufferHeader* i_buf);

+

+#ifdef __cplusplus

+}

+#endif /* __cplusplus */

+

+#endif

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/lpc17xx/EthDev.c Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,25 @@

+#include "NyLPC_config.h"

+#if NyLPC_MCU==NyLPC_MCU_LPC17xx

+

+#include "../EthDev.h"

+#include "EtherDev_DP83848C_protected.h"

+#include "EtherDev_LAN8720_protected.h"

+

+

+

+const struct TiEthernetDevice* getEthernetDevicePnP(void)

+{

+ const struct TiEthernetDevice* ret;

+ if(EthDev_LAN8720_getInterface(&ret)){

+ return ret;

+ }

+ if(EthDev_DP83848C_getInterface(&ret)){

+ return ret;

+ }

+ return NULL;

+}

+

+

+#endif

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/lpc17xx/EthDev_LPC17xx.c Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,196 @@

+/*

+ * EthDev_LPC1769.c

+ *

+ * Created on: 2011/12/07

+ * Author: nyatla

+ */

+#include "NyLPC_config.h"

+#if NyLPC_MCU==NyLPC_MCU_LPC17xx

+#include "LPC17xx.h"

+#include "EthDev_LPC17xx.h"

+#include "NyLPC_os.h"

+/* If no buffers are available, then wait this long before looking again.... */

+#define emacBUFFER_WAIT_DELAY_MS 3

+#define emacBUFFER_WAIT_EMPTY_DELAY_MS 10

+//--------------------------------------------------

+// common function.

+//--------------------------------------------------

+

+

+

+/**

+ * 送信デスクリプタを準備します。

+ */

+void EthDev_LPC17xx_prevTxDescriptor(void)

+{

+ long x;

+ //デスクリプタの設定

+ for( x = 0; x < NUM_TX_FRAG; x++ )

+ {

+ TX_DESC_PACKET( x ) = ( unsigned long ) NULL;

+ TX_DESC_CTRL( x ) = 0;

+ TX_STAT_INFO( x ) = 0;

+ }

+ /* Set LPC_EMAC Transmit Descriptor Registers. */

+ LPC_EMAC->TxDescriptor = TX_DESC_BASE;

+ LPC_EMAC->TxStatus = TX_STAT_BASE;

+ LPC_EMAC->TxDescriptorNumber = NUM_TX_FRAG - 1;

+}

+

+

+/**

+ * 送信中のイーサフレームを処理する機会を与えて、送信キューが空くまで待ちます。

+ * LPC1769の場合は、非同期に更新したディスクリプタの内容から、送信メモリのフラグを更新します。

+ * @return

+ * 次に書き込むことが出来る送信キュー。

+ */

+static NyLPC_TUInt32 waitForTxEthFrameEmpty(void)

+{

+ NyLPC_TUInt32 IndexNext;

+ struct NyLPC_TTxBufferHeader *b;

+ void* p;

+ NyLPC_TUInt32 i;

+

+ //送信キューの決定

+ IndexNext = (LPC_EMAC->TxProduceIndex + 1)%NUM_TX_FRAG;

+

+ //送信キューフルが解除されるまで待ち

+ while(IndexNext == LPC_EMAC->TxConsumeIndex)

+ {

+ //

+ NyLPC_cThread_sleep(emacBUFFER_WAIT_EMPTY_DELAY_MS);

+ }

+

+ //(TxProduceIndex+1)→TxConsumeIndexにあるデータのsentフラグを消去

+ for(i=IndexNext;i!=LPC_EMAC->TxConsumeIndex;i=(i+1)%NUM_TX_FRAG)

+ {

+ p=(void*)TX_DESC_PACKET(i);

+ if(p!=NULL){

+ b=((struct NyLPC_TTxBufferHeader*)p)-1;

+ b->is_lock=NyLPC_TUInt8_FALSE;

+ TX_DESC_PACKET(i)=0;

+ }

+ }

+ p=(void*)TX_DESC_PACKET(i);

+ if(p!=NULL){

+ b=((struct NyLPC_TTxBufferHeader*)p)-1;

+ b->is_lock=NyLPC_TUInt8_FALSE;

+ TX_DESC_PACKET(i)=0;

+ }

+ return IndexNext;

+}

+

+void EthDev_LPC17xx_processTx(void)

+{

+ waitForTxEthFrameEmpty();

+}

+

+/**

+ * Ethernetパケットを送信します。

+ * allocTxBufで得たバッファか、NyLPC_TTxBufferHeaderのペイロード部分を指定すること。

+ * <p>関数仕様</p>

+ * この関数は、i_bufが

+ * </div>

+ */

+void EthDev_LPC17xx_sendTxEthFrame(struct NyLPC_TTxBufferHeader* i_buf,unsigned short i_size)

+{

+ NyLPC_TUInt32 IndexNext,Index;

+

+ //サイズ0なら送信の必要なし

+ if(i_size == 0)

+ {

+ return;

+ }

+ //送信デスクリプタの反映

+ IndexNext =waitForTxEthFrameEmpty();

+

+ //送信対象のメモリブロックを送信中に設定。

+// b=(i_buf+1);

+ //送信中のメモリブロックなら無視

+ if(i_buf->is_lock){

+ return;

+ }

+ //送信中にセット

+ i_buf->is_lock=NyLPC_TUInt8_TRUE;

+

+ //送信データのセット

+ Index = LPC_EMAC->TxProduceIndex;

+ if (i_size > ETH_FRAG_SIZE){

+ i_size = ETH_FRAG_SIZE;

+ }

+

+ //送信処理

+ TX_DESC_PACKET( Index ) = ( unsigned long )(i_buf+1);

+ //See UM10360.pdf Table 181. Transmit descriptor control word

+ TX_DESC_CTRL( Index ) = ((i_size-1) | TCTRL_LAST | TCTRL_INT );

+ LPC_EMAC->TxProduceIndex = IndexNext;

+ return;

+}

+

+/***********************************************************************

+ * RXバッファ

+ ***********************************************************************/

+

+void EthDev_LPC17xx_prevRxDescriptor(void)

+{

+ int x;

+ //デスクリプタの設定

+ for( x = 0; x < NUM_RX_FRAG; x++ )

+ {

+ /* Allocate the next Ethernet buffer to this descriptor. */

+ RX_DESC_PACKET(x) = ETH_BUF(x);

+ RX_DESC_CTRL(x) = RCTRL_INT | ( ETH_FRAG_SIZE - 1 );

+ RX_STAT_INFO(x) = 0;

+ RX_STAT_HASHCRC(x) = 0;

+ }

+

+ /* Set LPC_EMAC Receive Descriptor Registers. */

+ LPC_EMAC->RxDescriptor = RX_DESC_BASE;

+ LPC_EMAC->RxStatus = RX_STAT_BASE;

+ LPC_EMAC->RxDescriptorNumber = NUM_RX_FRAG - 1;

+

+}

+

+

+/**

+ * 受信キューの先頭にあるRXフレームのポインタを返します。

+ * 関数は、受信キューのポインタを操作しません。続けて読み出したとしても、同じポインターを返します。

+ * 制限として、返却したポインタの内容は、一時的に書き換え可としてください。(この制限は将来削除します。)

+ * @return

+ * 成功した場合、受信データを格納したバッファポインターです。

+ * 次回nextRxEthFrameを呼び出すまで有効です。

+ */

+void* EthDev_LPC17xx_getRxEthFrame(unsigned short* o_len_of_data)

+{

+

+ if( LPC_EMAC->RxProduceIndex != LPC_EMAC->RxConsumeIndex )

+ {

+ //受信データを返却する。

+ *o_len_of_data = (unsigned short)(( RX_STAT_INFO( LPC_EMAC->RxConsumeIndex ) & RINFO_SIZE ) - 3);

+ return ( unsigned char * ) RX_DESC_PACKET( LPC_EMAC->RxConsumeIndex );

+ }

+ return NULL;

+}

+

+

+/**

+ * 受信キューを進行します。

+ */

+void EthDev_LPC17xx_nextRxEthFrame(void)

+{

+ long lIndex;

+ if( LPC_EMAC->RxProduceIndex != LPC_EMAC->RxConsumeIndex )

+ {

+ //キューすすめる。

+ lIndex = LPC_EMAC->RxConsumeIndex;

+ lIndex++;

+ if( lIndex >= NUM_RX_FRAG )

+ {

+ lIndex = 0;

+ }

+ LPC_EMAC->RxConsumeIndex = lIndex;

+ }

+}

+#endif

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/lpc17xx/EthDev_LPC17xx.h Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,338 @@

+/*

+ * @file: EthDev_LPC17xx.h

+ * @purpose: Ethernet Device Definitions for NXP LPC17xx

+ * @version: V0.01

+ * @date: 14. May 2009

+ *----------------------------------------------------------------------------

+ *

+ * Copyright (C) 2009 ARM Limited. All rights reserved.

+ *

+ * ARM Limited (ARM) is supplying this software for use with Cortex-M3

+ * processor based microcontrollers. This file can be freely distributed

+ * within development tools that are supporting such ARM based processors.

+ *

+ * THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED

+ * OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF

+ * MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE.

+ * ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR

+ * CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

+ *

+ */

+/*

+ * Modified by Kenji Arai August 29th, 2010 for XpressoLPC1768 LAN

+ *

+ * Changed LPC17xx.h then convert all "EMAC" to "LPC_EMAC"

+ *

+ * September 5th, 2010

+ */

+/*

+ * Modified for MiMic by R.Iizuka. 2011.08.27

+ * http://nyatla.jp/mimic

+ */

+#ifndef __ETHDEV_LPC17XX_H

+#define __ETHDEV_LPC17XX_H

+

+#include <stdint.h>

+#include "NyLPC_stdlib.h"

+#include "../NyLPC_IEthernetDevice.h"

+

+#ifdef __cplusplus

+extern "C" {

+#endif /* __cplusplus */

+

+/* EMAC Memory Buffer configuration for 16K Ethernet RAM. */

+#define NUM_RX_FRAG 3 /* Num.of RX Fragments. */

+#define NUM_TX_FRAG 16 /* Num.of TX Fragments. */

+#define ETH_FRAG_SIZE 1536 /* Packet Fragment size 1536 Bytes */

+

+#define ETH_MAX_FLEN 1536 /* Max. Ethernet Frame Size */

+

+typedef struct { /* RX Descriptor struct */

+ uint32_t Packet;

+ uint32_t Ctrl;

+} RX_DESC_TypeDef;

+

+typedef struct { /* RX Status struct */

+ uint32_t Info;

+ uint32_t HashCRC;

+} RX_STAT_TypeDef;

+

+typedef struct { /* TX Descriptor struct */

+ uint32_t Packet;

+ uint32_t Ctrl;

+} TX_DESC_TypeDef;

+

+typedef struct { /* TX Status struct */

+ uint32_t Info;

+} TX_STAT_TypeDef;

+

+

+/* EMAC variables located in AHB SRAM bank 1*/

+#define AHB_SRAM_BANK1_BASE 0x2007c000UL

+#define RX_DESC_BASE (AHB_SRAM_BANK1_BASE )

+#define RX_STAT_BASE (RX_DESC_BASE + NUM_RX_FRAG*(2*4)) /* 2 * uint32_t, see RX_DESC_TypeDef */

+#define TX_DESC_BASE (RX_STAT_BASE + NUM_RX_FRAG*(2*4)) /* 2 * uint32_t, see RX_STAT_TypeDef */

+#define TX_STAT_BASE (TX_DESC_BASE + NUM_TX_FRAG*(2*4)) /* 2 * uint32_t, see TX_DESC_TypeDef */

+#define ETH_BUF_BASE (TX_STAT_BASE + NUM_TX_FRAG*(1*4)) /* 1 * uint32_t, see TX_STAT_TypeDef */

+

+/**

+ * 消費メモリ量は、

+ * descriptor = NUM_RX_FRAG*16+NUM_TX_FRAG*12.

+ * EthnetBuf=ETH_FRAG_SIZE*NUM_RX_FRAG

+ */

+

+/* RX and TX descriptor and status definitions. */

+#define RX_DESC_PACKET(i) (*(unsigned int *)(RX_DESC_BASE + 8*i))

+#define RX_DESC_CTRL(i) (*(unsigned int *)(RX_DESC_BASE+4 + 8*i))

+#define RX_STAT_INFO(i) (*(unsigned int *)(RX_STAT_BASE + 8*i))

+#define RX_STAT_HASHCRC(i) (*(unsigned int *)(RX_STAT_BASE+4 + 8*i))

+#define TX_DESC_PACKET(i) (*(unsigned int *)(TX_DESC_BASE + 8*i))

+#define TX_DESC_CTRL(i) (*(unsigned int *)(TX_DESC_BASE+4 + 8*i))

+#define TX_STAT_INFO(i) (*(unsigned int *)(TX_STAT_BASE + 4*i))

+#define ETH_BUF(i) ( ETH_BUF_BASE + ETH_FRAG_SIZE*i )

+#define ETH_NUM_BUFFERS ( NUM_TX_FRAG + NUM_RX_FRAG + 1 ) /* There are in fact 2 more buffers than descriptors as the two Tx descriptors use the same buffer to speed up the uip Tx. */

+

+

+/* MAC Configuration Register 1 */

+#define MAC1_REC_EN 0x00000001 /* Receive Enable */

+#define MAC1_PASS_ALL 0x00000002 /* Pass All Receive Frames */

+#define MAC1_RX_FLOWC 0x00000004 /* RX Flow Control */

+#define MAC1_TX_FLOWC 0x00000008 /* TX Flow Control */

+#define MAC1_LOOPB 0x00000010 /* Loop Back Mode */

+#define MAC1_RES_TX 0x00000100 /* Reset TX Logic */

+#define MAC1_RES_MCS_TX 0x00000200 /* Reset MAC TX Control Sublayer */

+#define MAC1_RES_RX 0x00000400 /* Reset RX Logic */

+#define MAC1_RES_MCS_RX 0x00000800 /* Reset MAC RX Control Sublayer */

+#define MAC1_SIM_RES 0x00004000 /* Simulation Reset */

+#define MAC1_SOFT_RES 0x00008000 /* Soft Reset MAC */

+

+/* MAC Configuration Register 2 */

+#define MAC2_FULL_DUP 0x00000001 /* Full Duplex Mode */

+#define MAC2_FRM_LEN_CHK 0x00000002 /* Frame Length Checking */

+#define MAC2_HUGE_FRM_EN 0x00000004 /* Huge Frame Enable */

+#define MAC2_DLY_CRC 0x00000008 /* Delayed CRC Mode */

+#define MAC2_CRC_EN 0x00000010 /* Append CRC to every Frame */

+#define MAC2_PAD_EN 0x00000020 /* Pad all Short Frames */

+#define MAC2_VLAN_PAD_EN 0x00000040 /* VLAN Pad Enable */

+#define MAC2_ADET_PAD_EN 0x00000080 /* Auto Detect Pad Enable */

+#define MAC2_PPREAM_ENF 0x00000100 /* Pure Preamble Enforcement */

+#define MAC2_LPREAM_ENF 0x00000200 /* Long Preamble Enforcement */

+#define MAC2_NO_BACKOFF 0x00001000 /* No Backoff Algorithm */

+#define MAC2_BACK_PRESSURE 0x00002000 /* Backoff Presurre / No Backoff */

+#define MAC2_EXCESS_DEF 0x00004000 /* Excess Defer */

+

+/* Back-to-Back Inter-Packet-Gap Register */

+#define IPGT_FULL_DUP 0x00000015 /* Recommended value for Full Duplex */

+#define IPGT_HALF_DUP 0x00000012 /* Recommended value for Half Duplex */

+

+/* Non Back-to-Back Inter-Packet-Gap Register */

+#define IPGR_DEF 0x00000012 /* Recommended value */

+

+/* Collision Window/Retry Register */

+#define CLRT_DEF 0x0000370F /* Default value */

+

+/* PHY Support Register */

+#define SUPP_SPEED 0x00000100 /* Reduced MII Logic Current Speed */

+#define SUPP_RES_RMII 0x00000800 /* Reset Reduced MII Logic */

+

+/* Test Register */

+#define TEST_SHCUT_PQUANTA 0x00000001 /* Shortcut Pause Quanta */

+#define TEST_TST_PAUSE 0x00000002 /* Test Pause */

+#define TEST_TST_BACKP 0x00000004 /* Test Back Pressure */

+

+/* MII Management Configuration Register */

+#define MCFG_SCAN_INC 0x00000001 /* Scan Increment PHY Address */

+#define MCFG_SUPP_PREAM 0x00000002 /* Suppress Preamble */

+#define MCFG_CLK_SEL 0x0000003C /* Clock Select Mask */

+#define MCFG_RES_MII 0x00008000 /* Reset MII Management Hardware */

+

+#define MCFG_CLK_DIV4 0x00000000 /* MDC = hclk / 4 */

+#define MCFG_CLK_DIV6 0x00000008 /* MDC = hclk / 6 */

+#define MCFG_CLK_DIV8 0x0000000C /* MDC = hclk / 8 */

+#define MCFG_CLK_DIV10 0x00000010 /* MDC = hclk / 10 */

+#define MCFG_CLK_DIV14 0x00000014 /* MDC = hclk / 14 */

+#define MCFG_CLK_DIV20 0x00000018 /* MDC = hclk / 20 */

+#define MCFG_CLK_DIV28 0x0000001C /* MDC = hclk / 28 */

+

+/* MII Management Command Register */

+#define MCMD_READ 0x00000001 /* MII Read */

+#define MCMD_SCAN 0x00000002 /* MII Scan continuously */

+

+#define MII_WR_TOUT 0x00050000 /* MII Write timeout count */

+#define MII_RD_TOUT 0x00050000 /* MII Read timeout count */

+

+/* MII Management Address Register */

+#define MADR_REG_ADR 0x0000001F /* MII Register Address Mask */

+#define MADR_PHY_ADR 0x00001F00 /* PHY Address Mask */

+

+/* MII Management Indicators Register */

+#define MIND_BUSY 0x00000001 /* MII is Busy */

+#define MIND_SCAN 0x00000002 /* MII Scanning in Progress */

+#define MIND_NOT_VAL 0x00000004 /* MII Read Data not valid */

+#define MIND_MII_LINK_FAIL 0x00000008 /* MII Link Failed */

+

+/* Command Register */

+#define CR_RX_EN 0x00000001 /* Enable Receive */

+#define CR_TX_EN 0x00000002 /* Enable Transmit */

+#define CR_REG_RES 0x00000008 /* Reset Host Registers */

+#define CR_TX_RES 0x00000010 /* Reset Transmit Datapath */

+#define CR_RX_RES 0x00000020 /* Reset Receive Datapath */

+#define CR_PASS_RUNT_FRM 0x00000040 /* Pass Runt Frames */

+#define CR_PASS_RX_FILT 0x00000080 /* Pass RX Filter */

+#define CR_TX_FLOW_CTRL 0x00000100 /* TX Flow Control */

+#define CR_RMII 0x00000200 /* Reduced MII Interface */

+#define CR_FULL_DUP 0x00000400 /* Full Duplex */

+

+/* Status Register */

+#define SR_RX_EN 0x00000001 /* Enable Receive */

+#define SR_TX_EN 0x00000002 /* Enable Transmit */

+

+/* Transmit Status Vector 0 Register */

+#define TSV0_CRC_ERR 0x00000001 /* CRC error */

+#define TSV0_LEN_CHKERR 0x00000002 /* Length Check Error */

+#define TSV0_LEN_OUTRNG 0x00000004 /* Length Out of Range */

+#define TSV0_DONE 0x00000008 /* Tramsmission Completed */

+#define TSV0_MCAST 0x00000010 /* Multicast Destination */

+#define TSV0_BCAST 0x00000020 /* Broadcast Destination */

+#define TSV0_PKT_DEFER 0x00000040 /* Packet Deferred */

+#define TSV0_EXC_DEFER 0x00000080 /* Excessive Packet Deferral */

+#define TSV0_EXC_COLL 0x00000100 /* Excessive Collision */

+#define TSV0_LATE_COLL 0x00000200 /* Late Collision Occured */

+#define TSV0_GIANT 0x00000400 /* Giant Frame */

+#define TSV0_UNDERRUN 0x00000800 /* Buffer Underrun */

+#define TSV0_BYTES 0x0FFFF000 /* Total Bytes Transferred */

+#define TSV0_CTRL_FRAME 0x10000000 /* Control Frame */

+#define TSV0_PAUSE 0x20000000 /* Pause Frame */

+#define TSV0_BACK_PRESS 0x40000000 /* Backpressure Method Applied */

+#define TSV0_VLAN 0x80000000 /* VLAN Frame */

+

+/* Transmit Status Vector 1 Register */

+#define TSV1_BYTE_CNT 0x0000FFFF /* Transmit Byte Count */

+#define TSV1_COLL_CNT 0x000F0000 /* Transmit Collision Count */

+

+/* Receive Status Vector Register */

+#define RSV_BYTE_CNT 0x0000FFFF /* Receive Byte Count */

+#define RSV_PKT_IGNORED 0x00010000 /* Packet Previously Ignored */

+#define RSV_RXDV_SEEN 0x00020000 /* RXDV Event Previously Seen */

+#define RSV_CARR_SEEN 0x00040000 /* Carrier Event Previously Seen */

+#define RSV_REC_CODEV 0x00080000 /* Receive Code Violation */

+#define RSV_CRC_ERR 0x00100000 /* CRC Error */

+#define RSV_LEN_CHKERR 0x00200000 /* Length Check Error */

+#define RSV_LEN_OUTRNG 0x00400000 /* Length Out of Range */

+#define RSV_REC_OK 0x00800000 /* Frame Received OK */

+#define RSV_MCAST 0x01000000 /* Multicast Frame */

+#define RSV_BCAST 0x02000000 /* Broadcast Frame */

+#define RSV_DRIB_NIBB 0x04000000 /* Dribble Nibble */

+#define RSV_CTRL_FRAME 0x08000000 /* Control Frame */

+#define RSV_PAUSE 0x10000000 /* Pause Frame */

+#define RSV_UNSUPP_OPC 0x20000000 /* Unsupported Opcode */

+#define RSV_VLAN 0x40000000 /* VLAN Frame */

+

+/* Flow Control Counter Register */

+#define FCC_MIRR_CNT 0x0000FFFF /* Mirror Counter */

+#define FCC_PAUSE_TIM 0xFFFF0000 /* Pause Timer */

+

+/* Flow Control Status Register */

+#define FCS_MIRR_CNT 0x0000FFFF /* Mirror Counter Current */

+

+/* Receive Filter Control Register */

+#define RFC_UCAST_EN 0x00000001 /* Accept Unicast Frames Enable */

+#define RFC_BCAST_EN 0x00000002 /* Accept Broadcast Frames Enable */

+#define RFC_MCAST_EN 0x00000004 /* Accept Multicast Frames Enable */

+#define RFC_UCAST_HASH_EN 0x00000008 /* Accept Unicast Hash Filter Frames */

+#define RFC_MCAST_HASH_EN 0x00000010 /* Accept Multicast Hash Filter Fram.*/

+#define RFC_PERFECT_EN 0x00000020 /* Accept Perfect Match Enable */

+#define RFC_MAGP_WOL_EN 0x00001000 /* Magic Packet Filter WoL Enable */

+#define RFC_PFILT_WOL_EN 0x00002000 /* Perfect Filter WoL Enable */

+

+/* Receive Filter WoL Status/Clear Registers */

+#define WOL_UCAST 0x00000001 /* Unicast Frame caused WoL */

+#define WOL_BCAST 0x00000002 /* Broadcast Frame caused WoL */

+#define WOL_MCAST 0x00000004 /* Multicast Frame caused WoL */

+#define WOL_UCAST_HASH 0x00000008 /* Unicast Hash Filter Frame WoL */

+#define WOL_MCAST_HASH 0x00000010 /* Multicast Hash Filter Frame WoL */

+#define WOL_PERFECT 0x00000020 /* Perfect Filter WoL */

+#define WOL_RX_FILTER 0x00000080 /* RX Filter caused WoL */

+#define WOL_MAG_PACKET 0x00000100 /* Magic Packet Filter caused WoL */

+

+/* Interrupt Status/Enable/Clear/Set Registers */

+#define INT_RX_OVERRUN 0x00000001 /* Overrun Error in RX Queue */

+#define INT_RX_ERR 0x00000002 /* Receive Error */

+#define INT_RX_FIN 0x00000004 /* RX Finished Process Descriptors */

+#define INT_RX_DONE 0x00000008 /* Receive Done */

+#define INT_TX_UNDERRUN 0x00000010 /* Transmit Underrun */

+#define INT_TX_ERR 0x00000020 /* Transmit Error */

+#define INT_TX_FIN 0x00000040 /* TX Finished Process Descriptors */

+#define INT_TX_DONE 0x00000080 /* Transmit Done */

+#define INT_SOFT_INT 0x00001000 /* Software Triggered Interrupt */

+#define INT_WAKEUP 0x00002000 /* Wakeup Event Interrupt */

+

+/* Power Down Register */

+#define PD_POWER_DOWN 0x80000000 /* Power Down MAC */

+

+/* RX Descriptor Control Word */

+#define RCTRL_SIZE 0x000007FF /* Buffer size mask */

+#define RCTRL_INT 0x80000000 /* Generate RxDone Interrupt */

+

+/* RX Status Hash CRC Word */

+#define RHASH_SA 0x000001FF /* Hash CRC for Source Address */

+#define RHASH_DA 0x001FF000 /* Hash CRC for Destination Address */

+

+/* RX Status Information Word */

+#define RINFO_SIZE 0x000007FF /* Data size in bytes */

+#define RINFO_CTRL_FRAME 0x00040000 /* Control Frame */

+#define RINFO_VLAN 0x00080000 /* VLAN Frame */

+#define RINFO_FAIL_FILT 0x00100000 /* RX Filter Failed */

+#define RINFO_MCAST 0x00200000 /* Multicast Frame */

+#define RINFO_BCAST 0x00400000 /* Broadcast Frame */

+#define RINFO_CRC_ERR 0x00800000 /* CRC Error in Frame */

+#define RINFO_SYM_ERR 0x01000000 /* Symbol Error from PHY */

+#define RINFO_LEN_ERR 0x02000000 /* Length Error */

+#define RINFO_RANGE_ERR 0x04000000 /* Range Error (exceeded max. size) */

+#define RINFO_ALIGN_ERR 0x08000000 /* Alignment Error */

+#define RINFO_OVERRUN 0x10000000 /* Receive overrun */

+#define RINFO_NO_DESCR 0x20000000 /* No new Descriptor available */

+#define RINFO_LAST_FLAG 0x40000000 /* Last Fragment in Frame */

+#define RINFO_ERR 0x80000000 /* Error Occured (OR of all errors) */

+

+#define RINFO_ERR_MASK (RINFO_FAIL_FILT | RINFO_CRC_ERR | RINFO_SYM_ERR | \

+ RINFO_LEN_ERR | RINFO_ALIGN_ERR | RINFO_OVERRUN)

+

+/* TX Descriptor Control Word */

+#define TCTRL_SIZE 0x000007FF /* Size of data buffer in bytes */

+#define TCTRL_OVERRIDE 0x04000000 /* Override Default MAC Registers */

+#define TCTRL_HUGE 0x08000000 /* Enable Huge Frame */

+#define TCTRL_PAD 0x10000000 /* Pad short Frames to 64 bytes */

+#define TCTRL_CRC 0x20000000 /* Append a hardware CRC to Frame */

+#define TCTRL_LAST 0x40000000 /* Last Descriptor for TX Frame */

+#define TCTRL_INT 0x80000000 /* Generate TxDone Interrupt */

+

+/* TX Status Information Word */

+#define TINFO_COL_CNT 0x01E00000 /* Collision Count */

+#define TINFO_DEFER 0x02000000 /* Packet Deferred (not an error) */

+#define TINFO_EXCESS_DEF 0x04000000 /* Excessive Deferral */

+#define TINFO_EXCESS_COL 0x08000000 /* Excessive Collision */

+#define TINFO_LATE_COL 0x10000000 /* Late Collision Occured */

+#define TINFO_UNDERRUN 0x20000000 /* Transmit Underrun */

+#define TINFO_NO_DESCR 0x40000000 /* No new Descriptor available */

+#define TINFO_ERR 0x80000000 /* Error Occured (OR of all errors) */

+

+

+

+void EthDev_LPC17xx_prevTxDescriptor(void);

+void EthDev_LPC17xx_prevRxDescriptor(void);

+void EthDev_LPC17xx_processTx(void);

+void EthDev_LPC17xx_sendTxEthFrame(struct NyLPC_TTxBufferHeader* i_buf,unsigned short i_size);

+

+void* EthDev_LPC17xx_getRxEthFrame(unsigned short* o_len_of_data);

+void EthDev_LPC17xx_nextRxEthFrame(void);

+

+#ifdef __cplusplus

+}

+#endif /* __cplusplus */

+

+#endif

+/*----------------------------------------------------------------------------

+ * end of file

+ *---------------------------------------------------------------------------*/

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/lpc17xx/EtherDev_DP83848C.c Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,520 @@

+/*

+ FreeRTOS V7.0.0 - Copyright (C) 2011 Real Time Engineers Ltd.

+

+

+ ***************************************************************************

+ * *

+ * FreeRTOS tutorial books are available in pdf and paperback. *

+ * Complete, revised, and edited pdf reference manuals are also *

+ * available. *

+ * *

+ * Purchasing FreeRTOS documentation will not only help you, by *

+ * ensuring you get running as quickly as possible and with an *

+ * in-depth knowledge of how to use FreeRTOS, it will also help *

+ * the FreeRTOS project to continue with its mission of providing *

+ * professional grade, cross platform, de facto standard solutions *

+ * for microcontrollers - completely free of charge! *

+ * *

+ * >>> See http://www.FreeRTOS.org/Documentation for details. <<< *

+ * *

+ * Thank you for using FreeRTOS, and thank you for your support! *

+ * *

+ ***************************************************************************

+

+

+ This file is part of the FreeRTOS distribution.

+

+ FreeRTOS is free software; you can redistribute it and/or modify it under

+ the terms of the GNU General Public License (version 2) as published by the

+ Free Software Foundation AND MODIFIED BY the FreeRTOS exception.

+ >>>NOTE<<< The modification to the GPL is included to allow you to

+ distribute a combined work that includes FreeRTOS without being obliged to

+ provide the source code for proprietary components outside of the FreeRTOS

+ kernel. FreeRTOS is distributed in the hope that it will be useful, but

+ WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY

+ or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for

+ more details. You should have received a copy of the GNU General Public

+ License and the FreeRTOS license exception along with FreeRTOS; if not it

+ can be viewed here: http://www.freertos.org/a00114.html and also obtained

+ by writing to Richard Barry, contact details for whom are available on the

+ FreeRTOS WEB site.

+

+ 1 tab == 4 spaces!

+

+ http://www.FreeRTOS.org - Documentation, latest information, license and

+ contact details.

+

+ http://www.SafeRTOS.com - A version that is certified for use in safety

+ critical systems.

+

+ http://www.OpenRTOS.com - Commercial support, development, porting,

+ licensing and training services.

+*/

+

+/* Originally adapted from file written by Andreas Dannenberg. Supplied with permission. */

+/*

+ * Modified for MiMic by R.Iizuka. 2011.08.27

+ * http://nyatla.jp/mimic

+ */

+

+#include "NyLPC_config.h"

+#if NyLPC_MCU==NyLPC_MCU_LPC17xx

+

+

+/* Kernel includes. */

+#include "../NyLPC_cEthernetMM.h"

+#include "EtherDev_DP83848C_protected.h"

+#include "LPC17xx.h"

+#include "NyLPC_os.h"

+

+

+#define DP83848C_ID 0x20005C90 /* PHY Identifier */

+

+/* DP83848C PHY Registers */

+#define PHY_REG_BMCR 0x00 /* Basic Mode Control Register */

+#define PHY_REG_BMSR 0x01 /* Basic Mode Status Register */

+#define PHY_REG_IDR1 0x02 /* PHY Identifier 1 */

+#define PHY_REG_IDR2 0x03 /* PHY Identifier 2 */

+#define PHY_REG_ANAR 0x04 /* Auto-Negotiation Advertisement */

+#define PHY_REG_ANLPAR 0x05 /* Auto-Neg. Link Partner Abitily */

+#define PHY_REG_ANER 0x06 /* Auto-Neg. Expansion Register */

+#define PHY_REG_ANNPTR 0x07 /* Auto-Neg. Next Page TX */

+

+/* PHY Extended Registers */

+#define PHY_REG_STS 0x10 /* Status Register */

+#define PHY_REG_MICR 0x11 /* MII Interrupt Control Register */

+#define PHY_REG_MISR 0x12 /* MII Interrupt Status Register */

+#define PHY_REG_FCSCR 0x14 /* False Carrier Sense Counter */

+#define PHY_REG_RECR 0x15 /* Receive Error Counter */

+#define PHY_REG_PCSR 0x16 /* PCS Sublayer Config. and Status */

+#define PHY_REG_RBR 0x17 /* RMII and Bypass Register */

+#define PHY_REG_LEDCR 0x18 /* LED Direct Control Register */

+#define PHY_REG_PHYCR 0x19 /* PHY Control Register */

+#define PHY_REG_10BTSCR 0x1A /* 10Base-T Status/Control Register */

+#define PHY_REG_CDCTRL1 0x1B /* CD Test Control and BIST Extens. */

+#define PHY_REG_EDCR 0x1D /* Energy Detect Control Register */

+

+#define PHY_FULLD_100M 0x2100 /* Full Duplex 100Mbit */

+#define PHY_HALFD_100M 0x2000 /* Half Duplex 100Mbit */

+#define PHY_FULLD_10M 0x0100 /* Full Duplex 10Mbit */

+#define PHY_HALFD_10M 0x0000 /* Half Duplex 10MBit */

+#define PHY_AUTO_NEG 0x3000 /* Select Auto Negotiation */

+#define PHY_AUTO_NEG_COMPLETE 0x0020 /* Auto negotiation have finished. */

+#define ETHDEV_PHY_DEF_ADR 0x0100 /* Default PHY device address */

+

+

+#ifndef configEMAC_INTERRUPT_PRIORITY

+ #define configEMAC_INTERRUPT_PRIORITY 5

+#endif

+

+/* Time to wait between each inspection of the link status. */

+#define emacWAIT_FOR_LINK_TO_ESTABLISH_MS 500

+

+/* Short delay used in several places during the initialisation process. */

+#define emacSHORT_DELAY_MS 10

+

+/* Hardware specific bit definitions. */

+#define emacPINSEL2_VALUE ( 0x50150105 )

+

+/* If no buffers are available, then wait this long before looking again.... */

+#define emacBUFFER_WAIT_DELAY_MS 3

+#define emacBUFFER_WAIT_EMPTY_MS 10

+

+/* ...and don't look more than this many times. */

+#define emacBUFFER_WAIT_ATTEMPTS ( 30 )

+

+/* Index to the Tx descriptor that is always used first for every Tx. The second

+descriptor is then used to re-send in order to speed up the uIP Tx process. */

+#define emacTX_DESC_INDEX ( 0 )

+

+/*-----------------------------------------------------------*/

+

+/* Setup the IO and peripherals required for Ethernet communication.*/

+static void prvSetupEMACHardware( void );

+/* Control the auto negotiate process.*/

+static void prvConfigurePHY( void );

+/*

+ * Wait for a link to be established, then setup the PHY according to the link

+ * parameters.

+ */

+static NyLPC_TBool prvSetupLinkStatus( void );

+/*

+ * Send lValue to the lPhyReg within the PHY.

+ */

+static NyLPC_TBool prvWritePHY( long lPhyReg, long lValue );

+/*

+ * Read a value from ucPhyReg within the PHY. *plStatus will be set to

+ * pdFALSE if there is an error.

+ */

+static unsigned short prvReadPHY( unsigned int ucPhyReg, long *plStatus );

+

+

+

+static NyLPC_TBool start(const struct NyLPC_TEthAddr* i_eth_addr,NyLPC_TiEthernetDevice_onEvent i_handler,void* i_param);

+static void stop(void);

+static struct NyLPC_TTxBufferHeader* allocTxBuf(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size);

+static void releaseTxBuf(struct NyLPC_TTxBufferHeader* i_buf);

+/*-----------------------------------------------------------*/

+#define ETH_TX_BUF_BASE (void*)(ETH_BUF_BASE+ETH_FRAG_SIZE*NUM_RX_FRAG)

+

+

+const static struct TiEthernetDevice _interface=

+{

+ "DP83848C",

+ start,

+ stop,

+ EthDev_LPC17xx_getRxEthFrame,

+ EthDev_LPC17xx_nextRxEthFrame,

+ allocTxBuf,

+ releaseTxBuf,

+ EthDev_LPC17xx_sendTxEthFrame,

+ EthDev_LPC17xx_processTx

+};

+

+static void* _event_param;

+static NyLPC_TiEthernetDevice_onEvent _event_handler;

+

+/** EMAC ISRハンドラ*/

+static void emacIsrHandler(unsigned long i_status);

+

+/*

+ * EthernetDeviceのファクトリー関数

+ */

+

+NyLPC_TBool EthDev_DP83848C_getInterface(

+ const struct TiEthernetDevice** o_dev)

+{

+ unsigned long ulID1, ulID2;

+ NyLPC_TBool lReturn = NyLPC_TBool_TRUE;

+ //Reset MCU Interface. and wait for reset.

+ prvSetupEMACHardware();

+ //Check peripheral name

+ ulID1 = prvReadPHY( PHY_REG_IDR1, &lReturn );

+ ulID2 = prvReadPHY( PHY_REG_IDR2, &lReturn );

+ if( ( (ulID1 << 16UL ) | ( ulID2 & 0xFFF0UL ) ) != DP83848C_ID)

+ {

+ return NyLPC_TBool_FALSE;

+ }

+ *o_dev=&_interface;

+ LPC_EMAC->TxProduceIndex = 0;

+ LPC_EMAC->RxConsumeIndex = 0;

+ return NyLPC_TBool_TRUE;

+}

+

+

+static NyLPC_TBool start(const struct NyLPC_TEthAddr* i_eth_addr,NyLPC_TiEthernetDevice_onEvent i_handler,void* i_param)

+{

+ _event_handler=i_handler;

+ _event_param=i_param;

+ NyLPC_cIsr_setEnetISR(emacIsrHandler);

+ /* Set the Ethernet MAC Address registers */

+ LPC_EMAC->SA0 = (((uint32_t)(i_eth_addr->addr[0])) << 8 ) | i_eth_addr->addr[1];

+ LPC_EMAC->SA1 = (((uint32_t)(i_eth_addr->addr[2])) << 8 ) | i_eth_addr->addr[3];

+ LPC_EMAC->SA2 = (((uint32_t)(i_eth_addr->addr[4])) << 8 ) | i_eth_addr->addr[5];

+

+ //TXメモリマネージャの準備

+ NyLPC_cEthernetMM_initialize(ETH_TX_BUF_BASE);

+

+ /* Initialize Tx and Rx DMA Descriptors */

+ EthDev_LPC17xx_prevRxDescriptor();

+ EthDev_LPC17xx_prevTxDescriptor();

+

+ /* Setup the PHY. */

+ prvConfigurePHY();

+

+ //wait for Link up...

+ while(!prvSetupLinkStatus())

+ {

+ NyLPC_cThread_sleep(100);

+ }

+

+ /* Receive Broadcast and Perfect Match Packets */

+ LPC_EMAC->RxFilterCtrl = RFC_BCAST_EN | RFC_PERFECT_EN | RFC_MCAST_EN;

+

+ //Ethernetの割込み開始設定

+ NyLPC_cIsr_enterCritical();

+ {

+ /* Reset all interrupts */

+ LPC_EMAC->IntClear = 0xffff;

+ LPC_EMAC->IntEnable = ( INT_RX_DONE | INT_TX_DONE );

+

+ /* Enable receive and transmit mode of MAC Ethernet core */

+ LPC_EMAC->Command |= ( CR_RX_EN | CR_TX_EN );

+ LPC_EMAC->MAC1 |= MAC1_REC_EN;

+

+ /* Set the interrupt priority to the max permissible to cause some

+ interrupt nesting. */

+ NVIC_SetPriority( ENET_IRQn, configEMAC_INTERRUPT_PRIORITY );

+

+ /* Enable the interrupt. */

+ NVIC_EnableIRQ( ENET_IRQn );

+ }

+ NyLPC_cIsr_exitCritical();

+

+ return NyLPC_TBool_TRUE;

+

+}

+static void stop(void)

+{

+ NyLPC_cIsr_enterCritical();

+ {

+ LPC_EMAC->IntEnable = (~(INT_RX_DONE|INT_TX_DONE))&LPC_EMAC->IntEnable;

+ NVIC_DisableIRQ( ENET_IRQn );

+ }

+ NyLPC_cIsr_exitCritical();

+ LPC_EMAC->Command &= ~( CR_RX_EN | CR_TX_EN );

+ LPC_EMAC->MAC1 &= ~MAC1_REC_EN;

+ //ISR割り込み解除

+ NyLPC_cIsr_setEnetISR(NULL);

+ //TXメモリマネージャの終了

+ NyLPC_cEthernetMM_finalize();

+ return;

+}

+

+static struct NyLPC_TTxBufferHeader* allocTxBuf(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size)

+{

+ return NyLPC_cEthernetMM_alloc(i_hint,o_size);

+}

+static void releaseTxBuf(struct NyLPC_TTxBufferHeader* i_buf)

+{

+ NyLPC_cEthernetMM_release(i_buf);

+}

+

+

+

+/********************************************************************************

+ * Private functions

+ *******************************************************************************/

+

+/*-----------------------------------------------------------*/

+

+/*-----------------------------------------------------------*/

+

+static void prvSetupEMACHardware( void )

+{

+ unsigned short us;

+ long x;

+ NyLPC_TBool lDummy;

+

+ /* Power Up the EMAC controller. */

+ LPC_SC->PCONP |= 0x40000000;

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS);

+

+ /* Enable P1 Ethernet Pins. */

+ LPC_PINCON->PINSEL2 = emacPINSEL2_VALUE;

+ LPC_PINCON->PINSEL3 = ( LPC_PINCON->PINSEL3 & ~0x0000000F ) | 0x00000005;

+

+ /* Reset all EMAC internal modules. */

+ LPC_EMAC->MAC1 = MAC1_RES_TX | MAC1_RES_MCS_TX | MAC1_RES_RX | MAC1_RES_MCS_RX | MAC1_SIM_RES | MAC1_SOFT_RES;

+ LPC_EMAC->Command = CR_REG_RES | CR_TX_RES | CR_RX_RES| CR_PASS_RUNT_FRM;

+ /* A short delay after reset. */

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS );

+

+ /* Initialize MAC control registers. */

+ LPC_EMAC->MAC1 = MAC1_PASS_ALL;

+ LPC_EMAC->MAC2 = MAC2_CRC_EN | MAC2_PAD_EN;

+ LPC_EMAC->MAXF = ETH_MAX_FLEN;

+ LPC_EMAC->CLRT = CLRT_DEF;

+ LPC_EMAC->IPGR = IPGR_DEF;

+

+ /*PCLK=18MHz, clock select=6, MDC=18/6=3MHz */ // I don't think so!

+ /* Enable Reduced MII interface. */

+ LPC_EMAC->MCFG = MCFG_CLK_DIV20 | MCFG_RES_MII;

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS );

+ LPC_EMAC->MCFG = MCFG_CLK_DIV20;

+

+ /* Enable Reduced MII interface. */

+ LPC_EMAC->Command = CR_RMII | CR_PASS_RUNT_FRM | CR_PASS_RX_FILT;

+

+ /* Reset Reduced MII Logic. */

+ LPC_EMAC->SUPP = SUPP_RES_RMII | SUPP_SPEED;

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS );

+ LPC_EMAC->SUPP = SUPP_SPEED;

+

+ /* Put the PHY in reset mode */

+ prvWritePHY( PHY_REG_BMCR, MCFG_RES_MII );

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5);

+

+ /* Wait for hardware reset to end. */

+ for( x = 0; x < 100; x++ )

+ {

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5 );

+ us = prvReadPHY( PHY_REG_BMCR, &lDummy );

+ if( !( us & MCFG_RES_MII ) )

+ {

+ /* Reset complete */

+ break;

+ }

+ }

+}

+/*-----------------------------------------------------------*/

+

+

+/*-----------------------------------------------------------*/

+

+static NyLPC_TBool prvWritePHY( long lPhyReg, long lValue )

+{

+ const long lMaxTime = 10;

+ long x;

+

+ LPC_EMAC->MCMD = 0;

+ LPC_EMAC->MADR = ETHDEV_PHY_DEF_ADR | lPhyReg;

+ LPC_EMAC->MWTD = lValue;

+

+ for( x = 0; x < lMaxTime; x++ )

+ {

+ if( ( LPC_EMAC->MIND & MIND_BUSY ) == 0 )

+ {

+ /* Operation has finished. */

+ break;

+ }

+

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS );

+ }

+

+ if( x < lMaxTime )

+ {

+ return NyLPC_TBool_TRUE;

+ }

+ else

+ {

+ return NyLPC_TBool_FALSE;

+ }

+}

+/*-----------------------------------------------------------*/

+

+static unsigned short prvReadPHY( unsigned int ucPhyReg, NyLPC_TBool* plStatus )

+{

+ long x;

+ const long lMaxTime = 10;

+

+ LPC_EMAC->MCMD = 1;

+ LPC_EMAC->MADR = ETHDEV_PHY_DEF_ADR | ucPhyReg;

+ LPC_EMAC->MCMD = MCMD_READ;

+

+ for( x = 0; x < lMaxTime; x++ )

+ {

+ /* Operation has finished. */

+ if( ( LPC_EMAC->MIND & MIND_BUSY ) == 0 )

+ {

+ break;

+ }

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS );

+ }

+

+ LPC_EMAC->MCMD = 0;

+

+ if( x >= lMaxTime )

+ {

+ *plStatus = NyLPC_TBool_FALSE;

+ }

+

+ return( LPC_EMAC->MRDD );

+}

+/*------------------------------------------------

+ * Private function depend on device.

+ * デバイス依存部分

+ ------------------------------------------------*/

+

+

+/*for mbed

+ */

+#define emacLINK_ESTABLISHED ( 0x0001 )

+#define emacFULL_DUPLEX_ENABLED ( 0x0004 )

+#define emac10BASE_T_MODE ( 0x0002 )

+

+

+static void prvConfigurePHY( void )

+{

+ unsigned short us;

+ long x;

+ NyLPC_TBool lDummy;

+

+ /* Auto negotiate the configuration. */

+ if( prvWritePHY( PHY_REG_BMCR, PHY_AUTO_NEG ) )

+ {

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5 );

+

+ for( x = 0; x < 10; x++ )

+ {

+ us = prvReadPHY( PHY_REG_BMSR, &lDummy );

+

+ if( us & PHY_AUTO_NEG_COMPLETE )

+ {

+ break;

+ }

+

+ NyLPC_cThread_sleep( emacWAIT_FOR_LINK_TO_ESTABLISH_MS);

+ }

+ }

+}

+

+static NyLPC_TBool prvSetupLinkStatus( void )

+{

+ NyLPC_TBool lReturn = NyLPC_TBool_FALSE;

+ long x;

+ unsigned short usLinkStatus;

+

+ /* Wait with timeout for the link to be established. */

+ for( x = 0; x < 10; x++ )

+ {

+ usLinkStatus = prvReadPHY( PHY_REG_STS, &lReturn );

+ if( usLinkStatus & emacLINK_ESTABLISHED )

+ {

+ /* Link is established. */

+ lReturn = NyLPC_TBool_TRUE;

+ break;

+ }

+

+ NyLPC_cThread_sleep( emacWAIT_FOR_LINK_TO_ESTABLISH_MS);

+ }

+

+ if( lReturn == NyLPC_TBool_TRUE )

+ {

+ /* Configure Full/Half Duplex mode. */

+ if( usLinkStatus & emacFULL_DUPLEX_ENABLED )

+ {

+ /* Full duplex is enabled. */

+ LPC_EMAC->MAC2 |= MAC2_FULL_DUP;

+ LPC_EMAC->Command |= CR_FULL_DUP;

+ LPC_EMAC->IPGT = IPGT_FULL_DUP;

+ }

+ else

+ {

+ /* Half duplex mode. */

+ LPC_EMAC->IPGT = IPGT_HALF_DUP;

+ }

+

+ /* Configure 100MBit/10MBit mode. */

+ if( usLinkStatus & emac10BASE_T_MODE )

+ {

+ /* 10MBit mode. */

+ LPC_EMAC->SUPP = 0;

+ }

+ else

+ {

+ /* 100MBit mode. */

+ LPC_EMAC->SUPP = SUPP_SPEED;

+ }

+ }

+

+ return lReturn;

+}

+

+/**

+ * EMACからのハンドラ

+ */

+static void emacIsrHandler(unsigned long i_status)

+{

+ if( i_status & INT_RX_DONE )

+ {

+ _event_handler(_event_param,NyLPC_TiEthernetDevice_EVENT_ON_RX);

+ }

+ if( i_status & INT_TX_DONE )

+ {

+ _event_handler(_event_param,NyLPC_TiEthernetDevice_EVENT_ON_TX);

+ }

+}

+

+#endif

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/lpc17xx/EtherDev_DP83848C_protected.h Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,25 @@

+/*

+ * This is part of EthDev_LPC17xx.h

+ */

+

+#ifndef EtherDev_DP83848C_protected_h

+#define EtherDev_DP83848C_protected_h

+

+

+#include "NyLPC_stdlib.h"

+#include "../NyLPC_IEthernetDevice.h"

+#include "EthDev_LPC17xx.h"

+

+#ifdef __cplusplus

+extern "C" {

+#endif /* __cplusplus */

+

+NyLPC_TBool EthDev_DP83848C_getInterface(

+ const struct TiEthernetDevice** o_dev);

+

+#ifdef __cplusplus

+}

+#endif /* __cplusplus */

+

+#endif

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/core/driver/ethernet/lpc17xx/EtherDev_LAN8720.c Thu May 22 12:59:50 2014 +0000

@@ -0,0 +1,504 @@

+/*

+ FreeRTOS V7.0.0 - Copyright (C) 2011 Real Time Engineers Ltd.

+

+

+ ***************************************************************************

+ * *

+ * FreeRTOS tutorial books are available in pdf and paperback. *

+ * Complete, revised, and edited pdf reference manuals are also *

+ * available. *

+ * *

+ * Purchasing FreeRTOS documentation will not only help you, by *

+ * ensuring you get running as quickly as possible and with an *

+ * in-depth knowledge of how to use FreeRTOS, it will also help *

+ * the FreeRTOS project to continue with its mission of providing *

+ * professional grade, cross platform, de facto standard solutions *

+ * for microcontrollers - completely free of charge! *

+ * *

+ * >>> See http://www.FreeRTOS.org/Documentation for details. <<< *

+ * *

+ * Thank you for using FreeRTOS, and thank you for your support! *

+ * *

+ ***************************************************************************

+

+

+ This file is part of the FreeRTOS distribution.

+

+ FreeRTOS is free software; you can redistribute it and/or modify it under

+ the terms of the GNU General Public License (version 2) as published by the

+ Free Software Foundation AND MODIFIED BY the FreeRTOS exception.

+ >>>NOTE<<< The modification to the GPL is included to allow you to

+ distribute a combined work that includes FreeRTOS without being obliged to

+ provide the source code for proprietary components outside of the FreeRTOS

+ kernel. FreeRTOS is distributed in the hope that it will be useful, but

+ WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY

+ or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for

+ more details. You should have received a copy of the GNU General Public

+ License and the FreeRTOS license exception along with FreeRTOS; if not it

+ can be viewed here: http://www.freertos.org/a00114.html and also obtained

+ by writing to Richard Barry, contact details for whom are available on the

+ FreeRTOS WEB site.

+

+ 1 tab == 4 spaces!

+

+ http://www.FreeRTOS.org - Documentation, latest information, license and

+ contact details.

+

+ http://www.SafeRTOS.com - A version that is certified for use in safety

+ critical systems.

+

+ http://www.OpenRTOS.com - Commercial support, development, porting,

+ licensing and training services.

+*/

+

+/* Originally adapted from file written by Andreas Dannenberg. Supplied with permission. */

+/*

+ * Modified for MiMic by R.Iizuka. 2011.08.27

+ * http://nyatla.jp/mimic

+ */

+

+

+#include "NyLPC_config.h"

+#if NyLPC_MCU==NyLPC_MCU_LPC17xx

+#include "EtherDev_LAN8720_protected.h"

+#include "../NyLPC_cEthernetMM.h"

+#include "LPC17xx.h"

+#include "NyLPC_os.h"

+

+#define LAN8720_ID 0x0007C0F0 /* PHY Identifier */

+

+/* LAN8720 PHY Registers */

+#define PHY_REG_BMCR 0x00 /* Basic Mode Control Register */

+#define PHY_REG_BMSR 0x01 /* Basic Mode Status Register */

+#define PHY_REG_IDR1 0x02 /* PHY Identifier 1 */

+#define PHY_REG_IDR2 0x03 /* PHY Identifier 2 */

+#define PHY_REG_ANAR 0x04 /* Auto-Negotiation Advertisement */

+#define PHY_REG_ANLPAR 0x05 /* Auto-Neg. Link Partner Abitily */

+#define PHY_REG_ANER 0x06 /* Auto-Neg. Expansion Register */

+

+/* PHY Extended Registers */

+#define PHY_REG_MODE_CTRL 17

+#define PHY_REG_SPECIAL_MODE 18

+#define PHY_REG_SYMBOL_ERR_CNT 26

+#define PHY_REG_SPECIAL_CTRL 27

+#define PHY_REG_INT_SOURCE 29

+#define PHY_REG_INT_MASK 30

+#define PHY_REG_PHY_CTRL 31

+

+#define PHY_AUTO_NEG 0x3000 /* Select Auto Negotiation */

+#define PHY_AUTO_NEG_COMPLETE 0x1000 /* Auto negotiation have finished. */

+

+#define PHY_SPEED_FDUPLX 0x0010 /* Full Duplex */

+#define PHY_SPEED_100 0x0008 /* 100Mbit */

+#define ETHDEV_PHY_DEF_ADR 0x0100 /* Default PHY device address */

+

+#ifndef configEMAC_INTERRUPT_PRIORITY

+ #define configEMAC_INTERRUPT_PRIORITY 5

+#endif

+

+/* Time to wait between each inspection of the link status. */

+#define emacWAIT_FOR_LINK_TO_ESTABLISH_MS 500

+

+/* Short delay used in several places during the initialisation process. */

+#define emacSHORT_DELAY_MS 10

+

+/* Hardware specific bit definitions. */

+#define emacPINSEL2_VALUE ( 0x50150105 )

+

+

+

+/* ...and don't look more than this many times. */

+#define emacBUFFER_WAIT_ATTEMPTS ( 30 )

+

+/* Index to the Tx descriptor that is always used first for every Tx. The second

+descriptor is then used to re-send in order to speed up the uIP Tx process. */

+#define emacTX_DESC_INDEX ( 0 )

+

+/*-----------------------------------------------------------*/

+

+/* Setup the IO and peripherals required for Ethernet communication.*/

+static void prvSetupEMACHardware( void );

+/* Control the auto negotiate process.*/

+static void prvConfigurePHY( void );

+/*

+ * Wait for a link to be established, then setup the PHY according to the link

+ * parameters.

+ */

+static long prvSetupLinkStatus( void );

+/*

+ * Send lValue to the lPhyReg within the PHY.

+ */

+static long prvWritePHY( long lPhyReg, long lValue );

+/*

+ * Read a value from ucPhyReg within the PHY. *plStatus will be set to

+ * pdFALSE if there is an error.

+ */

+static unsigned short prvReadPHY( unsigned int ucPhyReg, NyLPC_TBool* o_status);

+

+

+static NyLPC_TBool start(const struct NyLPC_TEthAddr* i_eth_addr,NyLPC_TiEthernetDevice_onEvent i_handler,void* i_param);

+static void stop(void);

+static struct NyLPC_TTxBufferHeader* allocTxBuf(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size);

+static void releaseTxBuf(struct NyLPC_TTxBufferHeader* i_buf);

+

+/** EMAC ISRハンドラ*/

+static void emacIsrHandler(unsigned long i_status);

+

+/*-----------------------------------------------------------*/

+

+

+const static struct TiEthernetDevice _interface=

+{

+ "LAN8720",

+ start,

+ stop,

+ EthDev_LPC17xx_getRxEthFrame,

+ EthDev_LPC17xx_nextRxEthFrame,

+ allocTxBuf,

+ releaseTxBuf,

+ EthDev_LPC17xx_sendTxEthFrame,

+ EthDev_LPC17xx_processTx

+};

+static void* _event_param;

+static NyLPC_TiEthernetDevice_onEvent _event_handler;

+

+/*

+ * EthernetDeviceのファクトリー関数。インターフェイスを生成できればtrue

+ *

+ */

+NyLPC_TBool EthDev_LAN8720_getInterface(

+ const struct TiEthernetDevice** o_dev)

+{

+ unsigned long ulID1, ulID2;

+ NyLPC_TBool ret=NyLPC_TBool_TRUE;

+ //Reset MCU Interface. and wait for reset.

+ prvSetupEMACHardware();

+ //Check peripheral name

+ ulID1 = prvReadPHY( PHY_REG_IDR1, &ret );

+ ulID2 = prvReadPHY( PHY_REG_IDR2, &ret );

+ if( ( (ulID1 << 16UL ) | ( ulID2 & 0xFFF0UL ) ) != LAN8720_ID)

+ {

+ return NyLPC_TBool_FALSE;

+ }

+ *o_dev=&_interface;

+ LPC_EMAC->TxProduceIndex = 0;

+ LPC_EMAC->RxConsumeIndex = 0;

+ return NyLPC_TBool_TRUE;

+}

+

+

+

+/***********************************************************************

+ * RXバッファ関連の定義

+ ***********************************************************************/

+#define ETH_TX_BUF_BASE (void*)(ETH_BUF_BASE+ETH_FRAG_SIZE*NUM_RX_FRAG)

+

+static NyLPC_TBool start(const struct NyLPC_TEthAddr* i_eth_addr,NyLPC_TiEthernetDevice_onEvent i_handler,void* i_param)

+{

+ //ISRw割り込み設定

+ NyLPC_cIsr_setEnetISR(emacIsrHandler);

+ _event_handler=i_handler;

+ _event_param=i_param;

+ /* Set the Ethernet MAC Address registers */

+ LPC_EMAC->SA0 = (((uint32_t)(i_eth_addr->addr[0])) << 8 ) | i_eth_addr->addr[1];

+ LPC_EMAC->SA1 = (((uint32_t)(i_eth_addr->addr[2])) << 8 ) | i_eth_addr->addr[3];

+ LPC_EMAC->SA2 = (((uint32_t)(i_eth_addr->addr[4])) << 8 ) | i_eth_addr->addr[5];

+

+ //TXメモリマネージャの準備

+ NyLPC_cEthernetMM_initialize(ETH_TX_BUF_BASE);

+ /* Initialize Tx and Rx DMA Descriptors */

+ EthDev_LPC17xx_prevRxDescriptor();

+ EthDev_LPC17xx_prevTxDescriptor();

+

+ /* Setup the PHY. */

+ prvConfigurePHY();

+

+ //wait for Link up...

+ while(!prvSetupLinkStatus())

+ {

+ NyLPC_cThread_sleep(100);

+ }

+

+ /* Receive Broadcast and Perfect Match Packets */

+ LPC_EMAC->RxFilterCtrl = RFC_BCAST_EN | RFC_PERFECT_EN | RFC_MCAST_EN;

+

+ //Ethernetの割込み開始設定

+ NyLPC_cIsr_enterCritical();

+ {

+ /* Reset all interrupts */

+ LPC_EMAC->IntClear = 0xffff;

+ LPC_EMAC->IntEnable = ( INT_RX_DONE | INT_TX_DONE );

+ /* Enable receive and transmit mode of MAC Ethernet core */

+ LPC_EMAC->Command |= ( CR_RX_EN | CR_TX_EN );

+ LPC_EMAC->MAC1 |= MAC1_REC_EN;

+

+ /* Set the interrupt priority to the max permissible to cause some

+ interrupt nesting. */

+ NVIC_SetPriority( ENET_IRQn, configEMAC_INTERRUPT_PRIORITY );

+

+ /* Enable the interrupt. */

+ NVIC_EnableIRQ( ENET_IRQn );

+ }

+ NyLPC_cIsr_exitCritical();

+

+ return NyLPC_TBool_TRUE;

+}

+static void stop(void)

+{

+ NyLPC_cIsr_enterCritical();

+ {

+ LPC_EMAC->IntEnable = (~(INT_RX_DONE|INT_TX_DONE))&LPC_EMAC->IntEnable;

+ NVIC_DisableIRQ( ENET_IRQn );

+ }

+ NyLPC_cIsr_exitCritical();

+ LPC_EMAC->Command &= ~( CR_RX_EN | CR_TX_EN );

+ LPC_EMAC->MAC1 &= ~MAC1_REC_EN;

+ //ISR割り込み解除

+ NyLPC_cIsr_setEnetISR(NULL);

+ //TXメモリマネージャの終了

+ NyLPC_cEthernetMM_finalize();

+}

+

+

+static struct NyLPC_TTxBufferHeader* allocTxBuf(NyLPC_TUInt16 i_hint,NyLPC_TUInt16* o_size)

+{

+ return NyLPC_cEthernetMM_alloc(i_hint,o_size);

+}

+static void releaseTxBuf(struct NyLPC_TTxBufferHeader* i_buf)

+{

+ NyLPC_cEthernetMM_release(i_buf);

+}

+

+

+

+/********************************************************************************

+ * Private functions

+ *******************************************************************************/

+

+/*-----------------------------------------------------------*/

+

+/*-----------------------------------------------------------*/

+

+static void prvSetupEMACHardware( void )

+{

+ unsigned short us;

+ long x;

+ NyLPC_TBool lDummy;

+

+ /* Power Up the EMAC controller. */

+ LPC_SC->PCONP |= 0x40000000;

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS);

+

+ /* Enable P1 Ethernet Pins. */

+ LPC_PINCON->PINSEL2 = emacPINSEL2_VALUE;

+ LPC_PINCON->PINSEL3 = ( LPC_PINCON->PINSEL3 & ~0x0000000F ) | 0x00000005;

+

+ /* Reset all EMAC internal modules. */

+ LPC_EMAC->MAC1 = MAC1_RES_TX | MAC1_RES_MCS_TX | MAC1_RES_RX | MAC1_RES_MCS_RX | MAC1_SIM_RES | MAC1_SOFT_RES;

+ LPC_EMAC->Command = CR_REG_RES | CR_TX_RES | CR_RX_RES| CR_PASS_RUNT_FRM;

+ /* A short delay after reset. */

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS);

+

+ /* Initialize MAC control registers. */

+ LPC_EMAC->MAC1 = MAC1_PASS_ALL;

+ LPC_EMAC->MAC2 = MAC2_CRC_EN | MAC2_PAD_EN;

+ LPC_EMAC->MAXF = ETH_MAX_FLEN;

+ LPC_EMAC->CLRT = CLRT_DEF;

+ LPC_EMAC->IPGR = IPGR_DEF;

+

+ /*PCLK=18MHz, clock select=6, MDC=18/6=3MHz */ // I don't think so!

+ /* Enable Reduced MII interface. */

+ LPC_EMAC->MCFG = MCFG_CLK_DIV20 | MCFG_RES_MII;

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS);

+ LPC_EMAC->MCFG = MCFG_CLK_DIV20;

+

+ /* Enable Reduced MII interface. */

+ LPC_EMAC->Command = CR_RMII | CR_PASS_RUNT_FRM | CR_PASS_RX_FILT;

+

+ /* Reset Reduced MII Logic. */

+ LPC_EMAC->SUPP = SUPP_RES_RMII | SUPP_SPEED;

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS);

+ LPC_EMAC->SUPP = SUPP_SPEED;

+

+ /* Put the PHY in reset mode */

+ prvWritePHY( PHY_REG_BMCR, MCFG_RES_MII );

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5);

+

+ /* Wait for hardware reset to end. */

+ for( x = 0; x < 100; x++ )

+ {

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS * 5 );

+ us = prvReadPHY( PHY_REG_BMCR, &lDummy );

+ if( !( us & MCFG_RES_MII ) )

+ {

+ /* Reset complete */

+ break;

+ }

+ }

+}

+/*-----------------------------------------------------------*/

+

+

+/*-----------------------------------------------------------*/

+

+static NyLPC_TBool prvWritePHY( long lPhyReg, long lValue )

+{

+ const long lMaxTime = 10;

+ long x;

+

+ LPC_EMAC->MCMD = 0;

+ LPC_EMAC->MADR = ETHDEV_PHY_DEF_ADR | lPhyReg;

+ LPC_EMAC->MWTD = lValue;

+

+ for( x = 0; x < lMaxTime; x++ )

+ {

+ if( ( LPC_EMAC->MIND & MIND_BUSY ) == 0 )

+ {

+ /* Operation has finished. */

+ break;

+ }

+

+ NyLPC_cThread_sleep( emacSHORT_DELAY_MS);

+ }

+

+ if( x < lMaxTime )

+ {

+ return NyLPC_TBool_TRUE;

+ }

+ else

+ {

+ return NyLPC_TBool_FALSE;

+ }

+}

+/*-----------------------------------------------------------*/

+

+static unsigned short prvReadPHY( unsigned int ucPhyReg, NyLPC_TBool *o_status)

+{

+ long x;

+ const long lMaxTime = 10;

+

+ LPC_EMAC->MCMD = 1;

+ LPC_EMAC->MADR = ETHDEV_PHY_DEF_ADR | ucPhyReg;

+ LPC_EMAC->MCMD = MCMD_READ;

+