Library for Princeton PT6301 VFD controller. Used in Futaba CIG VFD tubes.

This is a library for the Princeton PT6301 VFD controller. The controller is used by Futaba 'Chip In Glass' (CIG) VFD tubes. The device supports upto 20 Grids of 5x7 matrix segments for 2 rows of characters (A and B). It also supports 1 additional segment for 2 rows (A and B). In addition to the internal ROM character set, the PT6301 also supports 16 User Defined Characters.

The PT6301 has an SPI Serial interface. Control data consists of an 8-bit command and one or more data bytes. Command and data are sent LSB first and latched on rising edge of CLK. Idle CLK is high. Data address is auto incremented. Same for Icon and UDC addresses. The commands and data are transmitted during CE low and latched on rising CE edge.

The PT6301 has internal memory for all characters and icons. The content is automatically displayed on the tube. The memory consists of two banks (row A and row B) for character memory and two banks (row A and row B) for icon memory. Each of those banks is accessed by separate commands. However, these command do not support addressing individual locations in the memory. Memory updates always start at address 0 in the selected row A or B. Consequently, the whole displaymemory needs to be rewritten when any location (except for 0) is to be updated. The library therefor uses a local mirror memory to store the display content, update one or more characters in the mirror-memory as needed, and rewrite the whole display memory from the mirror-content. The write-back is performed by calling the 'refresh' method. Additional advantage of the mirror-memory is that we can also implement wrap-around and scrolling from row A to B for multi-line displays.

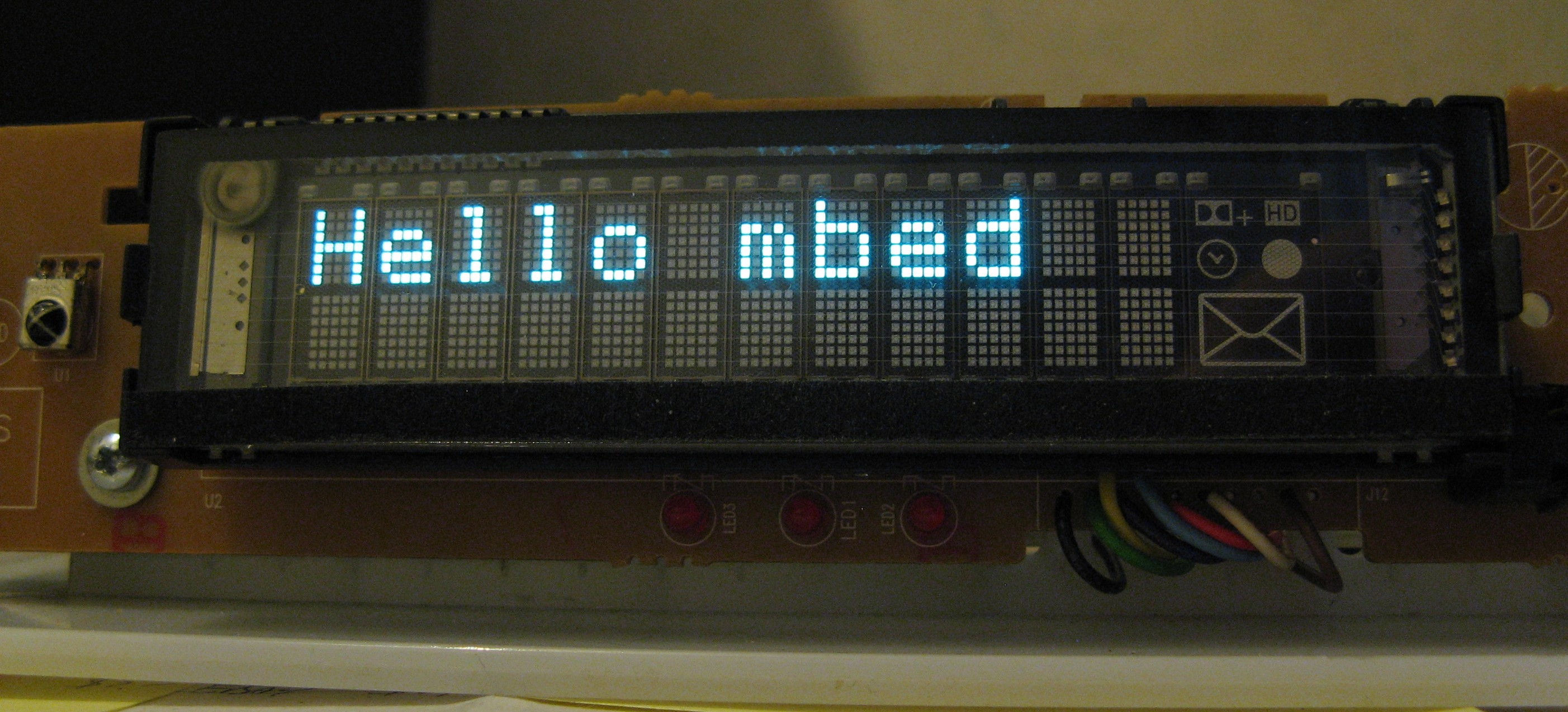

The lib was tested on displays salvaged from two Samsung cable TV receivers (e.g. Samsung SMT-C7140 and Samsung SMT-G7400). The examples don't use all features as this depends on how the controller has been applied inside the tube. The SMT-C7140 for example does not use the icon segments, but uses a separate grid to display a User Defined Character. The segments in the UDC light up specific icons (eg mail, clock). See picture below.

The example code is

Import programmbed_PT6301

Test for PT6301 VFD. First release.

I stumbled on the SMT-C7140 display and found some useful reverse engineering info by Codebeat here that helped to identify the controller. The pinout for the VFD tube connector (starting from the left side in the picture above) is: GND1, GND2, +35V DC (switched), 5V DC supply (switched), OSC pin (RC network between 5V and GND), /RST, /CS, CLK, DAT, NC, NC

The 35V DC is generated on the PCB by a DC/DC converter. The 35V generator, the 5V supply and the filament supply are all enabled by a pin on the connector at the bottom of the PCB.

The SMT-G7400 had a similar schematic for the tube connection as the SMT-C7140, but used a dedicated processor on the display PCB. The processor was removed and replaced by flying wires to an mbed LPC1768 for testing with the lib.

General explanation of VFD is here

PT6302.cpp@0:ecc29c13a997, 2017-12-03 (annotated)

- Committer:

- wim

- Date:

- Sun Dec 03 18:02:15 2017 +0000

- Revision:

- 0:ecc29c13a997

Library for Princeton PT6302 VFD controller.; Note the PT6302 is identical to the OKI ML9208.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| wim | 0:ecc29c13a997 | 1 | /* mbed PT6302 Library, for Princeton LC7571X VFD controller |

| wim | 0:ecc29c13a997 | 2 | * Note the PT6302 is identical to the OKI ML9208 |

| wim | 0:ecc29c13a997 | 3 | * |

| wim | 0:ecc29c13a997 | 4 | * Copyright (c) 2017, v01: WH, Initial version |

| wim | 0:ecc29c13a997 | 5 | * |

| wim | 0:ecc29c13a997 | 6 | * Permission is hereby granted, free of charge, to any person obtaining a copy |

| wim | 0:ecc29c13a997 | 7 | * of this software and associated documentation files (the "Software"), to deal |

| wim | 0:ecc29c13a997 | 8 | * in the Software without restriction, including without limitation the rights |

| wim | 0:ecc29c13a997 | 9 | * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell |

| wim | 0:ecc29c13a997 | 10 | * copies of the Software, and to permit persons to whom the Software is |

| wim | 0:ecc29c13a997 | 11 | * furnished to do so, subject to the following conditions: |

| wim | 0:ecc29c13a997 | 12 | * |

| wim | 0:ecc29c13a997 | 13 | * The above copyright notice and this permission notice shall be included in |

| wim | 0:ecc29c13a997 | 14 | * all copies or substantial portions of the Software. |

| wim | 0:ecc29c13a997 | 15 | * |

| wim | 0:ecc29c13a997 | 16 | * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR |

| wim | 0:ecc29c13a997 | 17 | * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, |

| wim | 0:ecc29c13a997 | 18 | * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE |

| wim | 0:ecc29c13a997 | 19 | * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER |

| wim | 0:ecc29c13a997 | 20 | * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, |

| wim | 0:ecc29c13a997 | 21 | * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN |

| wim | 0:ecc29c13a997 | 22 | * THE SOFTWARE. |

| wim | 0:ecc29c13a997 | 23 | */ |

| wim | 0:ecc29c13a997 | 24 | |

| wim | 0:ecc29c13a997 | 25 | #include "mbed.h" |

| wim | 0:ecc29c13a997 | 26 | #include "PT6302.h" |

| wim | 0:ecc29c13a997 | 27 | #include "PT6302_UDC.inc" |

| wim | 0:ecc29c13a997 | 28 | |

| wim | 0:ecc29c13a997 | 29 | |

| wim | 0:ecc29c13a997 | 30 | /** Constructor for class for driving Princeton PT6302 VFD controller |

| wim | 0:ecc29c13a997 | 31 | * |

| wim | 0:ecc29c13a997 | 32 | * @brief Supports upto 16 Grids of 35 matrix segments. |

| wim | 0:ecc29c13a997 | 33 | * Also supports 2 additional segments and 2 port pins. |

| wim | 0:ecc29c13a997 | 34 | * SPI bus interface device. |

| wim | 0:ecc29c13a997 | 35 | * @param PinName mosi, sclk, cs SPI bus pins |

| wim | 0:ecc29c13a997 | 36 | * @param Mode selects number of Grids and Segments (default 16 Grids, 2 additional segments) |

| wim | 0:ecc29c13a997 | 37 | */ |

| wim | 0:ecc29c13a997 | 38 | PT6302::PT6302(PinName mosi, PinName sclk, PinName cs, Mode mode) : _spi(mosi,NC,sclk), _cs(cs), _mode(mode) { |

| wim | 0:ecc29c13a997 | 39 | |

| wim | 0:ecc29c13a997 | 40 | _init(); |

| wim | 0:ecc29c13a997 | 41 | } |

| wim | 0:ecc29c13a997 | 42 | |

| wim | 0:ecc29c13a997 | 43 | /** Init the PT6302 interface and the controller |

| wim | 0:ecc29c13a997 | 44 | * |

| wim | 0:ecc29c13a997 | 45 | * @param none |

| wim | 0:ecc29c13a997 | 46 | * @return none |

| wim | 0:ecc29c13a997 | 47 | */ |

| wim | 0:ecc29c13a997 | 48 | void PT6302::_init(){ |

| wim | 0:ecc29c13a997 | 49 | |

| wim | 0:ecc29c13a997 | 50 | //init SPI |

| wim | 0:ecc29c13a997 | 51 | _cs=1; |

| wim | 0:ecc29c13a997 | 52 | _spi.format(8,3); //PT6302 uses mode 3 (Clock High on Idle, Data latched on second (=rising) edge) |

| wim | 0:ecc29c13a997 | 53 | _spi.frequency(100000); |

| wim | 0:ecc29c13a997 | 54 | // _spi.frequency(250000); |

| wim | 0:ecc29c13a997 | 55 | |

| wim | 0:ecc29c13a997 | 56 | //init controller |

| wim | 0:ecc29c13a997 | 57 | //setPort(0x0); // Port Off (default at Reset) |

| wim | 0:ecc29c13a997 | 58 | |

| wim | 0:ecc29c13a997 | 59 | // Set number of Grids |

| wim | 0:ecc29c13a997 | 60 | _writeCmd((PT6302_GRID_REG | _mode)); // Command register & value |

| wim | 0:ecc29c13a997 | 61 | |

| wim | 0:ecc29c13a997 | 62 | setBrightness(PT6302_BRT_DEF); // Default Brightness |

| wim | 0:ecc29c13a997 | 63 | |

| wim | 0:ecc29c13a997 | 64 | // Clear the DCRAM and ADRAM (undefined at Reset) |

| wim | 0:ecc29c13a997 | 65 | cls(); |

| wim | 0:ecc29c13a997 | 66 | |

| wim | 0:ecc29c13a997 | 67 | // Clear the UDC RAM (undefined at Reset) |

| wim | 0:ecc29c13a997 | 68 | const char udc_none[] = {0x00,0x00,0x00,0x00,0x00}; |

| wim | 0:ecc29c13a997 | 69 | for (int idx=0; idx < PT6302_NR_UDC; idx++) { |

| wim | 0:ecc29c13a997 | 70 | setUDC(idx, (char *)udc_none); |

| wim | 0:ecc29c13a997 | 71 | } |

| wim | 0:ecc29c13a997 | 72 | |

| wim | 0:ecc29c13a997 | 73 | setDisplay(true); // Display On |

| wim | 0:ecc29c13a997 | 74 | } |

| wim | 0:ecc29c13a997 | 75 | |

| wim | 0:ecc29c13a997 | 76 | |

| wim | 0:ecc29c13a997 | 77 | /** Clear the screen |

| wim | 0:ecc29c13a997 | 78 | * |

| wim | 0:ecc29c13a997 | 79 | * @param none |

| wim | 0:ecc29c13a997 | 80 | * @return none |

| wim | 0:ecc29c13a997 | 81 | */ |

| wim | 0:ecc29c13a997 | 82 | void PT6302::cls() { |

| wim | 0:ecc29c13a997 | 83 | |

| wim | 0:ecc29c13a997 | 84 | for (int cnt=0; cnt<PT6302_DSP_MEM; cnt++) { |

| wim | 0:ecc29c13a997 | 85 | writeData(char (' '), cnt); // data |

| wim | 0:ecc29c13a997 | 86 | // writeData(0x00, cnt); // data |

| wim | 0:ecc29c13a997 | 87 | } |

| wim | 0:ecc29c13a997 | 88 | |

| wim | 0:ecc29c13a997 | 89 | for (int cnt=0; cnt<PT6302_ADD_MEM; cnt++) { |

| wim | 0:ecc29c13a997 | 90 | writeAData(0x00, cnt); // adata |

| wim | 0:ecc29c13a997 | 91 | } |

| wim | 0:ecc29c13a997 | 92 | } |

| wim | 0:ecc29c13a997 | 93 | |

| wim | 0:ecc29c13a997 | 94 | |

| wim | 0:ecc29c13a997 | 95 | /** Set Brightness |

| wim | 0:ecc29c13a997 | 96 | * |

| wim | 0:ecc29c13a997 | 97 | * @param char brightness (3 significant bits, valid range 0..7) |

| wim | 0:ecc29c13a997 | 98 | * @return none |

| wim | 0:ecc29c13a997 | 99 | */ |

| wim | 0:ecc29c13a997 | 100 | void PT6302::setBrightness(char brightness){ |

| wim | 0:ecc29c13a997 | 101 | |

| wim | 0:ecc29c13a997 | 102 | //Sanity check |

| wim | 0:ecc29c13a997 | 103 | brightness = brightness & PT6302_BRT_MSK; // mask invalid bits |

| wim | 0:ecc29c13a997 | 104 | |

| wim | 0:ecc29c13a997 | 105 | _writeCmd((PT6302_BRT_REG | brightness)); // Command register & value |

| wim | 0:ecc29c13a997 | 106 | } |

| wim | 0:ecc29c13a997 | 107 | |

| wim | 0:ecc29c13a997 | 108 | /** Set the Display mode On/off |

| wim | 0:ecc29c13a997 | 109 | * |

| wim | 0:ecc29c13a997 | 110 | * @param bool display mode |

| wim | 0:ecc29c13a997 | 111 | * @return none |

| wim | 0:ecc29c13a997 | 112 | */ |

| wim | 0:ecc29c13a997 | 113 | void PT6302::setDisplay(bool on) { |

| wim | 0:ecc29c13a997 | 114 | char display; |

| wim | 0:ecc29c13a997 | 115 | |

| wim | 0:ecc29c13a997 | 116 | if (on) { |

| wim | 0:ecc29c13a997 | 117 | display = PT6302_DSPL_NRM; // normal mode, show Display RAM content |

| wim | 0:ecc29c13a997 | 118 | } |

| wim | 0:ecc29c13a997 | 119 | else { |

| wim | 0:ecc29c13a997 | 120 | display = PT6302_DSPL_OFF; // all segments off |

| wim | 0:ecc29c13a997 | 121 | } |

| wim | 0:ecc29c13a997 | 122 | |

| wim | 0:ecc29c13a997 | 123 | _writeCmd((PT6302_DSPL_REG | display)); // Command register & value |

| wim | 0:ecc29c13a997 | 124 | } |

| wim | 0:ecc29c13a997 | 125 | |

| wim | 0:ecc29c13a997 | 126 | /** Set Port |

| wim | 0:ecc29c13a997 | 127 | * |

| wim | 0:ecc29c13a997 | 128 | * @param char port (2 least significant bits) |

| wim | 0:ecc29c13a997 | 129 | * @return none |

| wim | 0:ecc29c13a997 | 130 | */ |

| wim | 0:ecc29c13a997 | 131 | void PT6302::setPort (char port){ |

| wim | 0:ecc29c13a997 | 132 | |

| wim | 0:ecc29c13a997 | 133 | //Sanity check |

| wim | 0:ecc29c13a997 | 134 | _port = port & PT6302_PDAT_MSK; // Mask invalid bits |

| wim | 0:ecc29c13a997 | 135 | |

| wim | 0:ecc29c13a997 | 136 | _writeCmd((PT6302_PDAT_REG | _port)); // Command register & value |

| wim | 0:ecc29c13a997 | 137 | _writeCmd((PT6302_PDAT_REG | _port)); // Command register & value (Dummy cmd to show on Latched LEDs) |

| wim | 0:ecc29c13a997 | 138 | } |

| wim | 0:ecc29c13a997 | 139 | |

| wim | 0:ecc29c13a997 | 140 | |

| wim | 0:ecc29c13a997 | 141 | /** Set User Defined Characters (UDC) |

| wim | 0:ecc29c13a997 | 142 | * |

| wim | 0:ecc29c13a997 | 143 | * @param unsigned char udc_idx The Index of the UDC (0..7) |

| wim | 0:ecc29c13a997 | 144 | * @param UDCData_t udc_data The bitpattern for the UDC (5 bytes) |

| wim | 0:ecc29c13a997 | 145 | * @return none |

| wim | 0:ecc29c13a997 | 146 | */ |

| wim | 0:ecc29c13a997 | 147 | void PT6302::setUDC(unsigned char udc_idx, UDCData_t udc_data) { |

| wim | 0:ecc29c13a997 | 148 | |

| wim | 0:ecc29c13a997 | 149 | //Sanity check |

| wim | 0:ecc29c13a997 | 150 | udc_idx = udc_idx & PT6302_UADR_MSK; // mask invalid bits |

| wim | 0:ecc29c13a997 | 151 | |

| wim | 0:ecc29c13a997 | 152 | _cs=0; // Send Command & Params |

| wim | 0:ecc29c13a997 | 153 | wait_us(1); |

| wim | 0:ecc29c13a997 | 154 | _spi.write(_flip(PT6302_UDC_REG | udc_idx)); // Command register & address |

| wim | 0:ecc29c13a997 | 155 | wait_us(PT6302_CMD_DLY); // Command Delay |

| wim | 0:ecc29c13a997 | 156 | |

| wim | 0:ecc29c13a997 | 157 | _spi.write(_flip(udc_data[0] & PT6302_UDC_MSK)); // CD30 CD25 ...... CD0 |

| wim | 0:ecc29c13a997 | 158 | _spi.write(_flip(udc_data[1] & PT6302_UDC_MSK)); // CD31 CD26 ...... CD1 |

| wim | 0:ecc29c13a997 | 159 | _spi.write(_flip(udc_data[2] & PT6302_UDC_MSK)); // CD32 CD27 ...... CD2 |

| wim | 0:ecc29c13a997 | 160 | _spi.write(_flip(udc_data[3] & PT6302_UDC_MSK)); // CD33 CD28 ...... CD3 |

| wim | 0:ecc29c13a997 | 161 | _spi.write(_flip(udc_data[4] & PT6302_UDC_MSK)); // CD34 CD29 ...... CD4 |

| wim | 0:ecc29c13a997 | 162 | |

| wim | 0:ecc29c13a997 | 163 | wait_us(PT6302_CS_DLY); // CS Hold Delay |

| wim | 0:ecc29c13a997 | 164 | _cs=1; // Latch Command & Params |

| wim | 0:ecc29c13a997 | 165 | |

| wim | 0:ecc29c13a997 | 166 | wait_us(PT6302_CMD_DLY); // Command Delay |

| wim | 0:ecc29c13a997 | 167 | } |

| wim | 0:ecc29c13a997 | 168 | |

| wim | 0:ecc29c13a997 | 169 | |

| wim | 0:ecc29c13a997 | 170 | /** Write Data to PT6302 |

| wim | 0:ecc29c13a997 | 171 | * |

| wim | 0:ecc29c13a997 | 172 | * @param char data Character code |

| wim | 0:ecc29c13a997 | 173 | * @param char address Parameter for data |

| wim | 0:ecc29c13a997 | 174 | * @return none |

| wim | 0:ecc29c13a997 | 175 | */ |

| wim | 0:ecc29c13a997 | 176 | void PT6302::writeData(char data, char address){ |

| wim | 0:ecc29c13a997 | 177 | |

| wim | 0:ecc29c13a997 | 178 | //Sanity check |

| wim | 0:ecc29c13a997 | 179 | address = address & PT6302_DADR_MSK; // mask invalid bits |

| wim | 0:ecc29c13a997 | 180 | |

| wim | 0:ecc29c13a997 | 181 | _writeCmd((PT6302_DATA_REG | address), // Command register & address |

| wim | 0:ecc29c13a997 | 182 | data); // Character code |

| wim | 0:ecc29c13a997 | 183 | } |

| wim | 0:ecc29c13a997 | 184 | |

| wim | 0:ecc29c13a997 | 185 | /** Write Additional Data to PT6302 |

| wim | 0:ecc29c13a997 | 186 | * |

| wim | 0:ecc29c13a997 | 187 | * @param char adata Additional code (annunciator) |

| wim | 0:ecc29c13a997 | 188 | * @param char address Parameter for data |

| wim | 0:ecc29c13a997 | 189 | * @return none |

| wim | 0:ecc29c13a997 | 190 | */ |

| wim | 0:ecc29c13a997 | 191 | void PT6302::writeAData(char adata, char address){ |

| wim | 0:ecc29c13a997 | 192 | |

| wim | 0:ecc29c13a997 | 193 | //Sanity check |

| wim | 0:ecc29c13a997 | 194 | address = address & PT6302_AADR_MSK; // mask invalid bits |

| wim | 0:ecc29c13a997 | 195 | |

| wim | 0:ecc29c13a997 | 196 | _writeCmd((PT6302_ADAT_REG | address), // Command register & ADRAM address |

| wim | 0:ecc29c13a997 | 197 | adata); // ADATA |

| wim | 0:ecc29c13a997 | 198 | } |

| wim | 0:ecc29c13a997 | 199 | |

| wim | 0:ecc29c13a997 | 200 | /** Write command and data to PT6302 |

| wim | 0:ecc29c13a997 | 201 | * |

| wim | 0:ecc29c13a997 | 202 | * @param char cmd Command byte |

| wim | 0:ecc29c13a997 | 203 | * @param char data Parameter for command |

| wim | 0:ecc29c13a997 | 204 | * @return none |

| wim | 0:ecc29c13a997 | 205 | */ |

| wim | 0:ecc29c13a997 | 206 | void PT6302::_writeCmd(char cmd, char data){ |

| wim | 0:ecc29c13a997 | 207 | |

| wim | 0:ecc29c13a997 | 208 | _cs=0; // Prepare to send Command and data |

| wim | 0:ecc29c13a997 | 209 | wait_us(1); |

| wim | 0:ecc29c13a997 | 210 | |

| wim | 0:ecc29c13a997 | 211 | _spi.write(_flip(cmd)); // Command register & value |

| wim | 0:ecc29c13a997 | 212 | |

| wim | 0:ecc29c13a997 | 213 | wait_us(PT6302_CMD_DLY); // Command Delay |

| wim | 0:ecc29c13a997 | 214 | |

| wim | 0:ecc29c13a997 | 215 | _spi.write(_flip(data)); // data |

| wim | 0:ecc29c13a997 | 216 | |

| wim | 0:ecc29c13a997 | 217 | wait_us(PT6302_CS_DLY); // CS Hold Delay |

| wim | 0:ecc29c13a997 | 218 | _cs=1; // Latch Command and data |

| wim | 0:ecc29c13a997 | 219 | |

| wim | 0:ecc29c13a997 | 220 | wait_us(PT6302_CMD_DLY); // Command Delay |

| wim | 0:ecc29c13a997 | 221 | } |

| wim | 0:ecc29c13a997 | 222 | |

| wim | 0:ecc29c13a997 | 223 | /** Write command to PT6302 |

| wim | 0:ecc29c13a997 | 224 | * |

| wim | 0:ecc29c13a997 | 225 | * @param char cmd Command byte |

| wim | 0:ecc29c13a997 | 226 | * @return none |

| wim | 0:ecc29c13a997 | 227 | */ |

| wim | 0:ecc29c13a997 | 228 | void PT6302::_writeCmd(char cmd){ |

| wim | 0:ecc29c13a997 | 229 | |

| wim | 0:ecc29c13a997 | 230 | _cs=0; // Prepare to send Command |

| wim | 0:ecc29c13a997 | 231 | wait_us(1); |

| wim | 0:ecc29c13a997 | 232 | |

| wim | 0:ecc29c13a997 | 233 | _spi.write(_flip(cmd)); // Command register & value |

| wim | 0:ecc29c13a997 | 234 | |

| wim | 0:ecc29c13a997 | 235 | wait_us(PT6302_CS_DLY); // CS Hold Delay |

| wim | 0:ecc29c13a997 | 236 | _cs=1; // Latch Command |

| wim | 0:ecc29c13a997 | 237 | |

| wim | 0:ecc29c13a997 | 238 | wait_us(PT6302_CMD_DLY); // Command Delay |

| wim | 0:ecc29c13a997 | 239 | } |

| wim | 0:ecc29c13a997 | 240 | |

| wim | 0:ecc29c13a997 | 241 | |

| wim | 0:ecc29c13a997 | 242 | |

| wim | 0:ecc29c13a997 | 243 | /** Helper to reverse all command or databits. The PT6302 expects LSB first, whereas SPI is MSB first |

| wim | 0:ecc29c13a997 | 244 | * |

| wim | 0:ecc29c13a997 | 245 | * @param char data |

| wim | 0:ecc29c13a997 | 246 | * @return bitreversed data |

| wim | 0:ecc29c13a997 | 247 | */ |

| wim | 0:ecc29c13a997 | 248 | char PT6302::_flip(char data) { |

| wim | 0:ecc29c13a997 | 249 | char value=0; |

| wim | 0:ecc29c13a997 | 250 | |

| wim | 0:ecc29c13a997 | 251 | if (data & 0x01) {value |= 0x80;} ; |

| wim | 0:ecc29c13a997 | 252 | if (data & 0x02) {value |= 0x40;} ; |

| wim | 0:ecc29c13a997 | 253 | if (data & 0x04) {value |= 0x20;} ; |

| wim | 0:ecc29c13a997 | 254 | if (data & 0x08) {value |= 0x10;} ; |

| wim | 0:ecc29c13a997 | 255 | if (data & 0x10) {value |= 0x08;} ; |

| wim | 0:ecc29c13a997 | 256 | if (data & 0x20) {value |= 0x04;} ; |

| wim | 0:ecc29c13a997 | 257 | if (data & 0x40) {value |= 0x02;} ; |

| wim | 0:ecc29c13a997 | 258 | if (data & 0x80) {value |= 0x01;} ; |

| wim | 0:ecc29c13a997 | 259 | return value; |

| wim | 0:ecc29c13a997 | 260 | } |

| wim | 0:ecc29c13a997 | 261 | |

| wim | 0:ecc29c13a997 | 262 | |

| wim | 0:ecc29c13a997 | 263 | #if (HANNSTAR_TEST == 1) |

| wim | 0:ecc29c13a997 | 264 | |

| wim | 0:ecc29c13a997 | 265 | /** Constructor for class for Princeton PT6302 VFD controller as used in HANNSTAR |

| wim | 0:ecc29c13a997 | 266 | * |

| wim | 0:ecc29c13a997 | 267 | * @brief Supports 16 Grids of 35 Segments without additional Segments. |

| wim | 0:ecc29c13a997 | 268 | * |

| wim | 0:ecc29c13a997 | 269 | * @param PinName mosi, miso, sclk, cs SPI bus pins |

| wim | 0:ecc29c13a997 | 270 | */ |

| wim | 0:ecc29c13a997 | 271 | PT6302_HANNSTAR::PT6302_HANNSTAR(PinName mosi, PinName sclk, PinName cs) : PT6302(mosi, sclk, cs, Grid16_Add2) { |

| wim | 0:ecc29c13a997 | 272 | _column = 0; |

| wim | 0:ecc29c13a997 | 273 | _columns = HANNSTAR_NR_DIGITS; |

| wim | 0:ecc29c13a997 | 274 | |

| wim | 0:ecc29c13a997 | 275 | //Enable VGen for VFD Power Supply |

| wim | 0:ecc29c13a997 | 276 | setVGen(true); |

| wim | 0:ecc29c13a997 | 277 | } |

| wim | 0:ecc29c13a997 | 278 | |

| wim | 0:ecc29c13a997 | 279 | /** Locate cursor to a screen column |

| wim | 0:ecc29c13a997 | 280 | * |

| wim | 0:ecc29c13a997 | 281 | * @param column The horizontal position from the left, indexed from 0 |

| wim | 0:ecc29c13a997 | 282 | * @return none |

| wim | 0:ecc29c13a997 | 283 | */ |

| wim | 0:ecc29c13a997 | 284 | void PT6302_HANNSTAR::locate(int column) { |

| wim | 0:ecc29c13a997 | 285 | //sanity check |

| wim | 0:ecc29c13a997 | 286 | if (column < 0) {column = 0;} |

| wim | 0:ecc29c13a997 | 287 | if (column > (_columns - 1)) {column = _columns - 1;} |

| wim | 0:ecc29c13a997 | 288 | |

| wim | 0:ecc29c13a997 | 289 | _column = column; |

| wim | 0:ecc29c13a997 | 290 | } |

| wim | 0:ecc29c13a997 | 291 | |

| wim | 0:ecc29c13a997 | 292 | |

| wim | 0:ecc29c13a997 | 293 | /** Number of screen columns |

| wim | 0:ecc29c13a997 | 294 | * |

| wim | 0:ecc29c13a997 | 295 | * @param none |

| wim | 0:ecc29c13a997 | 296 | * @return columns |

| wim | 0:ecc29c13a997 | 297 | */ |

| wim | 0:ecc29c13a997 | 298 | int PT6302_HANNSTAR::columns() { |

| wim | 0:ecc29c13a997 | 299 | return _columns; |

| wim | 0:ecc29c13a997 | 300 | } |

| wim | 0:ecc29c13a997 | 301 | |

| wim | 0:ecc29c13a997 | 302 | |

| wim | 0:ecc29c13a997 | 303 | /** Clear the screen and locate to 0 |

| wim | 0:ecc29c13a997 | 304 | * |

| wim | 0:ecc29c13a997 | 305 | * @param bool clrAll Clear Icons also (default = false) |

| wim | 0:ecc29c13a997 | 306 | * @return none |

| wim | 0:ecc29c13a997 | 307 | */ |

| wim | 0:ecc29c13a997 | 308 | void PT6302_HANNSTAR::cls(bool clrAll) { |

| wim | 0:ecc29c13a997 | 309 | |

| wim | 0:ecc29c13a997 | 310 | for (int cnt=0; cnt<HANNSTAR_NR_DIGITS; cnt++) { |

| wim | 0:ecc29c13a997 | 311 | writeData(char (' '), cnt); // data |

| wim | 0:ecc29c13a997 | 312 | } |

| wim | 0:ecc29c13a997 | 313 | |

| wim | 0:ecc29c13a997 | 314 | if (clrAll) { |

| wim | 0:ecc29c13a997 | 315 | //Clear Icons |

| wim | 0:ecc29c13a997 | 316 | for (int cnt=0; cnt<HANNSTAR_NR_DIGITS; cnt++) { |

| wim | 0:ecc29c13a997 | 317 | writeAData(0x00, cnt); // adata |

| wim | 0:ecc29c13a997 | 318 | } |

| wim | 0:ecc29c13a997 | 319 | } |

| wim | 0:ecc29c13a997 | 320 | |

| wim | 0:ecc29c13a997 | 321 | _column = 0; |

| wim | 0:ecc29c13a997 | 322 | } |

| wim | 0:ecc29c13a997 | 323 | |

| wim | 0:ecc29c13a997 | 324 | |

| wim | 0:ecc29c13a997 | 325 | /** Set Port |

| wim | 0:ecc29c13a997 | 326 | * |

| wim | 0:ecc29c13a997 | 327 | * @param char port (Only Bit 1 is used) |

| wim | 0:ecc29c13a997 | 328 | * @return none |

| wim | 0:ecc29c13a997 | 329 | */ |

| wim | 0:ecc29c13a997 | 330 | void PT6302_HANNSTAR::setPort (char port){ |

| wim | 0:ecc29c13a997 | 331 | |

| wim | 0:ecc29c13a997 | 332 | //Sanity check |

| wim | 0:ecc29c13a997 | 333 | _port &= ~PT6302_HANN_PDAT_MSK; // Clear valid bits |

| wim | 0:ecc29c13a997 | 334 | _port |= (port & PT6302_HANN_PDAT_MSK); // Mask invalid bits |

| wim | 0:ecc29c13a997 | 335 | |

| wim | 0:ecc29c13a997 | 336 | _writeCmd((PT6302_PDAT_REG | _port)); // Command register & value |

| wim | 0:ecc29c13a997 | 337 | _writeCmd((PT6302_PDAT_REG | _port)); // Command register & value (Dummy cmd to show on Latched LEDs) |

| wim | 0:ecc29c13a997 | 338 | } |

| wim | 0:ecc29c13a997 | 339 | |

| wim | 0:ecc29c13a997 | 340 | |

| wim | 0:ecc29c13a997 | 341 | /** Set VFD VGen |

| wim | 0:ecc29c13a997 | 342 | * |

| wim | 0:ecc29c13a997 | 343 | * @param bool on |

| wim | 0:ecc29c13a997 | 344 | * @return none |

| wim | 0:ecc29c13a997 | 345 | */ |

| wim | 0:ecc29c13a997 | 346 | void PT6302_HANNSTAR::setVGen(bool on){ |

| wim | 0:ecc29c13a997 | 347 | |

| wim | 0:ecc29c13a997 | 348 | if (on) { |

| wim | 0:ecc29c13a997 | 349 | _port = _port | PT6302_HANN_VGEN; // VGen On |

| wim | 0:ecc29c13a997 | 350 | } |

| wim | 0:ecc29c13a997 | 351 | else { |

| wim | 0:ecc29c13a997 | 352 | _port = _port & ~PT6302_HANN_VGEN; // VGen Off |

| wim | 0:ecc29c13a997 | 353 | } |

| wim | 0:ecc29c13a997 | 354 | |

| wim | 0:ecc29c13a997 | 355 | _writeCmd((PT6302_PDAT_REG | _port)); // Command register & value |

| wim | 0:ecc29c13a997 | 356 | _writeCmd((PT6302_PDAT_REG | _port)); // Command register & value (Dummy cmd to show on Latched LEDs) |

| wim | 0:ecc29c13a997 | 357 | } |

| wim | 0:ecc29c13a997 | 358 | |

| wim | 0:ecc29c13a997 | 359 | |

| wim | 0:ecc29c13a997 | 360 | /** Write a single character (Stream implementation) |

| wim | 0:ecc29c13a997 | 361 | * |

| wim | 0:ecc29c13a997 | 362 | * @param value char to print |

| wim | 0:ecc29c13a997 | 363 | * @return value; |

| wim | 0:ecc29c13a997 | 364 | */ |

| wim | 0:ecc29c13a997 | 365 | int PT6302_HANNSTAR::_putc(int value) { |

| wim | 0:ecc29c13a997 | 366 | int addr; |

| wim | 0:ecc29c13a997 | 367 | |

| wim | 0:ecc29c13a997 | 368 | if ((value == '\n') || (value == '\r')) { |

| wim | 0:ecc29c13a997 | 369 | //No character to write |

| wim | 0:ecc29c13a997 | 370 | |

| wim | 0:ecc29c13a997 | 371 | //Update Cursor |

| wim | 0:ecc29c13a997 | 372 | _column = 0; |

| wim | 0:ecc29c13a997 | 373 | } |

| wim | 0:ecc29c13a997 | 374 | else if ((value >= 0) && (value < 256)) { |

| wim | 0:ecc29c13a997 | 375 | //Character to write |

| wim | 0:ecc29c13a997 | 376 | |

| wim | 0:ecc29c13a997 | 377 | //Translate between _column and displaybuffer entries |

| wim | 0:ecc29c13a997 | 378 | //Note that the HANNSTAR has 1 digit/grid. |

| wim | 0:ecc29c13a997 | 379 | //_column == 0 => Grid15 => addr = 15 |

| wim | 0:ecc29c13a997 | 380 | //_column == 1 => Grid14 => addr = 14 |

| wim | 0:ecc29c13a997 | 381 | // .... |

| wim | 0:ecc29c13a997 | 382 | //_column == 15 => Grid1 => addr = 0 |

| wim | 0:ecc29c13a997 | 383 | addr = (15 - _column); // 1 Byte for every Grid; |

| wim | 0:ecc29c13a997 | 384 | |

| wim | 0:ecc29c13a997 | 385 | writeData(value, addr); |

| wim | 0:ecc29c13a997 | 386 | |

| wim | 0:ecc29c13a997 | 387 | //Update Cursor |

| wim | 0:ecc29c13a997 | 388 | _column++; |

| wim | 0:ecc29c13a997 | 389 | if (_column > (HANNSTAR_NR_DIGITS - 1)) { |

| wim | 0:ecc29c13a997 | 390 | _column = 0; |

| wim | 0:ecc29c13a997 | 391 | } |

| wim | 0:ecc29c13a997 | 392 | |

| wim | 0:ecc29c13a997 | 393 | } // if validChar |

| wim | 0:ecc29c13a997 | 394 | |

| wim | 0:ecc29c13a997 | 395 | return value; |

| wim | 0:ecc29c13a997 | 396 | } |

| wim | 0:ecc29c13a997 | 397 | |

| wim | 0:ecc29c13a997 | 398 | /** Get a single character (Stream implementation) |

| wim | 0:ecc29c13a997 | 399 | * |

| wim | 0:ecc29c13a997 | 400 | * @param none |

| wim | 0:ecc29c13a997 | 401 | * @return -1 |

| wim | 0:ecc29c13a997 | 402 | */ |

| wim | 0:ecc29c13a997 | 403 | int PT6302_HANNSTAR::_getc() { |

| wim | 0:ecc29c13a997 | 404 | return -1; |

| wim | 0:ecc29c13a997 | 405 | } |

| wim | 0:ecc29c13a997 | 406 | #endif |