LP1768 power mode implementation and measurement.

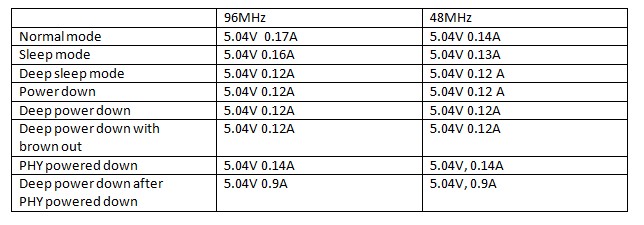

I measured the LP1768 power in different power mode and in different clock frequency using a USB power meter. The code could be found here http://mbed.org/users/steniu01/code/LP1768-lowpower_test. The data is shown below.

As the datasheet show, the sleep mode don't save much power while deep sleep and power down do. When reduce the clock frequency, power could be saved in normal run mode. The current is still relatively high in power down mode. I guess it is because it is the power cost by the peripherals. When power down the the PHY, power could be reduced further in Power Down mode. The next step is to investigate what will be the power reduced after powering down most of the peripherals.

2 comments on LP1768 power mode implementation and measurement. :

Please log in to post comments.

Your results do not look like these http://mbed.org/users/no2chem/notebook/mbed-power-controlconsumption/