The official mbed C/C SDK provides the software platform and libraries to build your applications.

Fork of mbed by

(01.May.2014) started sales! http://www.switch-science.com/catalog/1717/

(13.March.2014) updated to 0.5.0

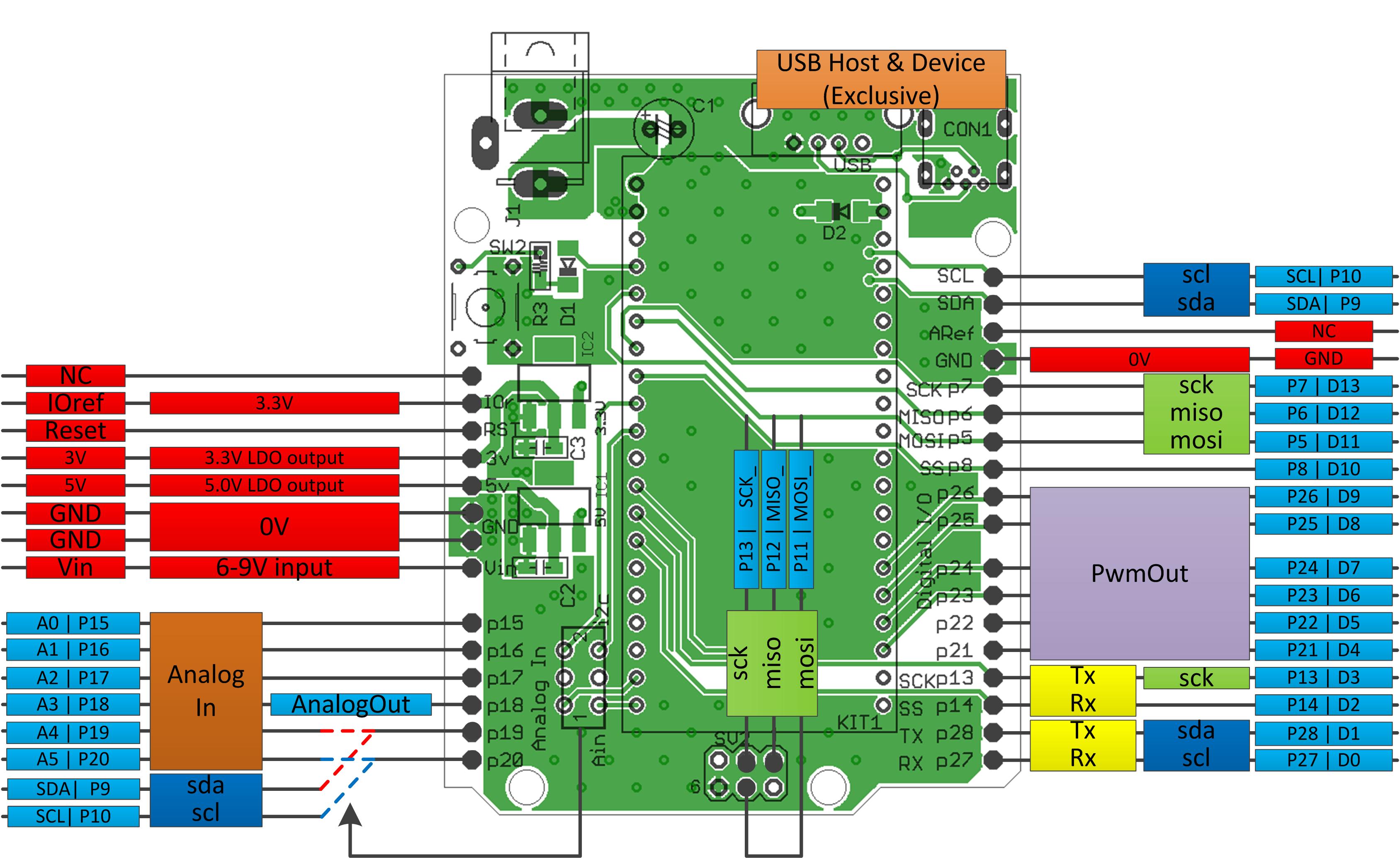

This is a pin conversion PCB from mbed 1768/11U24 to arduino UNO.

- So if you have both mbed and arduino shields, I guess you would be happy with such a conversion board :)

Photos

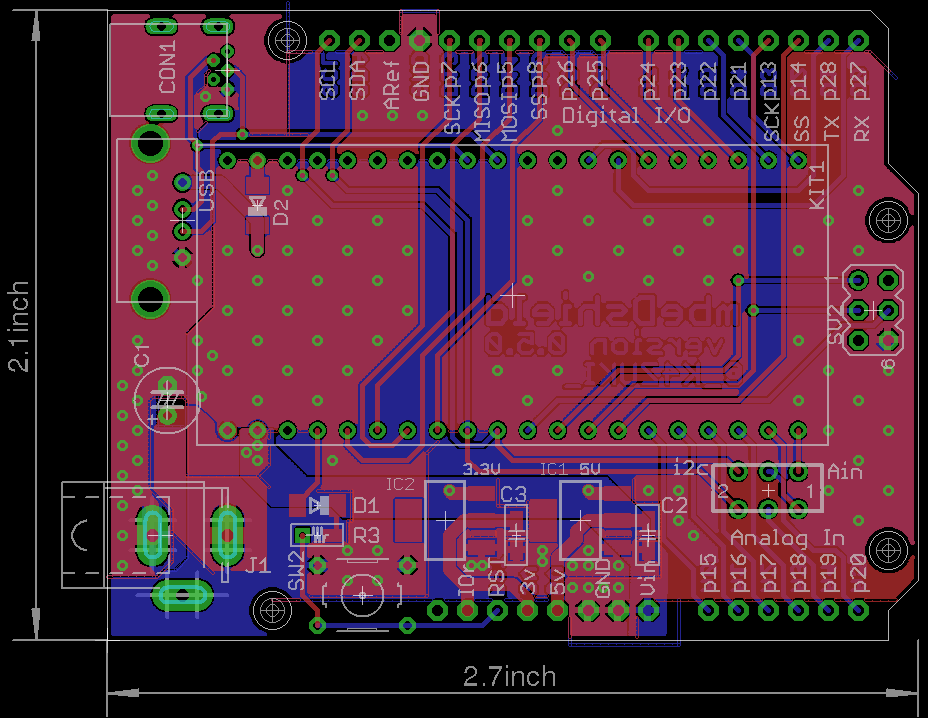

- Board photo vvv

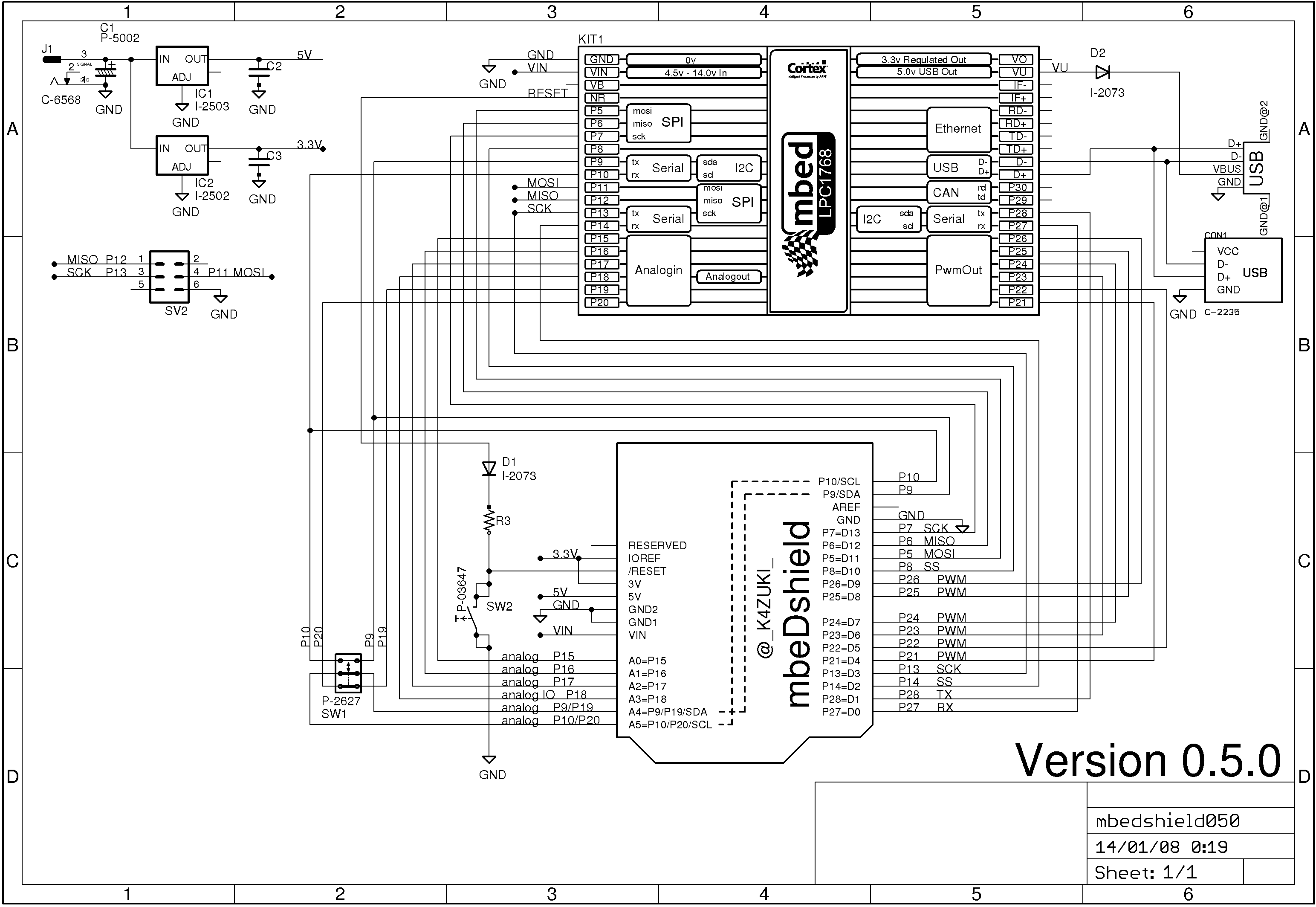

- Schematic photo vvv

- Functionality photo vvv

Latest eagle files

PCB >> /media/uploads/k4zuki/mbedshield050.brd

SCH >> /media/uploads/k4zuki/mbedshield050.sch

BIG changes from previous version

- Ethernet RJ45 connector is removed.

- http://mbed.org/components/Seeed-Ethernet-Shield-V20/ is the biggest hint to use Ethernet!

MostALL of components can be bought at Akizuki http://akizukidenshi.com/- But sorry, they do not send parts to abroad

- Pinout is changed!

| arduino | 0.4.0 | 0.5.0 |

|---|---|---|

| D4 | p12 | p21 |

| D5 | p11 | p22 |

| MOSI_ | none | p11 |

| MISO_ | none | p12 |

| SCK_ | none | p13 |

This design has bug(s)

- I2C functional pin differs between 1768 and 11U24.

Fixed bugs here

- MiniUSB cable cannot be connected on mbed if you solder high-height electrolytic capacitor on C3.

- http://akizukidenshi.com/catalog/g/gP-05002/ is the solution to make this 100% AKIZUKI parts!

- the 6-pin ISP port is not inprimented in version 0.4.0

it will be fixed in later version 0.4.1/0.4.2/0.5.0This has beenfixed

I am doing some porting to use existing arduino shields but it may faster if you do it by yourself...

you can use arduino PinName "A0-A5,D0-D13" plus backside SPI port for easier porting.

To do this you have to edit PinName enum in

- "mbed/TARGET_LPC1768/PinNames.h" or

- "mbed/TARGET_LPC11U24/PinNames.h" as per your target mbed.

here is the actual list: This list includes define switch to switch pin assignment

part_of_PinNames.h

USBTX = P0_2,

USBRX = P0_3,

//from here mbeDshield mod

D0=p27,

D1=p28,

D2=p14,

D3=p13,

#ifdef MBEDSHIELD_050

MOSI_=p11,

MISO_=p12,

SCK_=p13,

D4=p21,

D5=p22,

#else

D4=p12,

D5=p11,

#endif

D6=p23,

D7=p24,

D8=p25,

D9=p26,

D10=p8,

D11=p5,

D12=p6,

D13=p7,

A0=p15,

A1=p16,

A2=p17,

A3=p18,

A4=p19,

A5=p20,

SDA=p9,

SCL=p10,

//mbeDshield mod ends here

// Not connected

NC = (int)0xFFFFFFFF

Diff: LPC11U24/GCC_ARM/core_cmInstr.h

- Revision:

- 33:5364839841bd

- Parent:

- 27:7110ebee3484

--- a/LPC11U24/GCC_ARM/core_cmInstr.h Fri Jan 06 16:40:24 2012 +0000

+++ b/LPC11U24/GCC_ARM/core_cmInstr.h Tue Jan 10 12:00:50 2012 +0000

@@ -1,11 +1,11 @@

/**************************************************************************//**

* @file core_cmInstr.h

* @brief CMSIS Cortex-M Core Instruction Access Header File

- * @version V2.01

- * @date 06. December 2010

+ * @version V3.00

+ * @date 09. December 2011

*

* @note

- * Copyright (C) 2009-2010 ARM Limited. All rights reserved.

+ * Copyright (C) 2009-2011 ARM Limited. All rights reserved.

*

* @par

* ARM Limited (ARM) is supplying this software for use with Cortex-M

@@ -21,8 +21,8 @@

*

******************************************************************************/

-#ifndef __CORE_CMINSTR_H__

-#define __CORE_CMINSTR_H__

+#ifndef __CORE_CMINSTR_H

+#define __CORE_CMINSTR_H

/* ########################## Core Instruction Access ######################### */

@@ -31,9 +31,14 @@

@{

*/

-#if defined ( __CC_ARM ) /*------------------ RealView Compiler ----------------*/

+#if defined ( __CC_ARM ) /*------------------RealView Compiler -----------------*/

/* ARM armcc specific functions */

+#if (__ARMCC_VERSION < 400677)

+ #error "Please use ARM Compiler Toolchain V4.0.677 or later!"

+#endif

+

+

/** \brief No Operation

No Operation does nothing. This instruction can be used for code alignment purposes.

@@ -106,15 +111,11 @@

\param [in] value Value to reverse

\return Reversed value

*/

-#if (__ARMCC_VERSION < 400677)

-extern uint32_t __REV16(uint32_t value);

-#else /* (__ARMCC_VERSION >= 400677) */

-static __INLINE __ASM uint32_t __REV16(uint32_t value)

+static __attribute__((section(".rev16_text"))) __INLINE __ASM uint32_t __REV16(uint32_t value)

{

rev16 r0, r0

bx lr

}

-#endif /* __ARMCC_VERSION */

/** \brief Reverse byte order in signed short value

@@ -124,15 +125,11 @@

\param [in] value Value to reverse

\return Reversed value

*/

-#if (__ARMCC_VERSION < 400677)

-extern int32_t __REVSH(int32_t value);

-#else /* (__ARMCC_VERSION >= 400677) */

-static __INLINE __ASM int32_t __REVSH(int32_t value)

+static __attribute__((section(".revsh_text"))) __INLINE __ASM int32_t __REVSH(int32_t value)

{

revsh r0, r0

bx lr

}

-#endif /* __ARMCC_VERSION */

#if (__CORTEX_M >= 0x03)

@@ -218,11 +215,7 @@

This function removes the exclusive lock which is created by LDREX.

*/

-#if (__ARMCC_VERSION < 400000)

-extern void __CLREX(void);

-#else /* (__ARMCC_VERSION >= 400000) */

#define __CLREX __clrex

-#endif /* __ARMCC_VERSION */

/** \brief Signed Saturate

@@ -260,196 +253,13 @@

-#elif (defined (__ICCARM__)) /*---------------- ICC Compiler ---------------------*/

+#elif defined ( __ICCARM__ ) /*------------------ ICC Compiler -------------------*/

/* IAR iccarm specific functions */

-#include <intrinsics.h> /* IAR Intrinsics */

-

-#pragma diag_suppress=Pe940

-

-/** \brief No Operation

-

- No Operation does nothing. This instruction can be used for code alignment purposes.

- */

-#define __NOP __no_operation

-

-

-/** \brief Wait For Interrupt

-

- Wait For Interrupt is a hint instruction that suspends execution

- until one of a number of events occurs.

- */

-static __INLINE void __WFI(void)

-{

- __ASM ("wfi");

-}

-

-

-/** \brief Wait For Event

-

- Wait For Event is a hint instruction that permits the processor to enter

- a low-power state until one of a number of events occurs.

- */

-static __INLINE void __WFE(void)

-{

- __ASM ("wfe");

-}

-

-

-/** \brief Send Event

-

- Send Event is a hint instruction. It causes an event to be signaled to the CPU.

- */

-static __INLINE void __SEV(void)

-{

- __ASM ("sev");

-}

-

-

-/* intrinsic void __ISB(void) (see intrinsics.h) */

-/* intrinsic void __DSB(void) (see intrinsics.h) */

-/* intrinsic void __DMB(void) (see intrinsics.h) */

-/* intrinsic uint32_t __REV(uint32_t value) (see intrinsics.h) */

-/* intrinsic __SSAT (see intrinsics.h) */

-/* intrinsic __USAT (see intrinsics.h) */

-

-

-/** \brief Reverse byte order (16 bit)

-

- This function reverses the byte order in two unsigned short values.

-

- \param [in] value Value to reverse

- \return Reversed value

- */

-static uint32_t __REV16(uint32_t value)

-{

- __ASM("rev16 r0, r0");

-}

-

-

-/* intrinsic uint32_t __REVSH(uint32_t value) (see intrinsics.h */

-

-

-#if (__CORTEX_M >= 0x03)

-

-/** \brief Reverse bit order of value

-

- This function reverses the bit order of the given value.

-

- \param [in] value Value to reverse

- \return Reversed value

- */

-static uint32_t __RBIT(uint32_t value)

-{

- __ASM("rbit r0, r0");

-}

+#include <cmsis_iar.h>

-/** \brief LDR Exclusive (8 bit)

-

- This function performs a exclusive LDR command for 8 bit value.

-

- \param [in] ptr Pointer to data

- \return value of type uint8_t at (*ptr)

- */

-static uint8_t __LDREXB(volatile uint8_t *addr)

-{

- __ASM("ldrexb r0, [r0]");

-}

-

-

-/** \brief LDR Exclusive (16 bit)

-

- This function performs a exclusive LDR command for 16 bit values.

-

- \param [in] ptr Pointer to data

- \return value of type uint16_t at (*ptr)

- */

-static uint16_t __LDREXH(volatile uint16_t *addr)

-{

- __ASM("ldrexh r0, [r0]");

-}

-

-

-/** \brief LDR Exclusive (32 bit)

-

- This function performs a exclusive LDR command for 32 bit values.

-

- \param [in] ptr Pointer to data

- \return value of type uint32_t at (*ptr)

- */

-/* intrinsic unsigned long __LDREX(unsigned long *) (see intrinsics.h) */

-static uint32_t __LDREXW(volatile uint32_t *addr)

-{

- __ASM("ldrex r0, [r0]");

-}

-

-

-/** \brief STR Exclusive (8 bit)

-

- This function performs a exclusive STR command for 8 bit values.

-

- \param [in] value Value to store

- \param [in] ptr Pointer to location

- \return 0 Function succeeded

- \return 1 Function failed

- */

-static uint32_t __STREXB(uint8_t value, volatile uint8_t *addr)

-{

- __ASM("strexb r0, r0, [r1]");

-}

-

-

-/** \brief STR Exclusive (16 bit)

-

- This function performs a exclusive STR command for 16 bit values.

-

- \param [in] value Value to store

- \param [in] ptr Pointer to location

- \return 0 Function succeeded

- \return 1 Function failed

- */

-static uint32_t __STREXH(uint16_t value, volatile uint16_t *addr)

-{

- __ASM("strexh r0, r0, [r1]");

-}

-

-

-/** \brief STR Exclusive (32 bit)

-

- This function performs a exclusive STR command for 32 bit values.

-

- \param [in] value Value to store

- \param [in] ptr Pointer to location

- \return 0 Function succeeded

- \return 1 Function failed

- */

-/* intrinsic unsigned long __STREX(unsigned long, unsigned long) (see intrinsics.h )*/

-static uint32_t __STREXW(uint32_t value, volatile uint32_t *addr)

-{

- __ASM("strex r0, r0, [r1]");

-}

-

-

-/** \brief Remove the exclusive lock

-

- This function removes the exclusive lock which is created by LDREX.

-

- */

-static __INLINE void __CLREX(void)

-{

- __ASM ("clrex");

-}

-

-/* intrinsic unsigned char __CLZ( unsigned long ) (see intrinsics.h) */

-

-#endif /* (__CORTEX_M >= 0x03) */

-

-#pragma diag_default=Pe940

-

-

-

-#elif (defined (__GNUC__)) /*------------------ GNU Compiler ---------------------*/

+#elif defined ( __GNUC__ ) /*------------------ GNU Compiler ---------------------*/

/* GNU gcc specific functions */

/** \brief No Operation

@@ -655,7 +465,7 @@

{

uint32_t result;

- __ASM volatile ("strexb %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );

+ __ASM volatile ("strexb %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );

return(result);

}

@@ -673,7 +483,7 @@

{

uint32_t result;

- __ASM volatile ("strexh %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );

+ __ASM volatile ("strexh %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );

return(result);

}

@@ -691,7 +501,7 @@

{

uint32_t result;

- __ASM volatile ("strex %0, %2, [%1]" : "=r" (result) : "r" (addr), "r" (value) );

+ __ASM volatile ("strex %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );

return(result);

}

@@ -759,12 +569,12 @@

-#elif (defined (__TASKING__)) /*--------------- TASKING Compiler -----------------*/

+#elif defined ( __TASKING__ ) /*------------------ TASKING Compiler --------------*/

/* TASKING carm specific functions */

/*

* The CMSIS functions have been implemented as intrinsics in the compiler.

- * Please use "carm -?i" to get an up to date list of all instrinsics,

+ * Please use "carm -?i" to get an up to date list of all intrinsics,

* Including the CMSIS ones.

*/

@@ -772,4 +582,4 @@

/*@}*/ /* end of group CMSIS_Core_InstructionInterface */

-#endif /* __CORE_CMINSTR_H__ */

+#endif /* __CORE_CMINSTR_H */