Lib for FTDI FT800 Graphic Controller EVE Support up to 512 x 512 pixel resolution. Resistive touch sense Mono audio output SPI Interface

Dependents: FT800_touch_track FT800_JPG

Library for the FT800 Display,Audio and Touch Controller from FTDI. The Code is based on the sample code from FTDI.

FT800 is a graphics chip with added features such as audio playback and touch capabilities. FT800 graphics consist of a rich set of graphics objects (primitive and widgets) that can be used for displaying various menus and screen shots.

http://www.ftdichip.com/Products/ICs/FT800.html

The mbed is talking thru the SPI interface with the graphic engine. We have to set up a list of Commands and send them to the FT800 to get graphics.

Hardware

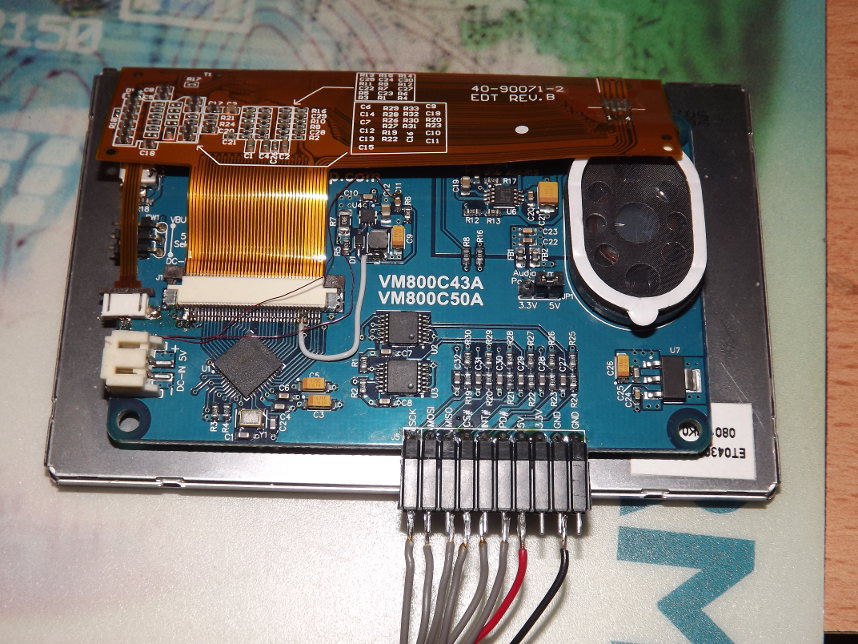

1. VM800C development modules from FTDI : http://www.ftdichip.com/Products/Modules/VM800C.html

The modules come with different size lcd. 3.5", 4.3" or 5" or without.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

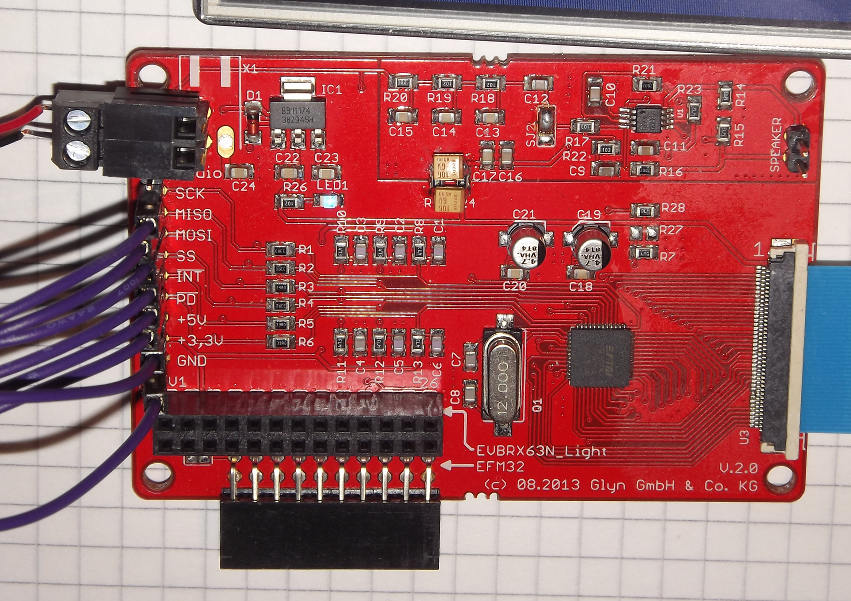

2. EVBEVE-FT800 board from GLYN: http://www.glyn.com/News-Events/Newsletter/Newsletter-2013/October-2013/A-quick-start-for-EVE-Requires-no-basic-knowledge-graphics-sound-and-touch-can-all-be-learned-in-minutes

The module has a 40 pin flex cable connector to connect a display out of the EDT series.

The mbed is connected via the pin header on the left. If you use this board with a EDT display you have to uncomment the #define Inv_Backlite in FT_LCD_Type.h, because the backlight dimming is inverted.

3. ConnectEVE board from MikroElektronika http://www.mikroe.com/add-on-boards/display/connecteve/#headers_10 The board has also a pin header to connect the mbed. - not tested, but it looks like the other boards.

Connection

We need 5 signals to connect to the mbed. SCK, MOSI and MISO are connected to a SPI channel. SS is the chip select signal and PD work as powerdown. The additional INT signal is not used at the moment. It is possible to generate a interrupt signal, but at the moment you have to poll the status register of the FT800 to see if a command is finished.

Software

This lib is based on the demo code from FTDI. If you want to use it, you have to read the programming manual : http://www.ftdichip.com/Support/Documents/ProgramGuides/FT800%20Programmers%20Guide.pdf

See my demo : http://mbed.org/users/dreschpe/code/FT800_touch_track/

or the demo code from FTDI : http://www.ftdichip.com/Support/SoftwareExamples/EVE/FT800_SampleApp_1.0.zip

FT_CoPro_Cmds.cpp@0:5e013296b353, 2014-01-03 (annotated)

- Committer:

- dreschpe

- Date:

- Fri Jan 03 15:26:10 2014 +0000

- Revision:

- 0:5e013296b353

- Child:

- 2:ab74a9a05970

Lib for FTDI FT800 Graphic Controller EVE

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dreschpe | 0:5e013296b353 | 1 | |

| dreschpe | 0:5e013296b353 | 2 | #include "FT_Platform.h" |

| dreschpe | 0:5e013296b353 | 3 | //#include "FT_Gpu_Hal.h" |

| dreschpe | 0:5e013296b353 | 4 | |

| dreschpe | 0:5e013296b353 | 5 | |

| dreschpe | 0:5e013296b353 | 6 | ft_void_t FT800::Ft_Gpu_Copro_SendCmd( ft_uint32_t cmd) |

| dreschpe | 0:5e013296b353 | 7 | { |

| dreschpe | 0:5e013296b353 | 8 | Ft_Gpu_Hal_Transfer32( cmd); |

| dreschpe | 0:5e013296b353 | 9 | } |

| dreschpe | 0:5e013296b353 | 10 | |

| dreschpe | 0:5e013296b353 | 11 | ft_void_t FT800::Ft_Gpu_CoCmd_SendStr( const ft_char8_t *s) |

| dreschpe | 0:5e013296b353 | 12 | { |

| dreschpe | 0:5e013296b353 | 13 | Ft_Gpu_Hal_TransferString( s); |

| dreschpe | 0:5e013296b353 | 14 | } |

| dreschpe | 0:5e013296b353 | 15 | |

| dreschpe | 0:5e013296b353 | 16 | |

| dreschpe | 0:5e013296b353 | 17 | ft_void_t FT800::Ft_Gpu_CoCmd_StartFunc( ft_uint16_t count) |

| dreschpe | 0:5e013296b353 | 18 | { |

| dreschpe | 0:5e013296b353 | 19 | Ft_Gpu_Hal_CheckCmdBuffer( count); |

| dreschpe | 0:5e013296b353 | 20 | Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_WRITE,count); |

| dreschpe | 0:5e013296b353 | 21 | } |

| dreschpe | 0:5e013296b353 | 22 | |

| dreschpe | 0:5e013296b353 | 23 | ft_void_t FT800::Ft_Gpu_CoCmd_EndFunc( ft_uint16_t count) |

| dreschpe | 0:5e013296b353 | 24 | { |

| dreschpe | 0:5e013296b353 | 25 | Ft_Gpu_Hal_EndTransfer( ); |

| dreschpe | 0:5e013296b353 | 26 | Ft_Gpu_Hal_Updatecmdfifo( count); |

| dreschpe | 0:5e013296b353 | 27 | } |

| dreschpe | 0:5e013296b353 | 28 | |

| dreschpe | 0:5e013296b353 | 29 | ft_void_t FT800::Ft_Gpu_CoCmd_Text( ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s) |

| dreschpe | 0:5e013296b353 | 30 | { |

| dreschpe | 0:5e013296b353 | 31 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3 + strlen(s) + 1); |

| dreschpe | 0:5e013296b353 | 32 | Ft_Gpu_Copro_SendCmd( CMD_TEXT); |

| dreschpe | 0:5e013296b353 | 33 | //Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(ft_uint32_t)x)); |

| dreschpe | 0:5e013296b353 | 34 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 35 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|(ft_uint32_t)font)); |

| dreschpe | 0:5e013296b353 | 36 | Ft_Gpu_CoCmd_SendStr( s); |

| dreschpe | 0:5e013296b353 | 37 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3 + strlen(s) + 1)); |

| dreschpe | 0:5e013296b353 | 38 | } |

| dreschpe | 0:5e013296b353 | 39 | |

| dreschpe | 0:5e013296b353 | 40 | ft_void_t FT800::Ft_Gpu_CoCmd_Number( ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, ft_int32_t n) |

| dreschpe | 0:5e013296b353 | 41 | { |

| dreschpe | 0:5e013296b353 | 42 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4); |

| dreschpe | 0:5e013296b353 | 43 | Ft_Gpu_Copro_SendCmd( CMD_NUMBER); |

| dreschpe | 0:5e013296b353 | 44 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 45 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|font)); |

| dreschpe | 0:5e013296b353 | 46 | Ft_Gpu_Copro_SendCmd( n); |

| dreschpe | 0:5e013296b353 | 47 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4)); |

| dreschpe | 0:5e013296b353 | 48 | } |

| dreschpe | 0:5e013296b353 | 49 | |

| dreschpe | 0:5e013296b353 | 50 | ft_void_t FT800::Ft_Gpu_CoCmd_LoadIdentity( ) |

| dreschpe | 0:5e013296b353 | 51 | { |

| dreschpe | 0:5e013296b353 | 52 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 53 | Ft_Gpu_Copro_SendCmd( CMD_LOADIDENTITY); |

| dreschpe | 0:5e013296b353 | 54 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1)); |

| dreschpe | 0:5e013296b353 | 55 | } |

| dreschpe | 0:5e013296b353 | 56 | |

| dreschpe | 0:5e013296b353 | 57 | ft_void_t FT800::Ft_Gpu_CoCmd_Toggle( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t font, ft_uint16_t options, ft_uint16_t state, const ft_char8_t* s) |

| dreschpe | 0:5e013296b353 | 58 | { |

| dreschpe | 0:5e013296b353 | 59 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4 + strlen(s) + 1); |

| dreschpe | 0:5e013296b353 | 60 | Ft_Gpu_Copro_SendCmd( CMD_TOGGLE); |

| dreschpe | 0:5e013296b353 | 61 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 62 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)font<<16)|w)); |

| dreschpe | 0:5e013296b353 | 63 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)state<<16)|options)); |

| dreschpe | 0:5e013296b353 | 64 | Ft_Gpu_CoCmd_SendStr( s); |

| dreschpe | 0:5e013296b353 | 65 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4 + strlen(s) + 1)); |

| dreschpe | 0:5e013296b353 | 66 | } |

| dreschpe | 0:5e013296b353 | 67 | |

| dreschpe | 0:5e013296b353 | 68 | /* Error handling for val is not done, so better to always use range of 65535 in order that needle is drawn within display region */ |

| dreschpe | 0:5e013296b353 | 69 | ft_void_t FT800::Ft_Gpu_CoCmd_Gauge( ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t major, ft_uint16_t minor, ft_uint16_t val, ft_uint16_t range) |

| dreschpe | 0:5e013296b353 | 70 | { |

| dreschpe | 0:5e013296b353 | 71 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5); |

| dreschpe | 0:5e013296b353 | 72 | Ft_Gpu_Copro_SendCmd( CMD_GAUGE); |

| dreschpe | 0:5e013296b353 | 73 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 74 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|r)); |

| dreschpe | 0:5e013296b353 | 75 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)minor<<16)|major)); |

| dreschpe | 0:5e013296b353 | 76 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)range<<16)|val)); |

| dreschpe | 0:5e013296b353 | 77 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5)); |

| dreschpe | 0:5e013296b353 | 78 | } |

| dreschpe | 0:5e013296b353 | 79 | |

| dreschpe | 0:5e013296b353 | 80 | ft_void_t FT800::Ft_Gpu_CoCmd_RegRead( ft_uint32_t ptr, ft_uint32_t result) |

| dreschpe | 0:5e013296b353 | 81 | { |

| dreschpe | 0:5e013296b353 | 82 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 83 | Ft_Gpu_Copro_SendCmd( CMD_REGREAD); |

| dreschpe | 0:5e013296b353 | 84 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 85 | Ft_Gpu_Copro_SendCmd( 0); |

| dreschpe | 0:5e013296b353 | 86 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 87 | |

| dreschpe | 0:5e013296b353 | 88 | } |

| dreschpe | 0:5e013296b353 | 89 | |

| dreschpe | 0:5e013296b353 | 90 | ft_void_t FT800::Ft_Gpu_CoCmd_GetProps( ft_uint32_t ptr, ft_uint32_t w, ft_uint32_t h) |

| dreschpe | 0:5e013296b353 | 91 | { |

| dreschpe | 0:5e013296b353 | 92 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4); |

| dreschpe | 0:5e013296b353 | 93 | Ft_Gpu_Copro_SendCmd( CMD_GETPROPS); |

| dreschpe | 0:5e013296b353 | 94 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 95 | Ft_Gpu_Copro_SendCmd( w); |

| dreschpe | 0:5e013296b353 | 96 | Ft_Gpu_Copro_SendCmd( h); |

| dreschpe | 0:5e013296b353 | 97 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4)); |

| dreschpe | 0:5e013296b353 | 98 | } |

| dreschpe | 0:5e013296b353 | 99 | |

| dreschpe | 0:5e013296b353 | 100 | ft_void_t FT800::Ft_Gpu_CoCmd_Memcpy( ft_uint32_t dest, ft_uint32_t src, ft_uint32_t num) |

| dreschpe | 0:5e013296b353 | 101 | { |

| dreschpe | 0:5e013296b353 | 102 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4); |

| dreschpe | 0:5e013296b353 | 103 | Ft_Gpu_Copro_SendCmd( CMD_MEMCPY); |

| dreschpe | 0:5e013296b353 | 104 | Ft_Gpu_Copro_SendCmd( dest); |

| dreschpe | 0:5e013296b353 | 105 | Ft_Gpu_Copro_SendCmd( src); |

| dreschpe | 0:5e013296b353 | 106 | Ft_Gpu_Copro_SendCmd( num); |

| dreschpe | 0:5e013296b353 | 107 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4)); |

| dreschpe | 0:5e013296b353 | 108 | } |

| dreschpe | 0:5e013296b353 | 109 | |

| dreschpe | 0:5e013296b353 | 110 | ft_void_t FT800::Ft_Gpu_CoCmd_Spinner( ft_int16_t x, ft_int16_t y, ft_uint16_t style, ft_uint16_t scale) |

| dreschpe | 0:5e013296b353 | 111 | { |

| dreschpe | 0:5e013296b353 | 112 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 113 | Ft_Gpu_Copro_SendCmd( CMD_SPINNER); |

| dreschpe | 0:5e013296b353 | 114 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 115 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)scale<<16)|style)); |

| dreschpe | 0:5e013296b353 | 116 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 117 | } |

| dreschpe | 0:5e013296b353 | 118 | |

| dreschpe | 0:5e013296b353 | 119 | ft_void_t FT800::Ft_Gpu_CoCmd_BgColor( ft_uint32_t c) |

| dreschpe | 0:5e013296b353 | 120 | { |

| dreschpe | 0:5e013296b353 | 121 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 122 | Ft_Gpu_Copro_SendCmd( CMD_BGCOLOR); |

| dreschpe | 0:5e013296b353 | 123 | Ft_Gpu_Copro_SendCmd( c); |

| dreschpe | 0:5e013296b353 | 124 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 125 | } |

| dreschpe | 0:5e013296b353 | 126 | |

| dreschpe | 0:5e013296b353 | 127 | ft_void_t FT800::Ft_Gpu_CoCmd_Swap() |

| dreschpe | 0:5e013296b353 | 128 | { |

| dreschpe | 0:5e013296b353 | 129 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 130 | Ft_Gpu_Copro_SendCmd( CMD_SWAP); |

| dreschpe | 0:5e013296b353 | 131 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1)); |

| dreschpe | 0:5e013296b353 | 132 | } |

| dreschpe | 0:5e013296b353 | 133 | |

| dreschpe | 0:5e013296b353 | 134 | ft_void_t FT800::Ft_Gpu_CoCmd_Inflate( ft_uint32_t ptr) |

| dreschpe | 0:5e013296b353 | 135 | { |

| dreschpe | 0:5e013296b353 | 136 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 137 | Ft_Gpu_Copro_SendCmd( CMD_INFLATE); |

| dreschpe | 0:5e013296b353 | 138 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 139 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 140 | } |

| dreschpe | 0:5e013296b353 | 141 | |

| dreschpe | 0:5e013296b353 | 142 | ft_void_t FT800::Ft_Gpu_CoCmd_Translate( ft_int32_t tx, ft_int32_t ty) |

| dreschpe | 0:5e013296b353 | 143 | { |

| dreschpe | 0:5e013296b353 | 144 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 145 | Ft_Gpu_Copro_SendCmd( CMD_TRANSLATE); |

| dreschpe | 0:5e013296b353 | 146 | Ft_Gpu_Copro_SendCmd( tx); |

| dreschpe | 0:5e013296b353 | 147 | Ft_Gpu_Copro_SendCmd( ty); |

| dreschpe | 0:5e013296b353 | 148 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 149 | } |

| dreschpe | 0:5e013296b353 | 150 | |

| dreschpe | 0:5e013296b353 | 151 | ft_void_t FT800::Ft_Gpu_CoCmd_Stop() |

| dreschpe | 0:5e013296b353 | 152 | { |

| dreschpe | 0:5e013296b353 | 153 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 154 | Ft_Gpu_Copro_SendCmd( CMD_STOP); |

| dreschpe | 0:5e013296b353 | 155 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1)); |

| dreschpe | 0:5e013296b353 | 156 | } |

| dreschpe | 0:5e013296b353 | 157 | |

| dreschpe | 0:5e013296b353 | 158 | ft_void_t FT800::Ft_Gpu_CoCmd_Slider( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range) |

| dreschpe | 0:5e013296b353 | 159 | { |

| dreschpe | 0:5e013296b353 | 160 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5); |

| dreschpe | 0:5e013296b353 | 161 | Ft_Gpu_Copro_SendCmd( CMD_SLIDER); |

| dreschpe | 0:5e013296b353 | 162 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 163 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w)); |

| dreschpe | 0:5e013296b353 | 164 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)val<<16)|options)); |

| dreschpe | 0:5e013296b353 | 165 | Ft_Gpu_Copro_SendCmd( range); |

| dreschpe | 0:5e013296b353 | 166 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5)); |

| dreschpe | 0:5e013296b353 | 167 | } |

| dreschpe | 0:5e013296b353 | 168 | |

| dreschpe | 0:5e013296b353 | 169 | ft_void_t FT800::Ft_Gpu_CoCmd_TouchTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result) |

| dreschpe | 0:5e013296b353 | 170 | { |

| dreschpe | 0:5e013296b353 | 171 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*6*2+FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 172 | Ft_Gpu_Copro_SendCmd( CMD_TOUCH_TRANSFORM); |

| dreschpe | 0:5e013296b353 | 173 | Ft_Gpu_Copro_SendCmd( x0); |

| dreschpe | 0:5e013296b353 | 174 | Ft_Gpu_Copro_SendCmd( y0); |

| dreschpe | 0:5e013296b353 | 175 | Ft_Gpu_Copro_SendCmd( x1); |

| dreschpe | 0:5e013296b353 | 176 | Ft_Gpu_Copro_SendCmd( y1); |

| dreschpe | 0:5e013296b353 | 177 | Ft_Gpu_Copro_SendCmd( x2); |

| dreschpe | 0:5e013296b353 | 178 | Ft_Gpu_Copro_SendCmd( y2); |

| dreschpe | 0:5e013296b353 | 179 | Ft_Gpu_Copro_SendCmd( tx0); |

| dreschpe | 0:5e013296b353 | 180 | Ft_Gpu_Copro_SendCmd( ty0); |

| dreschpe | 0:5e013296b353 | 181 | Ft_Gpu_Copro_SendCmd( tx1); |

| dreschpe | 0:5e013296b353 | 182 | Ft_Gpu_Copro_SendCmd( ty1); |

| dreschpe | 0:5e013296b353 | 183 | Ft_Gpu_Copro_SendCmd( tx2); |

| dreschpe | 0:5e013296b353 | 184 | Ft_Gpu_Copro_SendCmd( ty2); |

| dreschpe | 0:5e013296b353 | 185 | Ft_Gpu_Copro_SendCmd( result); |

| dreschpe | 0:5e013296b353 | 186 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*6*2+FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 187 | } |

| dreschpe | 0:5e013296b353 | 188 | |

| dreschpe | 0:5e013296b353 | 189 | ft_void_t FT800::Ft_Gpu_CoCmd_Interrupt( ft_uint32_t ms) |

| dreschpe | 0:5e013296b353 | 190 | { |

| dreschpe | 0:5e013296b353 | 191 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 192 | Ft_Gpu_Copro_SendCmd( CMD_INTERRUPT); |

| dreschpe | 0:5e013296b353 | 193 | Ft_Gpu_Copro_SendCmd( ms); |

| dreschpe | 0:5e013296b353 | 194 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 195 | } |

| dreschpe | 0:5e013296b353 | 196 | |

| dreschpe | 0:5e013296b353 | 197 | ft_void_t FT800::Ft_Gpu_CoCmd_FgColor( ft_uint32_t c) |

| dreschpe | 0:5e013296b353 | 198 | { |

| dreschpe | 0:5e013296b353 | 199 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 200 | Ft_Gpu_Copro_SendCmd( CMD_FGCOLOR); |

| dreschpe | 0:5e013296b353 | 201 | Ft_Gpu_Copro_SendCmd( c); |

| dreschpe | 0:5e013296b353 | 202 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 203 | } |

| dreschpe | 0:5e013296b353 | 204 | |

| dreschpe | 0:5e013296b353 | 205 | ft_void_t FT800::Ft_Gpu_CoCmd_Rotate( ft_int32_t a) |

| dreschpe | 0:5e013296b353 | 206 | { |

| dreschpe | 0:5e013296b353 | 207 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 208 | Ft_Gpu_Copro_SendCmd( CMD_ROTATE); |

| dreschpe | 0:5e013296b353 | 209 | Ft_Gpu_Copro_SendCmd( a); |

| dreschpe | 0:5e013296b353 | 210 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 211 | } |

| dreschpe | 0:5e013296b353 | 212 | |

| dreschpe | 0:5e013296b353 | 213 | ft_void_t FT800::Ft_Gpu_CoCmd_Button( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s) |

| dreschpe | 0:5e013296b353 | 214 | { |

| dreschpe | 0:5e013296b353 | 215 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4 + strlen(s) + 1); |

| dreschpe | 0:5e013296b353 | 216 | Ft_Gpu_Copro_SendCmd( CMD_BUTTON); |

| dreschpe | 0:5e013296b353 | 217 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 218 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w)); |

| dreschpe | 0:5e013296b353 | 219 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|font)); |

| dreschpe | 0:5e013296b353 | 220 | Ft_Gpu_CoCmd_SendStr( s); |

| dreschpe | 0:5e013296b353 | 221 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4 + strlen(s) + 1)); |

| dreschpe | 0:5e013296b353 | 222 | } |

| dreschpe | 0:5e013296b353 | 223 | |

| dreschpe | 0:5e013296b353 | 224 | ft_void_t FT800::Ft_Gpu_CoCmd_MemWrite( ft_uint32_t ptr, ft_uint32_t num) |

| dreschpe | 0:5e013296b353 | 225 | { |

| dreschpe | 0:5e013296b353 | 226 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 227 | Ft_Gpu_Copro_SendCmd( CMD_MEMWRITE); |

| dreschpe | 0:5e013296b353 | 228 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 229 | Ft_Gpu_Copro_SendCmd( num); |

| dreschpe | 0:5e013296b353 | 230 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 231 | } |

| dreschpe | 0:5e013296b353 | 232 | |

| dreschpe | 0:5e013296b353 | 233 | ft_void_t FT800::Ft_Gpu_CoCmd_Scrollbar( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t size, ft_uint16_t range) |

| dreschpe | 0:5e013296b353 | 234 | { |

| dreschpe | 0:5e013296b353 | 235 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5); |

| dreschpe | 0:5e013296b353 | 236 | Ft_Gpu_Copro_SendCmd( CMD_SCROLLBAR); |

| dreschpe | 0:5e013296b353 | 237 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 238 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w)); |

| dreschpe | 0:5e013296b353 | 239 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)val<<16)|options)); |

| dreschpe | 0:5e013296b353 | 240 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)range<<16)|size)); |

| dreschpe | 0:5e013296b353 | 241 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5)); |

| dreschpe | 0:5e013296b353 | 242 | } |

| dreschpe | 0:5e013296b353 | 243 | |

| dreschpe | 0:5e013296b353 | 244 | ft_void_t FT800::Ft_Gpu_CoCmd_GetMatrix( ft_int32_t a, ft_int32_t b, ft_int32_t c, ft_int32_t d, ft_int32_t e, ft_int32_t f) |

| dreschpe | 0:5e013296b353 | 245 | { |

| dreschpe | 0:5e013296b353 | 246 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*7); |

| dreschpe | 0:5e013296b353 | 247 | Ft_Gpu_Copro_SendCmd( CMD_GETMATRIX); |

| dreschpe | 0:5e013296b353 | 248 | Ft_Gpu_Copro_SendCmd( a); |

| dreschpe | 0:5e013296b353 | 249 | Ft_Gpu_Copro_SendCmd( b); |

| dreschpe | 0:5e013296b353 | 250 | Ft_Gpu_Copro_SendCmd( c); |

| dreschpe | 0:5e013296b353 | 251 | Ft_Gpu_Copro_SendCmd( d); |

| dreschpe | 0:5e013296b353 | 252 | Ft_Gpu_Copro_SendCmd( e); |

| dreschpe | 0:5e013296b353 | 253 | Ft_Gpu_Copro_SendCmd( f); |

| dreschpe | 0:5e013296b353 | 254 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*7)); |

| dreschpe | 0:5e013296b353 | 255 | } |

| dreschpe | 0:5e013296b353 | 256 | |

| dreschpe | 0:5e013296b353 | 257 | ft_void_t FT800::Ft_Gpu_CoCmd_Sketch( ft_int16_t x, ft_int16_t y, ft_uint16_t w, ft_uint16_t h, ft_uint32_t ptr, ft_uint16_t format) |

| dreschpe | 0:5e013296b353 | 258 | { |

| dreschpe | 0:5e013296b353 | 259 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5); |

| dreschpe | 0:5e013296b353 | 260 | Ft_Gpu_Copro_SendCmd( CMD_SKETCH); |

| dreschpe | 0:5e013296b353 | 261 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 262 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w)); |

| dreschpe | 0:5e013296b353 | 263 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 264 | Ft_Gpu_Copro_SendCmd( format); |

| dreschpe | 0:5e013296b353 | 265 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5)); |

| dreschpe | 0:5e013296b353 | 266 | } |

| dreschpe | 0:5e013296b353 | 267 | ft_void_t FT800::Ft_Gpu_CoCmd_MemSet( ft_uint32_t ptr, ft_uint32_t value, ft_uint32_t num) |

| dreschpe | 0:5e013296b353 | 268 | { |

| dreschpe | 0:5e013296b353 | 269 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4); |

| dreschpe | 0:5e013296b353 | 270 | Ft_Gpu_Copro_SendCmd( CMD_MEMSET); |

| dreschpe | 0:5e013296b353 | 271 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 272 | Ft_Gpu_Copro_SendCmd( value); |

| dreschpe | 0:5e013296b353 | 273 | Ft_Gpu_Copro_SendCmd( num); |

| dreschpe | 0:5e013296b353 | 274 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4)); |

| dreschpe | 0:5e013296b353 | 275 | } |

| dreschpe | 0:5e013296b353 | 276 | ft_void_t FT800::Ft_Gpu_CoCmd_GradColor( ft_uint32_t c) |

| dreschpe | 0:5e013296b353 | 277 | { |

| dreschpe | 0:5e013296b353 | 278 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 279 | Ft_Gpu_Copro_SendCmd( CMD_GRADCOLOR); |

| dreschpe | 0:5e013296b353 | 280 | Ft_Gpu_Copro_SendCmd( c); |

| dreschpe | 0:5e013296b353 | 281 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 282 | } |

| dreschpe | 0:5e013296b353 | 283 | ft_void_t FT800::Ft_Gpu_CoCmd_BitmapTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result) |

| dreschpe | 0:5e013296b353 | 284 | { |

| dreschpe | 0:5e013296b353 | 285 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*6*2+FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 286 | Ft_Gpu_Copro_SendCmd( CMD_BITMAP_TRANSFORM); |

| dreschpe | 0:5e013296b353 | 287 | Ft_Gpu_Copro_SendCmd( x0); |

| dreschpe | 0:5e013296b353 | 288 | Ft_Gpu_Copro_SendCmd( y0); |

| dreschpe | 0:5e013296b353 | 289 | Ft_Gpu_Copro_SendCmd( x1); |

| dreschpe | 0:5e013296b353 | 290 | Ft_Gpu_Copro_SendCmd( y1); |

| dreschpe | 0:5e013296b353 | 291 | Ft_Gpu_Copro_SendCmd( x2); |

| dreschpe | 0:5e013296b353 | 292 | Ft_Gpu_Copro_SendCmd( y2); |

| dreschpe | 0:5e013296b353 | 293 | Ft_Gpu_Copro_SendCmd( tx0); |

| dreschpe | 0:5e013296b353 | 294 | Ft_Gpu_Copro_SendCmd( ty0); |

| dreschpe | 0:5e013296b353 | 295 | Ft_Gpu_Copro_SendCmd( tx1); |

| dreschpe | 0:5e013296b353 | 296 | Ft_Gpu_Copro_SendCmd( ty1); |

| dreschpe | 0:5e013296b353 | 297 | Ft_Gpu_Copro_SendCmd( tx2); |

| dreschpe | 0:5e013296b353 | 298 | Ft_Gpu_Copro_SendCmd( ty2); |

| dreschpe | 0:5e013296b353 | 299 | Ft_Gpu_Copro_SendCmd( result); |

| dreschpe | 0:5e013296b353 | 300 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*6*2+FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 301 | } |

| dreschpe | 0:5e013296b353 | 302 | ft_void_t FT800::Ft_Gpu_CoCmd_Calibrate( ft_uint32_t result) |

| dreschpe | 0:5e013296b353 | 303 | { |

| dreschpe | 0:5e013296b353 | 304 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 305 | Ft_Gpu_Copro_SendCmd( CMD_CALIBRATE); |

| dreschpe | 0:5e013296b353 | 306 | Ft_Gpu_Copro_SendCmd( result); |

| dreschpe | 0:5e013296b353 | 307 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 308 | Ft_Gpu_Hal_WaitCmdfifo_empty( ); |

| dreschpe | 0:5e013296b353 | 309 | |

| dreschpe | 0:5e013296b353 | 310 | } |

| dreschpe | 0:5e013296b353 | 311 | ft_void_t FT800::Ft_Gpu_CoCmd_SetFont( ft_uint32_t font, ft_uint32_t ptr) |

| dreschpe | 0:5e013296b353 | 312 | { |

| dreschpe | 0:5e013296b353 | 313 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 314 | Ft_Gpu_Copro_SendCmd( CMD_SETFONT); |

| dreschpe | 0:5e013296b353 | 315 | Ft_Gpu_Copro_SendCmd( font); |

| dreschpe | 0:5e013296b353 | 316 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 317 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 318 | } |

| dreschpe | 0:5e013296b353 | 319 | ft_void_t FT800::Ft_Gpu_CoCmd_Logo( ) |

| dreschpe | 0:5e013296b353 | 320 | { |

| dreschpe | 0:5e013296b353 | 321 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 322 | Ft_Gpu_Copro_SendCmd( CMD_LOGO); |

| dreschpe | 0:5e013296b353 | 323 | Ft_Gpu_CoCmd_EndFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 324 | } |

| dreschpe | 0:5e013296b353 | 325 | ft_void_t FT800::Ft_Gpu_CoCmd_Append( ft_uint32_t ptr, ft_uint32_t num) |

| dreschpe | 0:5e013296b353 | 326 | { |

| dreschpe | 0:5e013296b353 | 327 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 328 | Ft_Gpu_Copro_SendCmd( CMD_APPEND); |

| dreschpe | 0:5e013296b353 | 329 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 330 | Ft_Gpu_Copro_SendCmd( num); |

| dreschpe | 0:5e013296b353 | 331 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 332 | } |

| dreschpe | 0:5e013296b353 | 333 | ft_void_t FT800::Ft_Gpu_CoCmd_MemZero( ft_uint32_t ptr, ft_uint32_t num) |

| dreschpe | 0:5e013296b353 | 334 | { |

| dreschpe | 0:5e013296b353 | 335 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 336 | Ft_Gpu_Copro_SendCmd( CMD_MEMZERO); |

| dreschpe | 0:5e013296b353 | 337 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 338 | Ft_Gpu_Copro_SendCmd( num); |

| dreschpe | 0:5e013296b353 | 339 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 340 | } |

| dreschpe | 0:5e013296b353 | 341 | ft_void_t FT800::Ft_Gpu_CoCmd_Scale( ft_int32_t sx, ft_int32_t sy) |

| dreschpe | 0:5e013296b353 | 342 | { |

| dreschpe | 0:5e013296b353 | 343 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 344 | Ft_Gpu_Copro_SendCmd( CMD_SCALE); |

| dreschpe | 0:5e013296b353 | 345 | Ft_Gpu_Copro_SendCmd( sx); |

| dreschpe | 0:5e013296b353 | 346 | Ft_Gpu_Copro_SendCmd( sy); |

| dreschpe | 0:5e013296b353 | 347 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 348 | } |

| dreschpe | 0:5e013296b353 | 349 | ft_void_t FT800::Ft_Gpu_CoCmd_Clock( ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t h, ft_uint16_t m, ft_uint16_t s, ft_uint16_t ms) |

| dreschpe | 0:5e013296b353 | 350 | { |

| dreschpe | 0:5e013296b353 | 351 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5); |

| dreschpe | 0:5e013296b353 | 352 | Ft_Gpu_Copro_SendCmd( CMD_CLOCK); |

| dreschpe | 0:5e013296b353 | 353 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 354 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|r)); |

| dreschpe | 0:5e013296b353 | 355 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)m<<16)|h)); |

| dreschpe | 0:5e013296b353 | 356 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)ms<<16)|s)); |

| dreschpe | 0:5e013296b353 | 357 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5)); |

| dreschpe | 0:5e013296b353 | 358 | } |

| dreschpe | 0:5e013296b353 | 359 | |

| dreschpe | 0:5e013296b353 | 360 | ft_void_t FT800::Ft_Gpu_CoCmd_Gradient( ft_int16_t x0, ft_int16_t y0, ft_uint32_t rgb0, ft_int16_t x1, ft_int16_t y1, ft_uint32_t rgb1) |

| dreschpe | 0:5e013296b353 | 361 | { |

| dreschpe | 0:5e013296b353 | 362 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5); |

| dreschpe | 0:5e013296b353 | 363 | Ft_Gpu_Copro_SendCmd( CMD_GRADIENT); |

| dreschpe | 0:5e013296b353 | 364 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y0<<16)|(x0 & 0xffff))); |

| dreschpe | 0:5e013296b353 | 365 | Ft_Gpu_Copro_SendCmd( rgb0); |

| dreschpe | 0:5e013296b353 | 366 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y1<<16)|(x1 & 0xffff))); |

| dreschpe | 0:5e013296b353 | 367 | Ft_Gpu_Copro_SendCmd( rgb1); |

| dreschpe | 0:5e013296b353 | 368 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5)); |

| dreschpe | 0:5e013296b353 | 369 | } |

| dreschpe | 0:5e013296b353 | 370 | |

| dreschpe | 0:5e013296b353 | 371 | ft_void_t FT800::Ft_Gpu_CoCmd_SetMatrix( ) |

| dreschpe | 0:5e013296b353 | 372 | { |

| dreschpe | 0:5e013296b353 | 373 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 374 | Ft_Gpu_Copro_SendCmd( CMD_SETMATRIX); |

| dreschpe | 0:5e013296b353 | 375 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1)); |

| dreschpe | 0:5e013296b353 | 376 | } |

| dreschpe | 0:5e013296b353 | 377 | |

| dreschpe | 0:5e013296b353 | 378 | ft_void_t FT800::Ft_Gpu_CoCmd_Track( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t tag) |

| dreschpe | 0:5e013296b353 | 379 | { |

| dreschpe | 0:5e013296b353 | 380 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4); |

| dreschpe | 0:5e013296b353 | 381 | Ft_Gpu_Copro_SendCmd( CMD_TRACK); |

| dreschpe | 0:5e013296b353 | 382 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 383 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w)); |

| dreschpe | 0:5e013296b353 | 384 | Ft_Gpu_Copro_SendCmd( tag); |

| dreschpe | 0:5e013296b353 | 385 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4)); |

| dreschpe | 0:5e013296b353 | 386 | } |

| dreschpe | 0:5e013296b353 | 387 | |

| dreschpe | 0:5e013296b353 | 388 | ft_void_t FT800::Ft_Gpu_CoCmd_GetPtr( ft_uint32_t result) |

| dreschpe | 0:5e013296b353 | 389 | { |

| dreschpe | 0:5e013296b353 | 390 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 391 | Ft_Gpu_Copro_SendCmd( CMD_GETPTR); |

| dreschpe | 0:5e013296b353 | 392 | Ft_Gpu_Copro_SendCmd( result); |

| dreschpe | 0:5e013296b353 | 393 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 394 | } |

| dreschpe | 0:5e013296b353 | 395 | |

| dreschpe | 0:5e013296b353 | 396 | ft_void_t FT800::Ft_Gpu_CoCmd_Progress( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range) |

| dreschpe | 0:5e013296b353 | 397 | { |

| dreschpe | 0:5e013296b353 | 398 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5); |

| dreschpe | 0:5e013296b353 | 399 | Ft_Gpu_Copro_SendCmd( CMD_PROGRESS); |

| dreschpe | 0:5e013296b353 | 400 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 401 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w)); |

| dreschpe | 0:5e013296b353 | 402 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)val<<16)|options)); |

| dreschpe | 0:5e013296b353 | 403 | Ft_Gpu_Copro_SendCmd( range); |

| dreschpe | 0:5e013296b353 | 404 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5)); |

| dreschpe | 0:5e013296b353 | 405 | } |

| dreschpe | 0:5e013296b353 | 406 | |

| dreschpe | 0:5e013296b353 | 407 | ft_void_t FT800::Ft_Gpu_CoCmd_ColdStart( ) |

| dreschpe | 0:5e013296b353 | 408 | { |

| dreschpe | 0:5e013296b353 | 409 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 410 | Ft_Gpu_Copro_SendCmd( CMD_COLDSTART); |

| dreschpe | 0:5e013296b353 | 411 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1)); |

| dreschpe | 0:5e013296b353 | 412 | } |

| dreschpe | 0:5e013296b353 | 413 | |

| dreschpe | 0:5e013296b353 | 414 | ft_void_t FT800::Ft_Gpu_CoCmd_Keys( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s) |

| dreschpe | 0:5e013296b353 | 415 | { |

| dreschpe | 0:5e013296b353 | 416 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4 + strlen(s) + 1); |

| dreschpe | 0:5e013296b353 | 417 | Ft_Gpu_Copro_SendCmd( CMD_KEYS); |

| dreschpe | 0:5e013296b353 | 418 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 419 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w)); |

| dreschpe | 0:5e013296b353 | 420 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|font)); |

| dreschpe | 0:5e013296b353 | 421 | Ft_Gpu_CoCmd_SendStr( s); |

| dreschpe | 0:5e013296b353 | 422 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4 + strlen(s) + 1)); |

| dreschpe | 0:5e013296b353 | 423 | } |

| dreschpe | 0:5e013296b353 | 424 | |

| dreschpe | 0:5e013296b353 | 425 | ft_void_t FT800::Ft_Gpu_CoCmd_Dial( ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t val) |

| dreschpe | 0:5e013296b353 | 426 | { |

| dreschpe | 0:5e013296b353 | 427 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4); |

| dreschpe | 0:5e013296b353 | 428 | Ft_Gpu_Copro_SendCmd( CMD_DIAL); |

| dreschpe | 0:5e013296b353 | 429 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff))); |

| dreschpe | 0:5e013296b353 | 430 | Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|r)); |

| dreschpe | 0:5e013296b353 | 431 | Ft_Gpu_Copro_SendCmd( val); |

| dreschpe | 0:5e013296b353 | 432 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4)); |

| dreschpe | 0:5e013296b353 | 433 | } |

| dreschpe | 0:5e013296b353 | 434 | |

| dreschpe | 0:5e013296b353 | 435 | ft_void_t FT800::Ft_Gpu_CoCmd_LoadImage( ft_uint32_t ptr, ft_uint32_t options) |

| dreschpe | 0:5e013296b353 | 436 | { |

| dreschpe | 0:5e013296b353 | 437 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3); |

| dreschpe | 0:5e013296b353 | 438 | Ft_Gpu_Copro_SendCmd( CMD_LOADIMAGE); |

| dreschpe | 0:5e013296b353 | 439 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 440 | Ft_Gpu_Copro_SendCmd( options); |

| dreschpe | 0:5e013296b353 | 441 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3)); |

| dreschpe | 0:5e013296b353 | 442 | } |

| dreschpe | 0:5e013296b353 | 443 | |

| dreschpe | 0:5e013296b353 | 444 | ft_void_t FT800::Ft_Gpu_CoCmd_Dlstart( ) |

| dreschpe | 0:5e013296b353 | 445 | { |

| dreschpe | 0:5e013296b353 | 446 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 447 | Ft_Gpu_Copro_SendCmd( CMD_DLSTART); |

| dreschpe | 0:5e013296b353 | 448 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1)); |

| dreschpe | 0:5e013296b353 | 449 | } |

| dreschpe | 0:5e013296b353 | 450 | |

| dreschpe | 0:5e013296b353 | 451 | ft_void_t FT800::Ft_Gpu_CoCmd_Snapshot( ft_uint32_t ptr) |

| dreschpe | 0:5e013296b353 | 452 | { |

| dreschpe | 0:5e013296b353 | 453 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2); |

| dreschpe | 0:5e013296b353 | 454 | Ft_Gpu_Copro_SendCmd( CMD_SNAPSHOT); |

| dreschpe | 0:5e013296b353 | 455 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 456 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2)); |

| dreschpe | 0:5e013296b353 | 457 | } |

| dreschpe | 0:5e013296b353 | 458 | |

| dreschpe | 0:5e013296b353 | 459 | ft_void_t FT800::Ft_Gpu_CoCmd_ScreenSaver( ) |

| dreschpe | 0:5e013296b353 | 460 | { |

| dreschpe | 0:5e013296b353 | 461 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1); |

| dreschpe | 0:5e013296b353 | 462 | Ft_Gpu_Copro_SendCmd( CMD_SCREENSAVER); |

| dreschpe | 0:5e013296b353 | 463 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1)); |

| dreschpe | 0:5e013296b353 | 464 | } |

| dreschpe | 0:5e013296b353 | 465 | |

| dreschpe | 0:5e013296b353 | 466 | ft_void_t FT800::Ft_Gpu_CoCmd_MemCrc( ft_uint32_t ptr, ft_uint32_t num, ft_uint32_t result) |

| dreschpe | 0:5e013296b353 | 467 | { |

| dreschpe | 0:5e013296b353 | 468 | Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4); |

| dreschpe | 0:5e013296b353 | 469 | Ft_Gpu_Copro_SendCmd( CMD_MEMCRC); |

| dreschpe | 0:5e013296b353 | 470 | Ft_Gpu_Copro_SendCmd( ptr); |

| dreschpe | 0:5e013296b353 | 471 | Ft_Gpu_Copro_SendCmd( num); |

| dreschpe | 0:5e013296b353 | 472 | Ft_Gpu_Copro_SendCmd( result); |

| dreschpe | 0:5e013296b353 | 473 | Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4)); |

| dreschpe | 0:5e013296b353 | 474 | } |

| dreschpe | 0:5e013296b353 | 475 | |

| dreschpe | 0:5e013296b353 | 476 | |

| dreschpe | 0:5e013296b353 | 477 | ft_void_t FT800::Ft_App_WrCoCmd_Buffer(ft_uint32_t cmd) |

| dreschpe | 0:5e013296b353 | 478 | { |

| dreschpe | 0:5e013296b353 | 479 | Ft_Gpu_Hal_WrCmd32(cmd); |

| dreschpe | 0:5e013296b353 | 480 | /* Increment the command index */ |

| dreschpe | 0:5e013296b353 | 481 | Ft_CmdBuffer_Index += FT_CMD_SIZE; |

| dreschpe | 0:5e013296b353 | 482 | } |

| dreschpe | 0:5e013296b353 | 483 | |

| dreschpe | 0:5e013296b353 | 484 | ft_void_t FT800::Ft_App_WrDlCmd_Buffer(ft_uint32_t cmd) |

| dreschpe | 0:5e013296b353 | 485 | { |

| dreschpe | 0:5e013296b353 | 486 | Ft_Gpu_Hal_Wr32((RAM_DL+Ft_DlBuffer_Index),cmd); |

| dreschpe | 0:5e013296b353 | 487 | /* Increment the command index */ |

| dreschpe | 0:5e013296b353 | 488 | Ft_DlBuffer_Index += FT_CMD_SIZE; |

| dreschpe | 0:5e013296b353 | 489 | } |

| dreschpe | 0:5e013296b353 | 490 | |

| dreschpe | 0:5e013296b353 | 491 | ft_void_t FT800::Ft_App_Flush_DL_Buffer() |

| dreschpe | 0:5e013296b353 | 492 | { |

| dreschpe | 0:5e013296b353 | 493 | Ft_DlBuffer_Index = 0; |

| dreschpe | 0:5e013296b353 | 494 | |

| dreschpe | 0:5e013296b353 | 495 | } |

| dreschpe | 0:5e013296b353 | 496 | |

| dreschpe | 0:5e013296b353 | 497 | ft_void_t FT800::Ft_App_Flush_Co_Buffer() |

| dreschpe | 0:5e013296b353 | 498 | { |

| dreschpe | 0:5e013296b353 | 499 | Ft_CmdBuffer_Index = 0; |

| dreschpe | 0:5e013296b353 | 500 | } |

| dreschpe | 0:5e013296b353 | 501 | |

| dreschpe | 0:5e013296b353 | 502 | |

| dreschpe | 0:5e013296b353 | 503 | /* API to check the status of previous DLSWAP and perform DLSWAP of new DL */ |

| dreschpe | 0:5e013296b353 | 504 | /* Check for the status of previous DLSWAP and if still not done wait for few ms and check again */ |

| dreschpe | 0:5e013296b353 | 505 | ft_void_t FT800::GPU_DLSwap(ft_uint8_t DL_Swap_Type) |

| dreschpe | 0:5e013296b353 | 506 | { |

| dreschpe | 0:5e013296b353 | 507 | ft_uint8_t Swap_Type = DLSWAP_FRAME,Swap_Done = DLSWAP_FRAME; |

| dreschpe | 0:5e013296b353 | 508 | |

| dreschpe | 0:5e013296b353 | 509 | if(DL_Swap_Type == DLSWAP_LINE) |

| dreschpe | 0:5e013296b353 | 510 | { |

| dreschpe | 0:5e013296b353 | 511 | Swap_Type = DLSWAP_LINE; |

| dreschpe | 0:5e013296b353 | 512 | } |

| dreschpe | 0:5e013296b353 | 513 | |

| dreschpe | 0:5e013296b353 | 514 | /* Perform a new DL swap */ |

| dreschpe | 0:5e013296b353 | 515 | Ft_Gpu_Hal_Wr8(REG_DLSWAP,Swap_Type); |

| dreschpe | 0:5e013296b353 | 516 | |

| dreschpe | 0:5e013296b353 | 517 | /* Wait till the swap is done */ |

| dreschpe | 0:5e013296b353 | 518 | while(Swap_Done) |

| dreschpe | 0:5e013296b353 | 519 | { |

| dreschpe | 0:5e013296b353 | 520 | Swap_Done = Ft_Gpu_Hal_Rd8(REG_DLSWAP); |

| dreschpe | 0:5e013296b353 | 521 | |

| dreschpe | 0:5e013296b353 | 522 | if(DLSWAP_DONE != Swap_Done) |

| dreschpe | 0:5e013296b353 | 523 | { |

| dreschpe | 0:5e013296b353 | 524 | Ft_Gpu_Hal_Sleep(10);//wait for 10ms |

| dreschpe | 0:5e013296b353 | 525 | } |

| dreschpe | 0:5e013296b353 | 526 | } |

| dreschpe | 0:5e013296b353 | 527 | } |

| dreschpe | 0:5e013296b353 | 528 | |

| dreschpe | 0:5e013296b353 | 529 | |

| dreschpe | 0:5e013296b353 | 530 | |

| dreschpe | 0:5e013296b353 | 531 | /* Nothing beyond this */ |

| dreschpe | 0:5e013296b353 | 532 | |

| dreschpe | 0:5e013296b353 | 533 | |

| dreschpe | 0:5e013296b353 | 534 | |

| dreschpe | 0:5e013296b353 | 535 |

EVE FT800

EVE FT800