BLACKPILL custom target.

BLACKPILL custom target

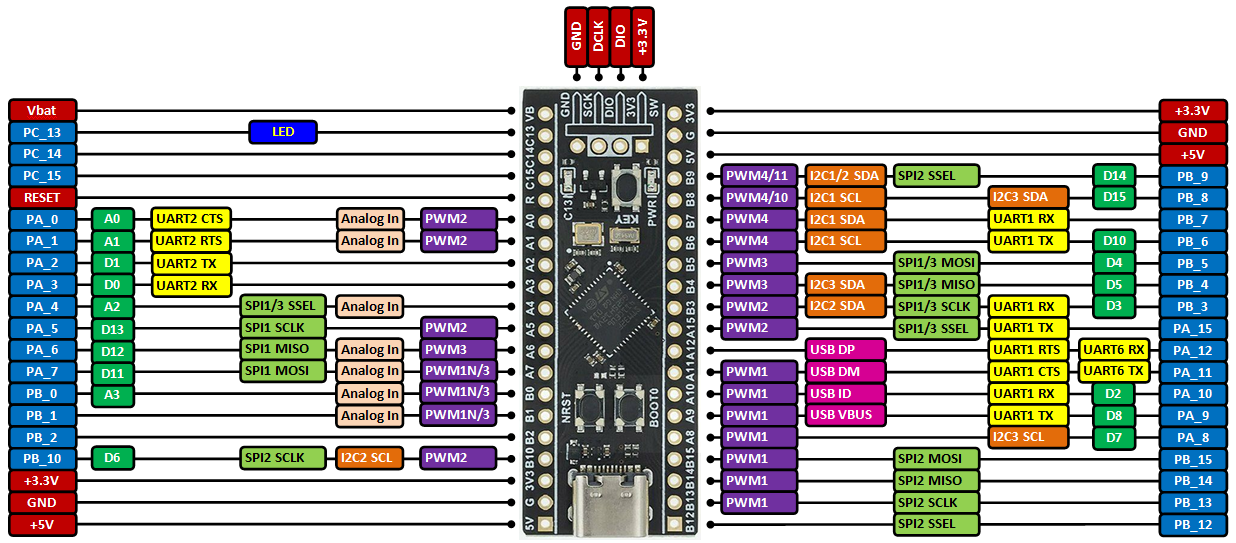

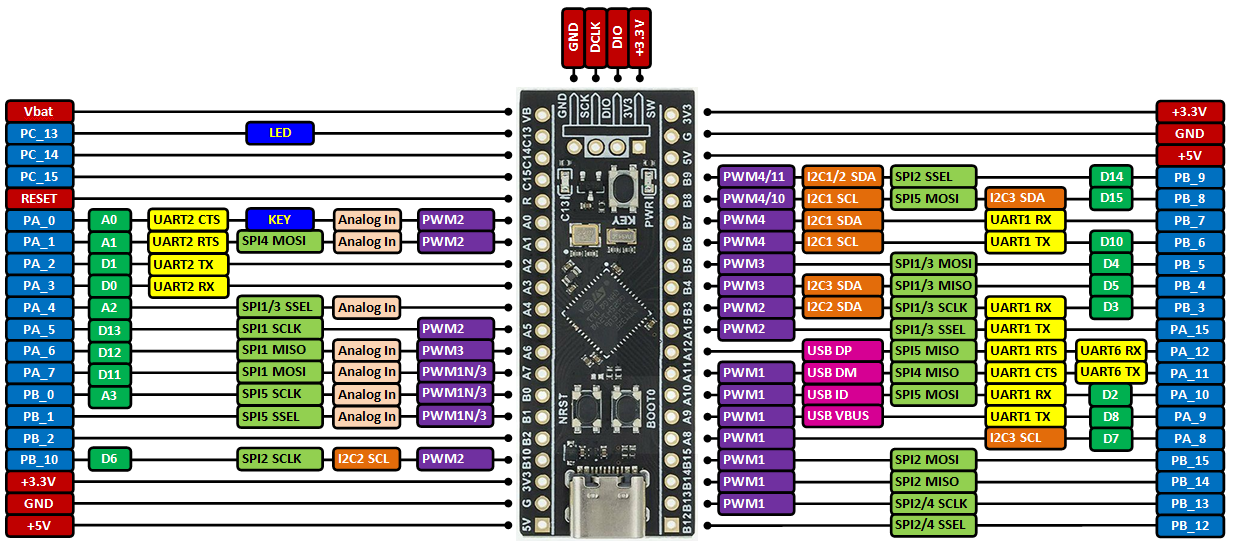

Board pinout

When equipped with STM32F401CCU6:

When equipped with STM32F411CEU6:

Advantages of the BLACKPILL custom target over the NUCLEO_F401RE/ NUCLEO_F411RE

- The onboard external 25 MHz crystal is used as system clock source rather than the less precise internal 16 MHz RC oscillator.

- The onboard LED works as LED1 in programs.

- The onboard KEY on STM32F411CEU6 boards works as USER_BUTTON pin in programs.

- You can use the USB peripheral in your programs and connect the board to the PC over the onboard USB connector. An example of using the USB peripheral as USBSerial (12 Mbit/s) is available here.

Building programs for the BLACKPILL custom target in Mbed Studio

- Connect an STM32 ST-Link programmer to your BLACKPILL board and PC (see below for more details).

- Create a new program in the Mbed Studio IDE.

- Right-click on the program's root folder and in the popup window select

Add library...

- Copy&paste the text https://os.mbed.com/users/hudakz/code/BLACKPILL_Custom_Target into the

Git or os.mbed.com URLedit box and click on theNextbutton.

- Open the drop-list and select

defaultasBranch or tagand click on theFinishbutton.

- Open the

BLACKPILL_Custom_Targetfolder and according to you board drag&drop theTARGET_BLACKPILL_F401CCor theTARGET_BLACKPILL_F411CEfolder and thecustom_targets.jsonfile one by one to the root folder of your program.

- Delete the

BLACKPILL_Custom_Targetfolder from your project. (Right-click and select delete).

- Open the

Targetdrop-list and click on the button with a "chip" icon on it (Manage custom targets) .

- Open the

USB devicedrop-list and select your STM32 ST-Link programmer.

- Open the

Build targetdrop-list and according to your board selectBLACKPILL_F401CCorBLACKPILL_F411CE.

- Click on the

Save Allbutton.

- Build your program (click on hammer button).

For more info visit

Import programBlackpill_Hello

Using low cost Blackpill (STM32F411CEU6) boards with mbed.

Revision 3:e156af7ad2ac, committed 2021-04-14

- Comitter:

- hudakz

- Date:

- Wed Apr 14 08:21:15 2021 +0000

- Parent:

- 2:4659e197ae83

- Child:

- 4:e2ec79fa1c70

- Commit message:

- BLACKPILL custom target.

Changed in this revision

--- a/TARGET_BLACKPILL/PeripheralPinMaps.h Fri Apr 02 07:37:35 2021 +0000 +++ b/TARGET_BLACKPILL/PeripheralPinMaps.h Wed Apr 14 08:21:15 2021 +0000 @@ -260,4 +260,4 @@ #define PINMAP_SPI_SSEL PinMap_SPI_SSEL #define PINMAP_PWM PinMap_PWM -#endif \ No newline at end of file +#endif

--- a/TARGET_BLACKPILL/PeripheralPins.c Fri Apr 02 07:37:35 2021 +0000 +++ b/TARGET_BLACKPILL/PeripheralPins.c Wed Apr 14 08:21:15 2021 +0000 @@ -31,3 +31,4 @@ #include "PeripheralPins.h" #include "mbed_toolchain.h" #include "PeripheralPinMaps.h" +

--- a/TARGET_BLACKPILL/PinNames.h Fri Apr 02 07:37:35 2021 +0000 +++ b/TARGET_BLACKPILL/PinNames.h Wed Apr 14 08:21:15 2021 +0000 @@ -218,3 +218,4 @@ #endif #endif +

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/TARGET_BLACKPILL/TOOLCHAIN_ARM/startup_stm32f411xe.S Wed Apr 14 08:21:15 2021 +0000 @@ -0,0 +1,336 @@ +;******************************************************************************* +;* File Name : startup_stm32f411xe.s +;* Author : MCD Application Team +;* Description : STM32F411xExx devices vector table for MDK-ARM toolchain. +;* This module performs: +;* - Set the initial SP +;* - Set the initial PC == Reset_Handler +;* - Set the vector table entries with the exceptions ISR address +;* - Branches to __main in the C library (which eventually +;* calls main()). +;* After Reset the CortexM4 processor is in Thread mode, +;* priority is Privileged, and the Stack is set to Main. +;******************************************************************************** +;* @attention +;* +;* <h2><center>© Copyright (c) 2017 STMicroelectronics. +;* All rights reserved.</center></h2> +;* +;* This software component is licensed by ST under BSD 3-Clause license, +;* the "License"; You may not use this file except in compliance with the +;* License. You may obtain a copy of the License at: +;* opensource.org/licenses/BSD-3-Clause +;* +;******************************************************************************* +;* <<< Use Configuration Wizard in Context Menu >>> +; + PRESERVE8 + THUMB + + +; Vector Table Mapped to Address 0 at Reset + AREA RESET, DATA, READONLY + EXPORT __Vectors + EXPORT __Vectors_End + EXPORT __Vectors_Size + + IMPORT |Image$$ARM_LIB_STACK$$ZI$$Limit| +__Vectors DCD |Image$$ARM_LIB_STACK$$ZI$$Limit| ; Top of Stack + DCD Reset_Handler ; Reset Handler + DCD NMI_Handler ; NMI Handler + DCD HardFault_Handler ; Hard Fault Handler + DCD MemManage_Handler ; MPU Fault Handler + DCD BusFault_Handler ; Bus Fault Handler + DCD UsageFault_Handler ; Usage Fault Handler + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD SVC_Handler ; SVCall Handler + DCD DebugMon_Handler ; Debug Monitor Handler + DCD 0 ; Reserved + DCD PendSV_Handler ; PendSV Handler + DCD SysTick_Handler ; SysTick Handler + + ; External Interrupts + DCD WWDG_IRQHandler ; Window WatchDog + DCD PVD_IRQHandler ; PVD through EXTI Line detection + DCD TAMP_STAMP_IRQHandler ; Tamper and TimeStamps through the EXTI line + DCD RTC_WKUP_IRQHandler ; RTC Wakeup through the EXTI line + DCD FLASH_IRQHandler ; FLASH + DCD RCC_IRQHandler ; RCC + DCD EXTI0_IRQHandler ; EXTI Line0 + DCD EXTI1_IRQHandler ; EXTI Line1 + DCD EXTI2_IRQHandler ; EXTI Line2 + DCD EXTI3_IRQHandler ; EXTI Line3 + DCD EXTI4_IRQHandler ; EXTI Line4 + DCD DMA1_Stream0_IRQHandler ; DMA1 Stream 0 + DCD DMA1_Stream1_IRQHandler ; DMA1 Stream 1 + DCD DMA1_Stream2_IRQHandler ; DMA1 Stream 2 + DCD DMA1_Stream3_IRQHandler ; DMA1 Stream 3 + DCD DMA1_Stream4_IRQHandler ; DMA1 Stream 4 + DCD DMA1_Stream5_IRQHandler ; DMA1 Stream 5 + DCD DMA1_Stream6_IRQHandler ; DMA1 Stream 6 + DCD ADC_IRQHandler ; ADC1, ADC2 and ADC3s + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD EXTI9_5_IRQHandler ; External Line[9:5]s + DCD TIM1_BRK_TIM9_IRQHandler ; TIM1 Break and TIM9 + DCD TIM1_UP_TIM10_IRQHandler ; TIM1 Update and TIM10 + DCD TIM1_TRG_COM_TIM11_IRQHandler ; TIM1 Trigger and Commutation and TIM11 + DCD TIM1_CC_IRQHandler ; TIM1 Capture Compare + DCD TIM2_IRQHandler ; TIM2 + DCD TIM3_IRQHandler ; TIM3 + DCD TIM4_IRQHandler ; TIM4 + DCD I2C1_EV_IRQHandler ; I2C1 Event + DCD I2C1_ER_IRQHandler ; I2C1 Error + DCD I2C2_EV_IRQHandler ; I2C2 Event + DCD I2C2_ER_IRQHandler ; I2C2 Error + DCD SPI1_IRQHandler ; SPI1 + DCD SPI2_IRQHandler ; SPI2 + DCD USART1_IRQHandler ; USART1 + DCD USART2_IRQHandler ; USART2 + DCD 0 ; Reserved + DCD EXTI15_10_IRQHandler ; External Line[15:10]s + DCD RTC_Alarm_IRQHandler ; RTC Alarm (A and B) through EXTI Line + DCD OTG_FS_WKUP_IRQHandler ; USB OTG FS Wakeup through EXTI line + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD DMA1_Stream7_IRQHandler ; DMA1 Stream7 + DCD 0 ; Reserved + DCD SDIO_IRQHandler ; SDIO + DCD TIM5_IRQHandler ; TIM5 + DCD SPI3_IRQHandler ; SPI3 + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD DMA2_Stream0_IRQHandler ; DMA2 Stream 0 + DCD DMA2_Stream1_IRQHandler ; DMA2 Stream 1 + DCD DMA2_Stream2_IRQHandler ; DMA2 Stream 2 + DCD DMA2_Stream3_IRQHandler ; DMA2 Stream 3 + DCD DMA2_Stream4_IRQHandler ; DMA2 Stream 4 + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD OTG_FS_IRQHandler ; USB OTG FS + DCD DMA2_Stream5_IRQHandler ; DMA2 Stream 5 + DCD DMA2_Stream6_IRQHandler ; DMA2 Stream 6 + DCD DMA2_Stream7_IRQHandler ; DMA2 Stream 7 + DCD USART6_IRQHandler ; USART6 + DCD I2C3_EV_IRQHandler ; I2C3 event + DCD I2C3_ER_IRQHandler ; I2C3 error + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD FPU_IRQHandler ; FPU + DCD 0 ; Reserved + DCD 0 ; Reserved + DCD SPI4_IRQHandler ; SPI4 + DCD SPI5_IRQHandler ; SPI5 + +__Vectors_End + +__Vectors_Size EQU __Vectors_End - __Vectors + + AREA |.text|, CODE, READONLY + +; Reset handler +Reset_Handler PROC + EXPORT Reset_Handler [WEAK] + IMPORT SystemInit + IMPORT __main + + LDR R0, =SystemInit + BLX R0 + LDR R0, =__main + BX R0 + ENDP + +; Dummy Exception Handlers (infinite loops which can be modified) + +NMI_Handler PROC + EXPORT NMI_Handler [WEAK] + B . + ENDP +HardFault_Handler\ + PROC + EXPORT HardFault_Handler [WEAK] + B . + ENDP +MemManage_Handler\ + PROC + EXPORT MemManage_Handler [WEAK] + B . + ENDP +BusFault_Handler\ + PROC + EXPORT BusFault_Handler [WEAK] + B . + ENDP +UsageFault_Handler\ + PROC + EXPORT UsageFault_Handler [WEAK] + B . + ENDP +SVC_Handler PROC + EXPORT SVC_Handler [WEAK] + B . + ENDP +DebugMon_Handler\ + PROC + EXPORT DebugMon_Handler [WEAK] + B . + ENDP +PendSV_Handler PROC + EXPORT PendSV_Handler [WEAK] + B . + ENDP +SysTick_Handler PROC + EXPORT SysTick_Handler [WEAK] + B . + ENDP + +Default_Handler PROC + + EXPORT WWDG_IRQHandler [WEAK] + EXPORT PVD_IRQHandler [WEAK] + EXPORT TAMP_STAMP_IRQHandler [WEAK] + EXPORT RTC_WKUP_IRQHandler [WEAK] + EXPORT FLASH_IRQHandler [WEAK] + EXPORT RCC_IRQHandler [WEAK] + EXPORT EXTI0_IRQHandler [WEAK] + EXPORT EXTI1_IRQHandler [WEAK] + EXPORT EXTI2_IRQHandler [WEAK] + EXPORT EXTI3_IRQHandler [WEAK] + EXPORT EXTI4_IRQHandler [WEAK] + EXPORT DMA1_Stream0_IRQHandler [WEAK] + EXPORT DMA1_Stream1_IRQHandler [WEAK] + EXPORT DMA1_Stream2_IRQHandler [WEAK] + EXPORT DMA1_Stream3_IRQHandler [WEAK] + EXPORT DMA1_Stream4_IRQHandler [WEAK] + EXPORT DMA1_Stream5_IRQHandler [WEAK] + EXPORT DMA1_Stream6_IRQHandler [WEAK] + EXPORT ADC_IRQHandler [WEAK] + EXPORT EXTI9_5_IRQHandler [WEAK] + EXPORT TIM1_BRK_TIM9_IRQHandler [WEAK] + EXPORT TIM1_UP_TIM10_IRQHandler [WEAK] + EXPORT TIM1_TRG_COM_TIM11_IRQHandler [WEAK] + EXPORT TIM1_CC_IRQHandler [WEAK] + EXPORT TIM2_IRQHandler [WEAK] + EXPORT TIM3_IRQHandler [WEAK] + EXPORT TIM4_IRQHandler [WEAK] + EXPORT I2C1_EV_IRQHandler [WEAK] + EXPORT I2C1_ER_IRQHandler [WEAK] + EXPORT I2C2_EV_IRQHandler [WEAK] + EXPORT I2C2_ER_IRQHandler [WEAK] + EXPORT SPI1_IRQHandler [WEAK] + EXPORT SPI2_IRQHandler [WEAK] + EXPORT USART1_IRQHandler [WEAK] + EXPORT USART2_IRQHandler [WEAK] + EXPORT EXTI15_10_IRQHandler [WEAK] + EXPORT RTC_Alarm_IRQHandler [WEAK] + EXPORT OTG_FS_WKUP_IRQHandler [WEAK] + EXPORT DMA1_Stream7_IRQHandler [WEAK] + EXPORT SDIO_IRQHandler [WEAK] + EXPORT TIM5_IRQHandler [WEAK] + EXPORT SPI3_IRQHandler [WEAK] + EXPORT DMA2_Stream0_IRQHandler [WEAK] + EXPORT DMA2_Stream1_IRQHandler [WEAK] + EXPORT DMA2_Stream2_IRQHandler [WEAK] + EXPORT DMA2_Stream3_IRQHandler [WEAK] + EXPORT DMA2_Stream4_IRQHandler [WEAK] + EXPORT OTG_FS_IRQHandler [WEAK] + EXPORT DMA2_Stream5_IRQHandler [WEAK] + EXPORT DMA2_Stream6_IRQHandler [WEAK] + EXPORT DMA2_Stream7_IRQHandler [WEAK] + EXPORT USART6_IRQHandler [WEAK] + EXPORT I2C3_EV_IRQHandler [WEAK] + EXPORT I2C3_ER_IRQHandler [WEAK] + EXPORT FPU_IRQHandler [WEAK] + EXPORT SPI4_IRQHandler [WEAK] + EXPORT SPI5_IRQHandler [WEAK] + +WWDG_IRQHandler +PVD_IRQHandler +TAMP_STAMP_IRQHandler +RTC_WKUP_IRQHandler +FLASH_IRQHandler +RCC_IRQHandler +EXTI0_IRQHandler +EXTI1_IRQHandler +EXTI2_IRQHandler +EXTI3_IRQHandler +EXTI4_IRQHandler +DMA1_Stream0_IRQHandler +DMA1_Stream1_IRQHandler +DMA1_Stream2_IRQHandler +DMA1_Stream3_IRQHandler +DMA1_Stream4_IRQHandler +DMA1_Stream5_IRQHandler +DMA1_Stream6_IRQHandler +ADC_IRQHandler +EXTI9_5_IRQHandler +TIM1_BRK_TIM9_IRQHandler +TIM1_UP_TIM10_IRQHandler +TIM1_TRG_COM_TIM11_IRQHandler +TIM1_CC_IRQHandler +TIM2_IRQHandler +TIM3_IRQHandler +TIM4_IRQHandler +I2C1_EV_IRQHandler +I2C1_ER_IRQHandler +I2C2_EV_IRQHandler +I2C2_ER_IRQHandler +SPI1_IRQHandler +SPI2_IRQHandler +USART1_IRQHandler +USART2_IRQHandler +EXTI15_10_IRQHandler +RTC_Alarm_IRQHandler +OTG_FS_WKUP_IRQHandler +DMA1_Stream7_IRQHandler +SDIO_IRQHandler +TIM5_IRQHandler +SPI3_IRQHandler +DMA2_Stream0_IRQHandler +DMA2_Stream1_IRQHandler +DMA2_Stream2_IRQHandler +DMA2_Stream3_IRQHandler +DMA2_Stream4_IRQHandler +OTG_FS_IRQHandler +DMA2_Stream5_IRQHandler +DMA2_Stream6_IRQHandler +DMA2_Stream7_IRQHandler +USART6_IRQHandler +I2C3_EV_IRQHandler +I2C3_ER_IRQHandler +FPU_IRQHandler +SPI4_IRQHandler +SPI5_IRQHandler + + B . + + ENDP + + ALIGN + +;******************************************************************************* +; User Stack and Heap initialization +;******************************************************************************* + + END + +;************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE***** +

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/TARGET_BLACKPILL/TOOLCHAIN_ARM/stm32f411xe.sct Wed Apr 14 08:21:15 2021 +0000

@@ -0,0 +1,69 @@

+#! armclang -E --target=arm-arm-none-eabi -x c -mcpu=cortex-m4

+; Scatter-Loading Description File

+;

+; SPDX-License-Identifier: BSD-3-Clause

+;******************************************************************************

+;* @attention

+;*

+;* Copyright (c) 2016-2020 STMicroelectronics.

+;* All rights reserved.

+;*

+;* This software component is licensed by ST under BSD 3-Clause license,

+;* the "License"; You may not use this file except in compliance with the

+;* License. You may obtain a copy of the License at:

+;* opensource.org/licenses/BSD-3-Clause

+;*

+;******************************************************************************

+

+#include "../cmsis_nvic.h"

+

+#if !defined(MBED_APP_START)

+ #define MBED_APP_START MBED_ROM_START

+#endif

+

+#if !defined(MBED_APP_SIZE)

+ #define MBED_APP_SIZE MBED_ROM_SIZE

+#endif

+

+#if !defined(MBED_CONF_TARGET_BOOT_STACK_SIZE)

+/* This value is normally defined by the tools to 0x1000 for bare metal and 0x400 for RTOS */

+#if defined(MBED_BOOT_STACK_SIZE)

+#define MBED_CONF_TARGET_BOOT_STACK_SIZE MBED_BOOT_STACK_SIZE

+#else

+#define MBED_CONF_TARGET_BOOT_STACK_SIZE 0x400

+#endif

+#endif

+

+/* Round up VECTORS_SIZE to 8 bytes */

+#define VECTORS_SIZE (((NVIC_NUM_VECTORS * 4) + 7) AND ~7)

+

+#define MBED_CRASH_REPORT_RAM_SIZE 0x100

+

+#define MBED_IRAM1_START (MBED_RAM_START + VECTORS_SIZE + MBED_CRASH_REPORT_RAM_SIZE)

+#define MBED_IRAM1_SIZE (MBED_RAM_SIZE - VECTORS_SIZE - MBED_CRASH_REPORT_RAM_SIZE)

+

+

+#define RAM_FIXED_SIZE (MBED_CONF_TARGET_BOOT_STACK_SIZE + VECTORS_SIZE + MBED_CRASH_REPORT_RAM_SIZE)

+

+LR_IROM1 MBED_APP_START MBED_APP_SIZE {

+

+ ER_IROM1 MBED_APP_START MBED_APP_SIZE {

+ *.o (RESET, +First)

+ *(InRoot$$Sections)

+ .ANY (+RO)

+ }

+

+ RW_m_crash_data (MBED_RAM_START + VECTORS_SIZE) EMPTY MBED_CRASH_REPORT_RAM_SIZE { ; RW data

+ }

+

+ RW_IRAM1 MBED_IRAM1_START MBED_IRAM1_SIZE { ; RW data

+ .ANY (+RW +ZI)

+ }

+

+ ARM_LIB_HEAP AlignExpr(+0, 16) EMPTY (MBED_IRAM1_START + MBED_RAM_SIZE - RAM_FIXED_SIZE - AlignExpr(ImageLimit(RW_IRAM1), 16)) { ; Heap growing up

+ }

+

+ ARM_LIB_STACK (MBED_RAM_START + MBED_RAM_SIZE) EMPTY -MBED_CONF_TARGET_BOOT_STACK_SIZE { ; Stack region growing down

+ }

+}

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/TARGET_BLACKPILL/TOOLCHAIN_GCC_ARM/startup_stm32f411xe.S Wed Apr 14 08:21:15 2021 +0000 @@ -0,0 +1,438 @@ +/** + ****************************************************************************** + * @file startup_stm32f411xe.s + * @author MCD Application Team + * @brief STM32F411xExx Devices vector table for GCC based toolchains. + * This module performs: + * - Set the initial SP + * - Set the initial PC == Reset_Handler, + * - Set the vector table entries with the exceptions ISR address + * - Branches to main in the C library (which eventually + * calls main()). + * After Reset the Cortex-M4 processor is in Thread mode, + * priority is Privileged, and the Stack is set to Main. + ****************************************************************************** + * @attention + * + * <h2><center>© Copyright (c) 2017 STMicroelectronics. + * All rights reserved.</center></h2> + * + * This software component is licensed by ST under BSD 3-Clause license, + * the "License"; You may not use this file except in compliance with the + * License. You may obtain a copy of the License at: + * opensource.org/licenses/BSD-3-Clause + * + ****************************************************************************** + */ + + .syntax unified + .cpu cortex-m4 + .fpu softvfp + .thumb + +.global g_pfnVectors +.global Default_Handler + +/* start address for the initialization values of the .data section. +defined in linker script */ +.word _sidata +/* start address for the .data section. defined in linker script */ +.word _sdata +/* end address for the .data section. defined in linker script */ +.word _edata +/* start address for the .bss section. defined in linker script */ +.word _sbss +/* end address for the .bss section. defined in linker script */ +.word _ebss +/* stack used for SystemInit_ExtMemCtl; always internal RAM used */ + +/** + * @brief This is the code that gets called when the processor first + * starts execution following a reset event. Only the absolutely + * necessary set is performed, after which the application + * supplied main() routine is called. + * @param None + * @retval : None +*/ + + .section .text.Reset_Handler + .weak Reset_Handler + .type Reset_Handler, %function +Reset_Handler: + ldr sp, =_estack /* set stack pointer */ + +/* Copy the data segment initializers from flash to SRAM */ + ldr r0, =_sdata + ldr r1, =_edata + ldr r2, =_sidata + movs r3, #0 + b LoopCopyDataInit + +CopyDataInit: + ldr r4, [r2, r3] + str r4, [r0, r3] + adds r3, r3, #4 + +LoopCopyDataInit: + adds r4, r0, r3 + cmp r4, r1 + bcc CopyDataInit + +/* Zero fill the bss segment. */ + ldr r2, =_sbss + ldr r4, =_ebss + movs r3, #0 + b LoopFillZerobss + +FillZerobss: + str r3, [r2] + adds r2, r2, #4 + +LoopFillZerobss: + cmp r2, r4 + bcc FillZerobss + +/* Call the clock system intitialization function.*/ + bl SystemInit + bl _start + bx lr + bx lr +.size Reset_Handler, .-Reset_Handler + +/** + * @brief This is the code that gets called when the processor receives an + * unexpected interrupt. This simply enters an infinite loop, preserving + * the system state for examination by a debugger. + * @param None + * @retval None +*/ + .section .text.Default_Handler,"ax",%progbits +Default_Handler: +Infinite_Loop: + b Infinite_Loop + .size Default_Handler, .-Default_Handler +/****************************************************************************** +* +* The minimal vector table for a Cortex M3. Note that the proper constructs +* must be placed on this to ensure that it ends up at physical address +* 0x0000.0000. +* +*******************************************************************************/ + .section .isr_vector,"a",%progbits + .type g_pfnVectors, %object + .size g_pfnVectors, .-g_pfnVectors + +g_pfnVectors: + .word _estack + .word Reset_Handler + .word NMI_Handler + .word HardFault_Handler + .word MemManage_Handler + .word BusFault_Handler + .word UsageFault_Handler + .word 0 + .word 0 + .word 0 + .word 0 + .word SVC_Handler + .word DebugMon_Handler + .word 0 + .word PendSV_Handler + .word SysTick_Handler + + /* External Interrupts */ + .word WWDG_IRQHandler /* Window WatchDog */ + .word PVD_IRQHandler /* PVD through EXTI Line detection */ + .word TAMP_STAMP_IRQHandler /* Tamper and TimeStamps through the EXTI line */ + .word RTC_WKUP_IRQHandler /* RTC Wakeup through the EXTI line */ + .word FLASH_IRQHandler /* FLASH */ + .word RCC_IRQHandler /* RCC */ + .word EXTI0_IRQHandler /* EXTI Line0 */ + .word EXTI1_IRQHandler /* EXTI Line1 */ + .word EXTI2_IRQHandler /* EXTI Line2 */ + .word EXTI3_IRQHandler /* EXTI Line3 */ + .word EXTI4_IRQHandler /* EXTI Line4 */ + .word DMA1_Stream0_IRQHandler /* DMA1 Stream 0 */ + .word DMA1_Stream1_IRQHandler /* DMA1 Stream 1 */ + .word DMA1_Stream2_IRQHandler /* DMA1 Stream 2 */ + .word DMA1_Stream3_IRQHandler /* DMA1 Stream 3 */ + .word DMA1_Stream4_IRQHandler /* DMA1 Stream 4 */ + .word DMA1_Stream5_IRQHandler /* DMA1 Stream 5 */ + .word DMA1_Stream6_IRQHandler /* DMA1 Stream 6 */ + .word ADC_IRQHandler /* ADC1, ADC2 and ADC3s */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word EXTI9_5_IRQHandler /* External Line[9:5]s */ + .word TIM1_BRK_TIM9_IRQHandler /* TIM1 Break and TIM9 */ + .word TIM1_UP_TIM10_IRQHandler /* TIM1 Update and TIM10 */ + .word TIM1_TRG_COM_TIM11_IRQHandler /* TIM1 Trigger and Commutation and TIM11 */ + .word TIM1_CC_IRQHandler /* TIM1 Capture Compare */ + .word TIM2_IRQHandler /* TIM2 */ + .word TIM3_IRQHandler /* TIM3 */ + .word TIM4_IRQHandler /* TIM4 */ + .word I2C1_EV_IRQHandler /* I2C1 Event */ + .word I2C1_ER_IRQHandler /* I2C1 Error */ + .word I2C2_EV_IRQHandler /* I2C2 Event */ + .word I2C2_ER_IRQHandler /* I2C2 Error */ + .word SPI1_IRQHandler /* SPI1 */ + .word SPI2_IRQHandler /* SPI2 */ + .word USART1_IRQHandler /* USART1 */ + .word USART2_IRQHandler /* USART2 */ + .word 0 /* Reserved */ + .word EXTI15_10_IRQHandler /* External Line[15:10]s */ + .word RTC_Alarm_IRQHandler /* RTC Alarm (A and B) through EXTI Line */ + .word OTG_FS_WKUP_IRQHandler /* USB OTG FS Wakeup through EXTI line */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word DMA1_Stream7_IRQHandler /* DMA1 Stream7 */ + .word 0 /* Reserved */ + .word SDIO_IRQHandler /* SDIO */ + .word TIM5_IRQHandler /* TIM5 */ + .word SPI3_IRQHandler /* SPI3 */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word DMA2_Stream0_IRQHandler /* DMA2 Stream 0 */ + .word DMA2_Stream1_IRQHandler /* DMA2 Stream 1 */ + .word DMA2_Stream2_IRQHandler /* DMA2 Stream 2 */ + .word DMA2_Stream3_IRQHandler /* DMA2 Stream 3 */ + .word DMA2_Stream4_IRQHandler /* DMA2 Stream 4 */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word OTG_FS_IRQHandler /* USB OTG FS */ + .word DMA2_Stream5_IRQHandler /* DMA2 Stream 5 */ + .word DMA2_Stream6_IRQHandler /* DMA2 Stream 6 */ + .word DMA2_Stream7_IRQHandler /* DMA2 Stream 7 */ + .word USART6_IRQHandler /* USART6 */ + .word I2C3_EV_IRQHandler /* I2C3 event */ + .word I2C3_ER_IRQHandler /* I2C3 error */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word FPU_IRQHandler /* FPU */ + .word 0 /* Reserved */ + .word 0 /* Reserved */ + .word SPI4_IRQHandler /* SPI4 */ + .word SPI5_IRQHandler /* SPI5 */ + +/******************************************************************************* +* +* Provide weak aliases for each Exception handler to the Default_Handler. +* As they are weak aliases, any function with the same name will override +* this definition. +* +*******************************************************************************/ + .weak NMI_Handler + .thumb_set NMI_Handler,Default_Handler + + .weak HardFault_Handler + .thumb_set HardFault_Handler,Default_Handler + + .weak MemManage_Handler + .thumb_set MemManage_Handler,Default_Handler + + .weak BusFault_Handler + .thumb_set BusFault_Handler,Default_Handler + + .weak UsageFault_Handler + .thumb_set UsageFault_Handler,Default_Handler + + .weak SVC_Handler + .thumb_set SVC_Handler,Default_Handler + + .weak DebugMon_Handler + .thumb_set DebugMon_Handler,Default_Handler + + .weak PendSV_Handler + .thumb_set PendSV_Handler,Default_Handler + + .weak SysTick_Handler + .thumb_set SysTick_Handler,Default_Handler + + .weak WWDG_IRQHandler + .thumb_set WWDG_IRQHandler,Default_Handler + + .weak PVD_IRQHandler + .thumb_set PVD_IRQHandler,Default_Handler + + .weak TAMP_STAMP_IRQHandler + .thumb_set TAMP_STAMP_IRQHandler,Default_Handler + + .weak RTC_WKUP_IRQHandler + .thumb_set RTC_WKUP_IRQHandler,Default_Handler + + .weak FLASH_IRQHandler + .thumb_set FLASH_IRQHandler,Default_Handler + + .weak RCC_IRQHandler + .thumb_set RCC_IRQHandler,Default_Handler + + .weak EXTI0_IRQHandler + .thumb_set EXTI0_IRQHandler,Default_Handler + + .weak EXTI1_IRQHandler + .thumb_set EXTI1_IRQHandler,Default_Handler + + .weak EXTI2_IRQHandler + .thumb_set EXTI2_IRQHandler,Default_Handler + + .weak EXTI3_IRQHandler + .thumb_set EXTI3_IRQHandler,Default_Handler + + .weak EXTI4_IRQHandler + .thumb_set EXTI4_IRQHandler,Default_Handler + + .weak DMA1_Stream0_IRQHandler + .thumb_set DMA1_Stream0_IRQHandler,Default_Handler + + .weak DMA1_Stream1_IRQHandler + .thumb_set DMA1_Stream1_IRQHandler,Default_Handler + + .weak DMA1_Stream2_IRQHandler + .thumb_set DMA1_Stream2_IRQHandler,Default_Handler + + .weak DMA1_Stream3_IRQHandler + .thumb_set DMA1_Stream3_IRQHandler,Default_Handler + + .weak DMA1_Stream4_IRQHandler + .thumb_set DMA1_Stream4_IRQHandler,Default_Handler + + .weak DMA1_Stream5_IRQHandler + .thumb_set DMA1_Stream5_IRQHandler,Default_Handler + + .weak DMA1_Stream6_IRQHandler + .thumb_set DMA1_Stream6_IRQHandler,Default_Handler + + .weak ADC_IRQHandler + .thumb_set ADC_IRQHandler,Default_Handler + + .weak EXTI9_5_IRQHandler + .thumb_set EXTI9_5_IRQHandler,Default_Handler + + .weak TIM1_BRK_TIM9_IRQHandler + .thumb_set TIM1_BRK_TIM9_IRQHandler,Default_Handler + + .weak TIM1_UP_TIM10_IRQHandler + .thumb_set TIM1_UP_TIM10_IRQHandler,Default_Handler + + .weak TIM1_TRG_COM_TIM11_IRQHandler + .thumb_set TIM1_TRG_COM_TIM11_IRQHandler,Default_Handler + + .weak TIM1_CC_IRQHandler + .thumb_set TIM1_CC_IRQHandler,Default_Handler + + .weak TIM2_IRQHandler + .thumb_set TIM2_IRQHandler,Default_Handler + + .weak TIM3_IRQHandler + .thumb_set TIM3_IRQHandler,Default_Handler + + .weak TIM4_IRQHandler + .thumb_set TIM4_IRQHandler,Default_Handler + + .weak I2C1_EV_IRQHandler + .thumb_set I2C1_EV_IRQHandler,Default_Handler + + .weak I2C1_ER_IRQHandler + .thumb_set I2C1_ER_IRQHandler,Default_Handler + + .weak I2C2_EV_IRQHandler + .thumb_set I2C2_EV_IRQHandler,Default_Handler + + .weak I2C2_ER_IRQHandler + .thumb_set I2C2_ER_IRQHandler,Default_Handler + + .weak SPI1_IRQHandler + .thumb_set SPI1_IRQHandler,Default_Handler + + .weak SPI2_IRQHandler + .thumb_set SPI2_IRQHandler,Default_Handler + + .weak USART1_IRQHandler + .thumb_set USART1_IRQHandler,Default_Handler + + .weak USART2_IRQHandler + .thumb_set USART2_IRQHandler,Default_Handler + + .weak EXTI15_10_IRQHandler + .thumb_set EXTI15_10_IRQHandler,Default_Handler + + .weak RTC_Alarm_IRQHandler + .thumb_set RTC_Alarm_IRQHandler,Default_Handler + + .weak OTG_FS_WKUP_IRQHandler + .thumb_set OTG_FS_WKUP_IRQHandler,Default_Handler + + .weak DMA1_Stream7_IRQHandler + .thumb_set DMA1_Stream7_IRQHandler,Default_Handler + + .weak SDIO_IRQHandler + .thumb_set SDIO_IRQHandler,Default_Handler + + .weak TIM5_IRQHandler + .thumb_set TIM5_IRQHandler,Default_Handler + + .weak SPI3_IRQHandler + .thumb_set SPI3_IRQHandler,Default_Handler + + .weak DMA2_Stream0_IRQHandler + .thumb_set DMA2_Stream0_IRQHandler,Default_Handler + + .weak DMA2_Stream1_IRQHandler + .thumb_set DMA2_Stream1_IRQHandler,Default_Handler + + .weak DMA2_Stream2_IRQHandler + .thumb_set DMA2_Stream2_IRQHandler,Default_Handler + + .weak DMA2_Stream3_IRQHandler + .thumb_set DMA2_Stream3_IRQHandler,Default_Handler + + .weak DMA2_Stream4_IRQHandler + .thumb_set DMA2_Stream4_IRQHandler,Default_Handler + + .weak OTG_FS_IRQHandler + .thumb_set OTG_FS_IRQHandler,Default_Handler + + .weak DMA2_Stream5_IRQHandler + .thumb_set DMA2_Stream5_IRQHandler,Default_Handler + + .weak DMA2_Stream6_IRQHandler + .thumb_set DMA2_Stream6_IRQHandler,Default_Handler + + .weak DMA2_Stream7_IRQHandler + .thumb_set DMA2_Stream7_IRQHandler,Default_Handler + + .weak USART6_IRQHandler + .thumb_set USART6_IRQHandler,Default_Handler + + .weak I2C3_EV_IRQHandler + .thumb_set I2C3_EV_IRQHandler,Default_Handler + + .weak I2C3_ER_IRQHandler + .thumb_set I2C3_ER_IRQHandler,Default_Handler + + .weak FPU_IRQHandler + .thumb_set FPU_IRQHandler,Default_Handler + + .weak SPI4_IRQHandler + .thumb_set SPI4_IRQHandler,Default_Handler + + .weak SPI5_IRQHandler + .thumb_set SPI5_IRQHandler,Default_Handler + +/************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/ + +

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/TARGET_BLACKPILL/TOOLCHAIN_GCC_ARM/stm32f411xe.ld Wed Apr 14 08:21:15 2021 +0000

@@ -0,0 +1,218 @@

+/* Linker script to configure memory regions. */

+/*

+ * SPDX-License-Identifier: BSD-3-Clause

+ ******************************************************************************

+ * @attention

+ *

+ * Copyright (c) 2016-2020 STMicroelectronics.

+ * All rights reserved.

+ *

+ * This software component is licensed by ST under BSD 3-Clause license,

+ * the "License"; You may not use this file except in compliance with the

+ * License. You may obtain a copy of the License at:

+ * opensource.org/licenses/BSD-3-Clause

+ *

+ ******************************************************************************

+*/

+

+#include "../cmsis_nvic.h"

+

+

+#if !defined(MBED_APP_START)

+ #define MBED_APP_START MBED_ROM_START

+#endif

+

+#if !defined(MBED_APP_SIZE)

+ #define MBED_APP_SIZE MBED_ROM_SIZE

+#endif

+

+#if !defined(MBED_CONF_TARGET_BOOT_STACK_SIZE)

+ /* This value is normally defined by the tools

+ to 0x1000 for bare metal and 0x400 for RTOS */

+ #define MBED_CONF_TARGET_BOOT_STACK_SIZE 0x400

+#endif

+

+/* Round up VECTORS_SIZE to 8 bytes */

+#define VECTORS_SIZE (((NVIC_NUM_VECTORS * 4) + 7) & 0xFFFFFFF8)

+

+M_CRASH_DATA_RAM_SIZE = 0x100;

+

+MEMORY

+{

+ FLASH (rx) : ORIGIN = MBED_APP_START, LENGTH = MBED_APP_SIZE

+ RAM (rwx) : ORIGIN = MBED_RAM_START + VECTORS_SIZE, LENGTH = MBED_RAM_SIZE - VECTORS_SIZE

+}

+

+/* Linker script to place sections and symbol values. Should be used together

+ * with other linker script that defines memory regions FLASH and RAM.

+ * It references following symbols, which must be defined in code:

+ * Reset_Handler : Entry of reset handler

+ *

+ * It defines following symbols, which code can use without definition:

+ * __exidx_start

+ * __exidx_end

+ * __etext

+ * __data_start__

+ * __preinit_array_start

+ * __preinit_array_end

+ * __init_array_start

+ * __init_array_end

+ * __fini_array_start

+ * __fini_array_end

+ * __data_end__

+ * __bss_start__

+ * __bss_end__

+ * __end__

+ * end

+ * __HeapLimit

+ * __StackLimit

+ * __StackTop

+ * __stack

+ * _estack

+ */

+ENTRY(Reset_Handler)

+

+SECTIONS

+{

+ .text :

+ {

+ KEEP(*(.isr_vector))

+ *(.text*)

+

+ KEEP(*(.init))

+ KEEP(*(.fini))

+

+ /* .ctors */

+ *crtbegin.o(.ctors)

+ *crtbegin?.o(.ctors)

+ *(EXCLUDE_FILE(*crtend?.o *crtend.o) .ctors)

+ *(SORT(.ctors.*))

+ *(.ctors)

+

+ /* .dtors */

+ *crtbegin.o(.dtors)

+ *crtbegin?.o(.dtors)

+ *(EXCLUDE_FILE(*crtend?.o *crtend.o) .dtors)

+ *(SORT(.dtors.*))

+ *(.dtors)

+

+ *(.rodata*)

+

+ KEEP(*(.eh_frame*))

+ } > FLASH

+

+ .ARM.extab :

+ {

+ *(.ARM.extab* .gnu.linkonce.armextab.*)

+ } > FLASH

+

+ __exidx_start = .;

+ .ARM.exidx :

+ {

+ *(.ARM.exidx* .gnu.linkonce.armexidx.*)

+ } > FLASH

+ __exidx_end = .;

+

+ __etext = .;

+ _sidata = .;

+

+ .crash_data_ram :

+ {

+ . = ALIGN(8);

+ __CRASH_DATA_RAM__ = .;

+ __CRASH_DATA_RAM_START__ = .; /* Create a global symbol at data start */

+ KEEP(*(.keep.crash_data_ram))

+ *(.m_crash_data_ram) /* This is a user defined section */

+ . += M_CRASH_DATA_RAM_SIZE;

+ . = ALIGN(8);

+ __CRASH_DATA_RAM_END__ = .; /* Define a global symbol at data end */

+ } > RAM

+

+ .data : AT (__etext)

+ {

+ __data_start__ = .;

+ _sdata = .;

+ *(vtable)

+ *(.data*)

+

+ . = ALIGN(8);

+ /* preinit data */

+ PROVIDE_HIDDEN (__preinit_array_start = .);

+ KEEP(*(.preinit_array))

+ PROVIDE_HIDDEN (__preinit_array_end = .);

+

+ . = ALIGN(8);

+ /* init data */

+ PROVIDE_HIDDEN (__init_array_start = .);

+ KEEP(*(SORT(.init_array.*)))

+ KEEP(*(.init_array))

+ PROVIDE_HIDDEN (__init_array_end = .);

+

+ . = ALIGN(8);

+ /* finit data */

+ PROVIDE_HIDDEN (__fini_array_start = .);

+ KEEP(*(SORT(.fini_array.*)))

+ KEEP(*(.fini_array))

+ PROVIDE_HIDDEN (__fini_array_end = .);

+

+ KEEP(*(.jcr*))

+ . = ALIGN(8);

+ /* All data end */

+ __data_end__ = .;

+ _edata = .;

+

+ } > RAM

+

+ /* Uninitialized data section

+ * This region is not initialized by the C/C++ library and can be used to

+ * store state across soft reboots. */

+ .uninitialized (NOLOAD):

+ {

+ . = ALIGN(32);

+ __uninitialized_start = .;

+ *(.uninitialized)

+ KEEP(*(.keep.uninitialized))

+ . = ALIGN(32);

+ __uninitialized_end = .;

+ } > RAM

+

+ .bss :

+ {

+ . = ALIGN(8);

+ __bss_start__ = .;

+ _sbss = .;

+ *(.bss*)

+ *(COMMON)

+ . = ALIGN(8);

+ __bss_end__ = .;

+ _ebss = .;

+ } > RAM

+

+ .heap (COPY):

+ {

+ __end__ = .;

+ PROVIDE(end = .);

+ *(.heap*)

+ . = ORIGIN(RAM) + LENGTH(RAM) - MBED_CONF_TARGET_BOOT_STACK_SIZE;

+ __HeapLimit = .;

+ } > RAM

+

+ /* .stack_dummy section doesn't contains any symbols. It is only

+ * used for linker to calculate size of stack sections, and assign

+ * values to stack symbols later */

+ .stack_dummy (COPY):

+ {

+ *(.stack*)

+ } > RAM

+

+ /* Set stack top to end of RAM, and stack limit move down by

+ * size of stack_dummy section */

+ __StackTop = ORIGIN(RAM) + LENGTH(RAM);

+ _estack = __StackTop;

+ __StackLimit = __StackTop - MBED_CONF_TARGET_BOOT_STACK_SIZE;

+ PROVIDE(__stack = __StackTop);

+

+ /* Check if data + heap + stack exceeds RAM limit */

+ ASSERT(__StackLimit >= __HeapLimit, "region RAM overflowed with stack")

+}

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/TARGET_BLACKPILL/cmsis_nvic.h Wed Apr 14 08:21:15 2021 +0000 @@ -0,0 +1,40 @@ +/* mbed Microcontroller Library + * SPDX-License-Identifier: BSD-3-Clause + ****************************************************************************** + * @attention + * + * <h2><center>© Copyright (c) 2016-2020 STMicroelectronics. + * All rights reserved.</center></h2> + * + * This software component is licensed by ST under BSD 3-Clause license, + * the "License"; You may not use this file except in compliance with the + * License. You may obtain a copy of the License at: + * opensource.org/licenses/BSD-3-Clause + * + ****************************************************************************** +*/ + +#ifndef MBED_CMSIS_NVIC_H +#define MBED_CMSIS_NVIC_H + +#if !defined(MBED_ROM_START) +#define MBED_ROM_START 0x8000000 +#endif + +#if !defined(MBED_ROM_SIZE) +#define MBED_ROM_SIZE 0x80000 // 512 KB +#endif + +#if !defined(MBED_RAM_START) +#define MBED_RAM_START 0x20000000 +#endif + +#if !defined(MBED_RAM_SIZE) +#define MBED_RAM_SIZE 0x20000 // 128 KB +#endif + +#define NVIC_NUM_VECTORS 102 +#define NVIC_RAM_VECTOR_ADDRESS MBED_RAM_START + +#endif +

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/TARGET_BLACKPILL/flash_data.h Wed Apr 14 08:21:15 2021 +0000 @@ -0,0 +1,56 @@ +/* mbed Microcontroller Library + ******************************************************************************* + * Copyright (c) 2016, STMicroelectronics + * All rights reserved. + * + * Redistribution and use in source and binary forms, with or without + * modification, are permitted provided that the following conditions are met: + * + * 1. Redistributions of source code must retain the above copyright notice, + * this list of conditions and the following disclaimer. + * 2. Redistributions in binary form must reproduce the above copyright notice, + * this list of conditions and the following disclaimer in the documentation + * and/or other materials provided with the distribution. + * 3. Neither the name of STMicroelectronics nor the names of its contributors + * may be used to endorse or promote products derived from this software + * without specific prior written permission. + * + * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" + * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE + * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE + * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE + * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL + * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR + * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER + * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, + * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE + * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. + ******************************************************************************* + */ +#ifndef MBED_FLASH_DATA_H +#define MBED_FLASH_DATA_H + +#include "device.h" +#include <stdint.h> + +#if DEVICE_FLASH + +/* Exported types ------------------------------------------------------------*/ +/* Exported constants --------------------------------------------------------*/ +/* Exported macro ------------------------------------------------------------*/ +/* FLASH SIZE */ +#define FLASH_SIZE (uint32_t) 0x80000 + +/* Base address of the Flash sectors Bank 1 */ +#define ADDR_FLASH_SECTOR_0 ((uint32_t)0x08000000) /* Base @ of Sector 0, 16 Kbytes */ +#define ADDR_FLASH_SECTOR_1 ((uint32_t)0x08004000) /* Base @ of Sector 1, 16 Kbytes */ +#define ADDR_FLASH_SECTOR_2 ((uint32_t)0x08008000) /* Base @ of Sector 2, 16 Kbytes */ +#define ADDR_FLASH_SECTOR_3 ((uint32_t)0x0800C000) /* Base @ of Sector 3, 16 Kbytes */ +#define ADDR_FLASH_SECTOR_4 ((uint32_t)0x08010000) /* Base @ of Sector 4, 64 Kbytes */ +#define ADDR_FLASH_SECTOR_5 ((uint32_t)0x08020000) /* Base @ of Sector 5, 128 Kbytes */ +#define ADDR_FLASH_SECTOR_6 ((uint32_t)0x08040000) /* Base @ of Sector 6, 128 Kbytes */ +#define ADDR_FLASH_SECTOR_7 ((uint32_t)0x08060000) /* Base @ of Sector 7, 128 Kbytes */ + +#endif +#endif +

--- a/TARGET_BLACKPILL/system_clock.c Fri Apr 02 07:37:35 2021 +0000

+++ b/TARGET_BLACKPILL/system_clock.c Wed Apr 14 08:21:15 2021 +0000

@@ -186,3 +186,4 @@

return 1; // OK

}

#endif /* ((CLOCK_SOURCE) & USE_PLL_HSI) */

+

--- a/custom_targets.json Fri Apr 02 07:37:35 2021 +0000

+++ b/custom_targets.json Wed Apr 14 08:21:15 2021 +0000

@@ -1,10 +1,13 @@

"BLACKPILL": {

"inherits": [

- "MCU_STM32F411xE"

+ "MCU_STM32F4"

+ ],

+ "macros_add": [

+ "STM32F411xE"

],

"config": {

"clock_source_usb": {

- "help": "As 48 Mhz clock is configured for USB, SYSCLK has to be reduced from 100 to 60 MHz (set 1 for USB)",

+ "help": "When set 1 (to use USB) the SYSCLK is reduced from 100 to 60 MHz.",

"value": "0",

"macro_name": "CLOCK_SOURCE_USB"

}

@@ -20,5 +23,5 @@

"detect_code": [

"0740"

],

- "device_name": "STM32F411CE"

+ "device_name": "MCU_STM32F411CE"

}