Lib to change the clock speed of the ST Nucleo L152RE board to 32 MHz.

The ST Nucleo L152 board is running on 16 MHz out of the box. To speed up the cpu to the maximum 32MHz speed we have to change the clock setting. Simply add the lib and :

#include "ST_L152_32MHZ.h"

L152_init32 myinit(0); // use the internal oscillator

in front of your program. This should be the first line in main to ensure the frequency is changed before other objects are initialised.

This frequency is generated out of the internal RC oscillator. The frequency is not so stable like a crystal. The PLL is switched to 96MHz to enable the use of the USB interface.

If you need a more precise timing source, you have to add a external crystal.

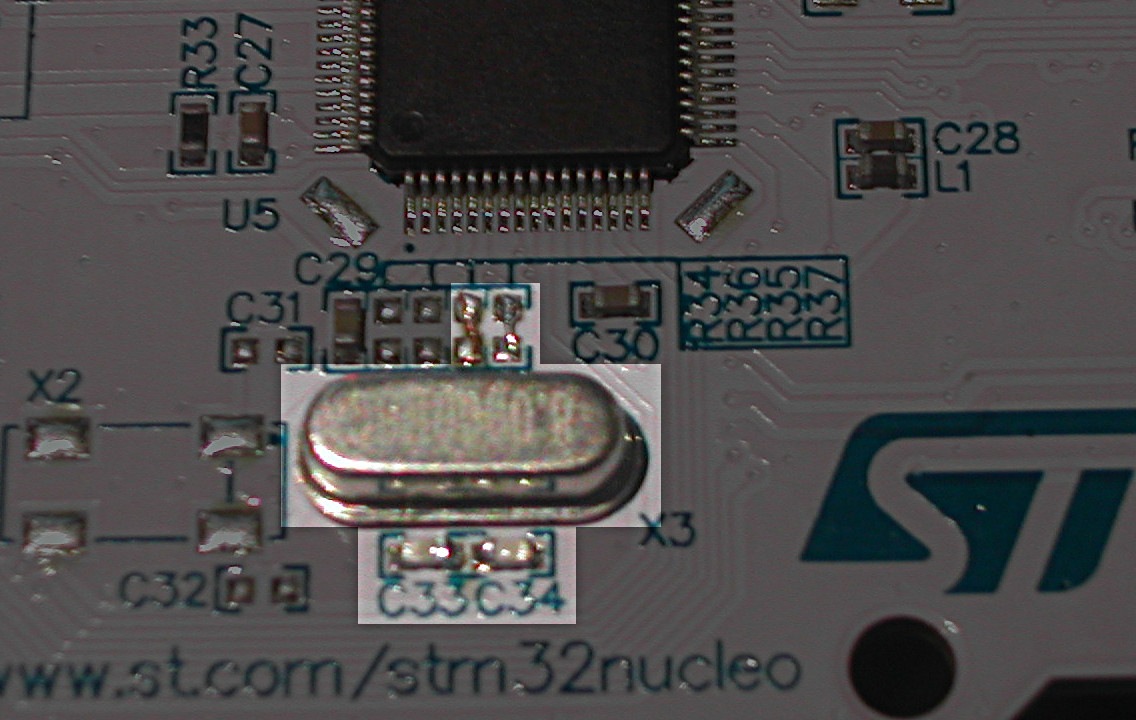

You need : X3 8MHz crystal , C33 and C34 18pF 0603 , R35 and R37 have to be short with a small piece of wire.

#include "ST_L152_32MHZ.h"

L152_init32 myinit(1); // use external crystal oscillator

Revision 2:9e2ba1d93567, committed 2014-03-19

- Comitter:

- dreschpe

- Date:

- Wed Mar 19 18:07:11 2014 +0000

- Parent:

- 1:bdeac50afe1a

- Child:

- 3:1e82f1f333ad

- Commit message:

- Fix setup

Changed in this revision

| ST_L152_32MHZ.cpp | Show annotated file Show diff for this revision Revisions of this file |

--- a/ST_L152_32MHZ.cpp Tue Mar 11 21:03:03 2014 +0000

+++ b/ST_L152_32MHZ.cpp Wed Mar 19 18:07:11 2014 +0000

@@ -30,28 +30,71 @@

{

uint32_t PLLStartUpCounter = 0,PLLStatus = 0,error;

- if(external == 0) { // internal Oscillator

- RCC_PLLConfig(RCC_PLLSource_HSI,RCC_PLLMul_6,RCC_PLLDiv_3); // setup pll to 96MHz to use USB

- } else {

- RCC_HSEConfig(RCC_HSE_ON); // start external crystal osc.

+

+/* Enable 64-bit access */

+ FLASH->ACR |= FLASH_ACR_ACC64;

+

+ /* Enable Prefetch Buffer */

+ FLASH->ACR |= FLASH_ACR_PRFTEN;

+

+ /* Flash 1 wait state */

+ FLASH->ACR |= FLASH_ACR_LATENCY;

+

+ /* Power enable */

+ RCC->APB1ENR |= RCC_APB1ENR_PWREN;

+

+ /* Select the Voltage Range 1 (1.8 V) */

+ PWR->CR = PWR_CR_VOS_0;

+

+ /* Wait Until the Voltage Regulator is ready */

+ while((PWR->CSR & PWR_CSR_VOSF) != RESET)

+ {

+ }

+

+ /* HCLK = SYSCLK /1*/

+ RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

+ /* PCLK2 = HCLK /1*/

+ RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

+

+ /* PCLK1 = HCLK /1*/

+ RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1;

+

+ /* PLL configuration */

+ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMUL |

+ RCC_CFGR_PLLDIV));

+

+ if(external == 0){

+ RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSI | RCC_CFGR_PLLMUL6 | RCC_CFGR_PLLDIV3);

+ }

+ else{

+ RCC_HSEConfig(RCC_HSE_ON); // start external crystal osc.

error = RCC_WaitForHSEStartUp();

if(error == ERROR ) { // no external crystal

return(EXT_ERR);

- }

- RCC_PLLConfig(RCC_PLLSource_HSE,RCC_PLLMul_12,RCC_PLLDiv_3); // setup pll to 96MHz to use USB

- }

- RCC_PLLCmd(ENABLE); // switch on pll

+ }

+ RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMUL12 | RCC_CFGR_PLLDIV3);

+ }

+

+ /* Enable PLL */

+ RCC->CR |= RCC_CR_PLLON;

+

+ /* Wait till PLL is ready */

do {

PLLStatus = RCC->CR & RCC_CR_PLLRDY;

} while((PLLStatus == 0) && (PLLStartUpCounter < PLL_STARTUP_TIMEOUT)); // wait for pll

if(PLLStatus == 0) {

return(PLL_ERR);

}

- FLASH_SetLatency(FLASH_Latency_1);

- FLASH_PrefetchBufferCmd(ENABLE);

- FLASH_ReadAccess64Cmd(ENABLE);

- RCC_HCLKConfig(RCC_SYSCLK_Div2);

- RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); // switch to 32 MHz clock

+

+ /* Select PLL as system clock source */

+ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

+ RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

+

+ /* Wait till PLL is used as system clock source */

+ while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL)

+ {

+ }

SystemCoreClockUpdate(); // update SystemCoreClock var

return(OK);

-}

\ No newline at end of file

+}

+