Lib for FTDI FT800 graphic controller "EVE" The API is changed from the FTDI original names. It use smaller names now. DL() will add something to the display list instead of Ft_App_WrCoCmd_Buffer ... The FTDI programmer Guide is also using this commands.

Dependents: FT800_RGB_demo FT800_RGB_demo2 FT800_demo_for_habr Temp_&_RH_at_TFT-demo ... more

Fork of FT800 by

The mbed is talking thru the SPI interface with the graphic engine. We have to set up a list of Commands and send them to the FT800 to get graphics.

Hardware

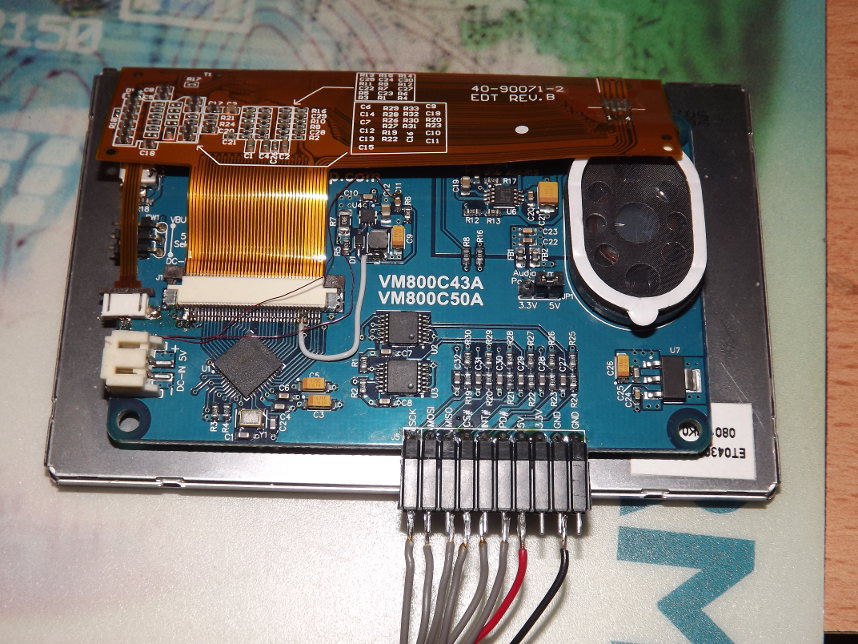

1. VM800C development modules from FTDI : http://www.ftdichip.com/Products/Modules/VM800C.html

The modules come with different size lcd. 3.5", 4.3" or 5" or without.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

The picture shows a modified board, because my lcd had a different pinout. The mbed is connected to the pin header on the bottom.

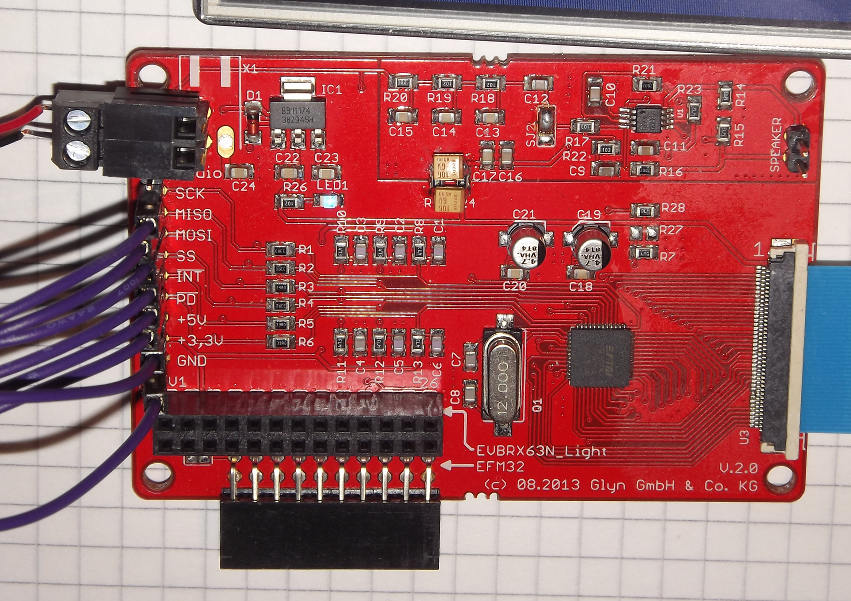

2. EVBEVE-FT800 board from GLYN: http://www.glyn.com/News-Events/Newsletter/Newsletter-2013/October-2013/A-quick-start-for-EVE-Requires-no-basic-knowledge-graphics-sound-and-touch-can-all-be-learned-in-minutes

The module has a 40 pin flex cable connector to connect a display out of the EDT series.

The mbed is connected via the pin header on the left. If you use this board with a EDT display you have to uncomment the #define Inv_Backlite in FT_LCD_Type.h, because the backlight dimming is inverted.

3. ConnectEVE board from MikroElektronika http://www.mikroe.com/add-on-boards/display/connecteve/#headers_10 The board has also a pin header to connect the mbed. - not tested, but it looks like the other boards.

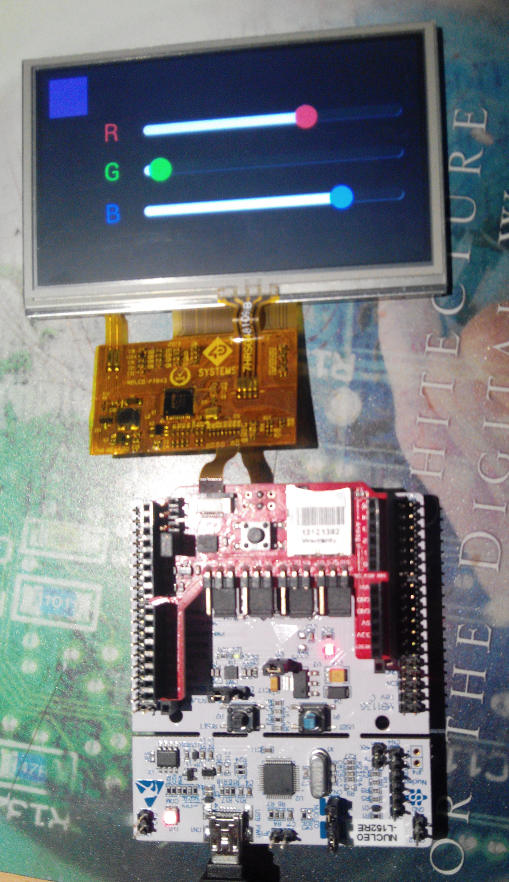

4. ADAM arduino shield http://www.4dsystems.com.au/product/4DLCD_FT843/ Component page : http://mbed.org/components/ADAM/

Works with the NUCLEO boards, but you have to patch three wires.

Connection

We need 5 signals to connect to the mbed. SCK, MOSI and MISO are connected to a SPI channel. SS is the chip select signal and PD work as powerdown. The additional INT signal is not used at the moment. It is possible to generate a interrupt signal, but at the moment you have to poll the status register of the FT800 to see if a command is finished.

Software

This lib is based on the demo code from FTDI. If you want to use it, you have to read the programming manual : http://www.ftdichip.com/Support/Documents/ProgramGuides/FT800%20Programmers%20Guide.pdf

See my demo : http://mbed.org/users/dreschpe/code/FT800_RGB_demo/

Revision 0:5e013296b353, committed 2014-01-03

- Comitter:

- dreschpe

- Date:

- Fri Jan 03 15:26:10 2014 +0000

- Child:

- 1:bd671a31e765

- Commit message:

- Lib for FTDI FT800 Graphic Controller EVE

Changed in this revision

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/FT_CoPro_Cmds.cpp Fri Jan 03 15:26:10 2014 +0000

@@ -0,0 +1,535 @@

+

+#include "FT_Platform.h"

+//#include "FT_Gpu_Hal.h"

+

+

+ft_void_t FT800::Ft_Gpu_Copro_SendCmd( ft_uint32_t cmd)

+{

+ Ft_Gpu_Hal_Transfer32( cmd);

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_SendStr( const ft_char8_t *s)

+{

+ Ft_Gpu_Hal_TransferString( s);

+}

+

+

+ft_void_t FT800::Ft_Gpu_CoCmd_StartFunc( ft_uint16_t count)

+{

+ Ft_Gpu_Hal_CheckCmdBuffer( count);

+ Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_WRITE,count);

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_EndFunc( ft_uint16_t count)

+{

+ Ft_Gpu_Hal_EndTransfer( );

+ Ft_Gpu_Hal_Updatecmdfifo( count);

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Text( ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3 + strlen(s) + 1);

+ Ft_Gpu_Copro_SendCmd( CMD_TEXT);

+ //Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(ft_uint32_t)x));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|(ft_uint32_t)font));

+ Ft_Gpu_CoCmd_SendStr( s);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3 + strlen(s) + 1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Number( ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, ft_int32_t n)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4);

+ Ft_Gpu_Copro_SendCmd( CMD_NUMBER);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|font));

+ Ft_Gpu_Copro_SendCmd( n);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_LoadIdentity( )

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_LOADIDENTITY);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Toggle( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t font, ft_uint16_t options, ft_uint16_t state, const ft_char8_t* s)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4 + strlen(s) + 1);

+ Ft_Gpu_Copro_SendCmd( CMD_TOGGLE);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)font<<16)|w));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)state<<16)|options));

+ Ft_Gpu_CoCmd_SendStr( s);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4 + strlen(s) + 1));

+}

+

+/* Error handling for val is not done, so better to always use range of 65535 in order that needle is drawn within display region */

+ft_void_t FT800::Ft_Gpu_CoCmd_Gauge( ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t major, ft_uint16_t minor, ft_uint16_t val, ft_uint16_t range)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5);

+ Ft_Gpu_Copro_SendCmd( CMD_GAUGE);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|r));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)minor<<16)|major));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)range<<16)|val));

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_RegRead( ft_uint32_t ptr, ft_uint32_t result)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_REGREAD);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( 0);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_GetProps( ft_uint32_t ptr, ft_uint32_t w, ft_uint32_t h)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4);

+ Ft_Gpu_Copro_SendCmd( CMD_GETPROPS);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( w);

+ Ft_Gpu_Copro_SendCmd( h);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Memcpy( ft_uint32_t dest, ft_uint32_t src, ft_uint32_t num)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4);

+ Ft_Gpu_Copro_SendCmd( CMD_MEMCPY);

+ Ft_Gpu_Copro_SendCmd( dest);

+ Ft_Gpu_Copro_SendCmd( src);

+ Ft_Gpu_Copro_SendCmd( num);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Spinner( ft_int16_t x, ft_int16_t y, ft_uint16_t style, ft_uint16_t scale)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_SPINNER);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)scale<<16)|style));

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_BgColor( ft_uint32_t c)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_BGCOLOR);

+ Ft_Gpu_Copro_SendCmd( c);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Swap()

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_SWAP);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Inflate( ft_uint32_t ptr)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_INFLATE);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Translate( ft_int32_t tx, ft_int32_t ty)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_TRANSLATE);

+ Ft_Gpu_Copro_SendCmd( tx);

+ Ft_Gpu_Copro_SendCmd( ty);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Stop()

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_STOP);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Slider( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5);

+ Ft_Gpu_Copro_SendCmd( CMD_SLIDER);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)val<<16)|options));

+ Ft_Gpu_Copro_SendCmd( range);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_TouchTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*6*2+FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_TOUCH_TRANSFORM);

+ Ft_Gpu_Copro_SendCmd( x0);

+ Ft_Gpu_Copro_SendCmd( y0);

+ Ft_Gpu_Copro_SendCmd( x1);

+ Ft_Gpu_Copro_SendCmd( y1);

+ Ft_Gpu_Copro_SendCmd( x2);

+ Ft_Gpu_Copro_SendCmd( y2);

+ Ft_Gpu_Copro_SendCmd( tx0);

+ Ft_Gpu_Copro_SendCmd( ty0);

+ Ft_Gpu_Copro_SendCmd( tx1);

+ Ft_Gpu_Copro_SendCmd( ty1);

+ Ft_Gpu_Copro_SendCmd( tx2);

+ Ft_Gpu_Copro_SendCmd( ty2);

+ Ft_Gpu_Copro_SendCmd( result);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*6*2+FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Interrupt( ft_uint32_t ms)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_INTERRUPT);

+ Ft_Gpu_Copro_SendCmd( ms);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_FgColor( ft_uint32_t c)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_FGCOLOR);

+ Ft_Gpu_Copro_SendCmd( c);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Rotate( ft_int32_t a)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_ROTATE);

+ Ft_Gpu_Copro_SendCmd( a);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Button( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4 + strlen(s) + 1);

+ Ft_Gpu_Copro_SendCmd( CMD_BUTTON);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|font));

+ Ft_Gpu_CoCmd_SendStr( s);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4 + strlen(s) + 1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_MemWrite( ft_uint32_t ptr, ft_uint32_t num)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_MEMWRITE);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( num);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Scrollbar( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t size, ft_uint16_t range)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5);

+ Ft_Gpu_Copro_SendCmd( CMD_SCROLLBAR);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)val<<16)|options));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)range<<16)|size));

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_GetMatrix( ft_int32_t a, ft_int32_t b, ft_int32_t c, ft_int32_t d, ft_int32_t e, ft_int32_t f)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*7);

+ Ft_Gpu_Copro_SendCmd( CMD_GETMATRIX);

+ Ft_Gpu_Copro_SendCmd( a);

+ Ft_Gpu_Copro_SendCmd( b);

+ Ft_Gpu_Copro_SendCmd( c);

+ Ft_Gpu_Copro_SendCmd( d);

+ Ft_Gpu_Copro_SendCmd( e);

+ Ft_Gpu_Copro_SendCmd( f);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*7));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Sketch( ft_int16_t x, ft_int16_t y, ft_uint16_t w, ft_uint16_t h, ft_uint32_t ptr, ft_uint16_t format)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5);

+ Ft_Gpu_Copro_SendCmd( CMD_SKETCH);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w));

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( format);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_MemSet( ft_uint32_t ptr, ft_uint32_t value, ft_uint32_t num)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4);

+ Ft_Gpu_Copro_SendCmd( CMD_MEMSET);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( value);

+ Ft_Gpu_Copro_SendCmd( num);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_GradColor( ft_uint32_t c)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_GRADCOLOR);

+ Ft_Gpu_Copro_SendCmd( c);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_BitmapTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*6*2+FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_BITMAP_TRANSFORM);

+ Ft_Gpu_Copro_SendCmd( x0);

+ Ft_Gpu_Copro_SendCmd( y0);

+ Ft_Gpu_Copro_SendCmd( x1);

+ Ft_Gpu_Copro_SendCmd( y1);

+ Ft_Gpu_Copro_SendCmd( x2);

+ Ft_Gpu_Copro_SendCmd( y2);

+ Ft_Gpu_Copro_SendCmd( tx0);

+ Ft_Gpu_Copro_SendCmd( ty0);

+ Ft_Gpu_Copro_SendCmd( tx1);

+ Ft_Gpu_Copro_SendCmd( ty1);

+ Ft_Gpu_Copro_SendCmd( tx2);

+ Ft_Gpu_Copro_SendCmd( ty2);

+ Ft_Gpu_Copro_SendCmd( result);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*6*2+FT_CMD_SIZE*2));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_Calibrate( ft_uint32_t result)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_CALIBRATE);

+ Ft_Gpu_Copro_SendCmd( result);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+ Ft_Gpu_Hal_WaitCmdfifo_empty( );

+

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_SetFont( ft_uint32_t font, ft_uint32_t ptr)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_SETFONT);

+ Ft_Gpu_Copro_SendCmd( font);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_Logo( )

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_LOGO);

+ Ft_Gpu_CoCmd_EndFunc( FT_CMD_SIZE*1);

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_Append( ft_uint32_t ptr, ft_uint32_t num)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_APPEND);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( num);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_MemZero( ft_uint32_t ptr, ft_uint32_t num)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_MEMZERO);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( num);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_Scale( ft_int32_t sx, ft_int32_t sy)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_SCALE);

+ Ft_Gpu_Copro_SendCmd( sx);

+ Ft_Gpu_Copro_SendCmd( sy);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+ft_void_t FT800::Ft_Gpu_CoCmd_Clock( ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t h, ft_uint16_t m, ft_uint16_t s, ft_uint16_t ms)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5);

+ Ft_Gpu_Copro_SendCmd( CMD_CLOCK);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|r));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)m<<16)|h));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)ms<<16)|s));

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Gradient( ft_int16_t x0, ft_int16_t y0, ft_uint32_t rgb0, ft_int16_t x1, ft_int16_t y1, ft_uint32_t rgb1)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5);

+ Ft_Gpu_Copro_SendCmd( CMD_GRADIENT);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y0<<16)|(x0 & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( rgb0);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y1<<16)|(x1 & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( rgb1);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_SetMatrix( )

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_SETMATRIX);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Track( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t tag)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4);

+ Ft_Gpu_Copro_SendCmd( CMD_TRACK);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w));

+ Ft_Gpu_Copro_SendCmd( tag);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_GetPtr( ft_uint32_t result)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_GETPTR);

+ Ft_Gpu_Copro_SendCmd( result);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Progress( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*5);

+ Ft_Gpu_Copro_SendCmd( CMD_PROGRESS);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)val<<16)|options));

+ Ft_Gpu_Copro_SendCmd( range);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*5));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_ColdStart( )

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_COLDSTART);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Keys( ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4 + strlen(s) + 1);

+ Ft_Gpu_Copro_SendCmd( CMD_KEYS);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)h<<16)|w));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|font));

+ Ft_Gpu_CoCmd_SendStr( s);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4 + strlen(s) + 1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Dial( ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t val)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4);

+ Ft_Gpu_Copro_SendCmd( CMD_DIAL);

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)y<<16)|(x & 0xffff)));

+ Ft_Gpu_Copro_SendCmd( (((ft_uint32_t)options<<16)|r));

+ Ft_Gpu_Copro_SendCmd( val);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_LoadImage( ft_uint32_t ptr, ft_uint32_t options)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*3);

+ Ft_Gpu_Copro_SendCmd( CMD_LOADIMAGE);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( options);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*3));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Dlstart( )

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_DLSTART);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_Snapshot( ft_uint32_t ptr)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*2);

+ Ft_Gpu_Copro_SendCmd( CMD_SNAPSHOT);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*2));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_ScreenSaver( )

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*1);

+ Ft_Gpu_Copro_SendCmd( CMD_SCREENSAVER);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*1));

+}

+

+ft_void_t FT800::Ft_Gpu_CoCmd_MemCrc( ft_uint32_t ptr, ft_uint32_t num, ft_uint32_t result)

+{

+ Ft_Gpu_CoCmd_StartFunc( FT_CMD_SIZE*4);

+ Ft_Gpu_Copro_SendCmd( CMD_MEMCRC);

+ Ft_Gpu_Copro_SendCmd( ptr);

+ Ft_Gpu_Copro_SendCmd( num);

+ Ft_Gpu_Copro_SendCmd( result);

+ Ft_Gpu_CoCmd_EndFunc( (FT_CMD_SIZE*4));

+}

+

+

+ft_void_t FT800::Ft_App_WrCoCmd_Buffer(ft_uint32_t cmd)

+{

+ Ft_Gpu_Hal_WrCmd32(cmd);

+ /* Increment the command index */

+ Ft_CmdBuffer_Index += FT_CMD_SIZE;

+}

+

+ft_void_t FT800::Ft_App_WrDlCmd_Buffer(ft_uint32_t cmd)

+{

+ Ft_Gpu_Hal_Wr32((RAM_DL+Ft_DlBuffer_Index),cmd);

+ /* Increment the command index */

+ Ft_DlBuffer_Index += FT_CMD_SIZE;

+}

+

+ft_void_t FT800::Ft_App_Flush_DL_Buffer()

+{

+ Ft_DlBuffer_Index = 0;

+

+}

+

+ft_void_t FT800::Ft_App_Flush_Co_Buffer()

+{

+ Ft_CmdBuffer_Index = 0;

+}

+

+

+/* API to check the status of previous DLSWAP and perform DLSWAP of new DL */

+/* Check for the status of previous DLSWAP and if still not done wait for few ms and check again */

+ft_void_t FT800::GPU_DLSwap(ft_uint8_t DL_Swap_Type)

+{

+ ft_uint8_t Swap_Type = DLSWAP_FRAME,Swap_Done = DLSWAP_FRAME;

+

+ if(DL_Swap_Type == DLSWAP_LINE)

+ {

+ Swap_Type = DLSWAP_LINE;

+ }

+

+ /* Perform a new DL swap */

+ Ft_Gpu_Hal_Wr8(REG_DLSWAP,Swap_Type);

+

+ /* Wait till the swap is done */

+ while(Swap_Done)

+ {

+ Swap_Done = Ft_Gpu_Hal_Rd8(REG_DLSWAP);

+

+ if(DLSWAP_DONE != Swap_Done)

+ {

+ Ft_Gpu_Hal_Sleep(10);//wait for 10ms

+ }

+ }

+}

+

+

+

+/* Nothing beyond this */

+

+

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/FT_CoPro_Cmds.h Fri Jan 03 15:26:10 2014 +0000 @@ -0,0 +1,59 @@ +#ifndef _FT_COPRO_CMDS_H_ +#define _FT_COPRO_CMDS_H_ + +/* +ft_void_t Ft_Gpu_CoCmd_Text(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s); +ft_void_t Ft_Gpu_CoCmd_Number(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, ft_int32_t n); +ft_void_t Ft_Gpu_CoCmd_LoadIdentity(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Toggle(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t font, ft_uint16_t options, ft_uint16_t state, const ft_char8_t* s); +ft_void_t Ft_Gpu_CoCmd_Gauge(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t major, ft_uint16_t minor, ft_uint16_t val, ft_uint16_t range); +ft_void_t Ft_Gpu_CoCmd_RegRead(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t result); +ft_void_t Ft_Gpu_CoCmd_GetProps(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t w, ft_uint32_t h); +ft_void_t Ft_Gpu_CoCmd_Memcpy(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t dest, ft_uint32_t src, ft_uint32_t num); +ft_void_t Ft_Gpu_CoCmd_Spinner(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_uint16_t style, ft_uint16_t scale); +ft_void_t Ft_Gpu_CoCmd_BgColor(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t c); +ft_void_t Ft_Gpu_CoCmd_Swap(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Inflate(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr); +ft_void_t Ft_Gpu_CoCmd_Translate(Ft_Gpu_Hal_Context_t *phost,ft_int32_t tx, ft_int32_t ty); +ft_void_t Ft_Gpu_CoCmd_Stop(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Slider(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range); +ft_void_t Ft_Gpu_CoCmd_Interrupt(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ms); +ft_void_t Ft_Gpu_CoCmd_FgColor(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t c); +ft_void_t Ft_Gpu_CoCmd_Rotate(Ft_Gpu_Hal_Context_t *phost,ft_int32_t a); +ft_void_t Ft_Gpu_CoCmd_Button(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s); +ft_void_t Ft_Gpu_CoCmd_MemWrite(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t num); +ft_void_t Ft_Gpu_CoCmd_Scrollbar(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t size, ft_uint16_t range); +ft_void_t Ft_Gpu_CoCmd_GetMatrix(Ft_Gpu_Hal_Context_t *phost,ft_int32_t a, ft_int32_t b, ft_int32_t c, ft_int32_t d, ft_int32_t e, ft_int32_t f); +ft_void_t Ft_Gpu_CoCmd_Sketch(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_uint16_t w, ft_uint16_t h, ft_uint32_t ptr, ft_uint16_t format); +ft_void_t Ft_Gpu_CoCmd_MemSet(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t value, ft_uint32_t num); +ft_void_t Ft_Gpu_CoCmd_Calibrate(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t result); +ft_void_t Ft_Gpu_CoCmd_SetFont(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t font, ft_uint32_t ptr); +ft_void_t Ft_Gpu_CoCmd_Bitmap_Transform(Ft_Gpu_Hal_Context_t *phost,ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result); +ft_void_t Ft_Gpu_CoCmd_GradColor(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t c); +ft_void_t Ft_Gpu_CoCmd_Append(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t num); +ft_void_t Ft_Gpu_CoCmd_MemZero(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t num); +ft_void_t Ft_Gpu_CoCmd_Scale(Ft_Gpu_Hal_Context_t *phost,ft_int32_t sx, ft_int32_t sy); +ft_void_t Ft_Gpu_CoCmd_Clock(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t h, ft_uint16_t m, ft_uint16_t s, ft_uint16_t ms); +ft_void_t Ft_Gpu_CoCmd_Gradient(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x0, ft_int16_t y0, ft_uint32_t rgb0, ft_int16_t x1, ft_int16_t y1, ft_uint32_t rgb1); +ft_void_t Ft_Gpu_CoCmd_SetMatrix(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Track(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t tag); +ft_void_t Ft_Gpu_CoCmd_GetPtr(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t result); +ft_void_t Ft_Gpu_CoCmd_Progress(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range); +ft_void_t Ft_Gpu_CoCmd_ColdStart(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Keys(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s); +ft_void_t Ft_Gpu_CoCmd_Dial(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t val); +ft_void_t Ft_Gpu_CoCmd_LoadImage(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t options); +ft_void_t Ft_Gpu_CoCmd_Dlstart(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Snapshot(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr); +ft_void_t Ft_Gpu_CoCmd_ScreenSaver(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Memcrc(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t ptr, ft_uint32_t num, ft_uint32_t result); + + +ft_void_t Ft_Gpu_CoCmd_Logo(Ft_Gpu_Hal_Context_t *phost); +ft_void_t Ft_Gpu_CoCmd_Calibrate(Ft_Gpu_Hal_Context_t *phost,ft_uint32_t result); +ft_void_t Ft_Gpu_CoCmd_Text(Ft_Gpu_Hal_Context_t *phost,ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s); +*/ +#endif /*FT_COPRO_CMDS_H*/ + + +

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/FT_DataTypes.h Fri Jan 03 15:26:10 2014 +0000 @@ -0,0 +1,64 @@ +#ifndef _FT_DATATYPES_H_ +#define _FT_DATATYPES_H_ + + +#define FT_FALSE (0) +#define FT_TRUE (1) + +typedef char ft_char8_t; +typedef signed char ft_schar8_t; +typedef unsigned char ft_uchar8_t; +typedef ft_uchar8_t ft_uint8_t; +typedef short ft_int16_t; +typedef unsigned short ft_uint16_t; +typedef unsigned int ft_uint32_t; +typedef int ft_int32_t; +typedef void ft_void_t; +typedef long long ft_int64_t; +typedef unsigned long long ft_uint64_t; +typedef float ft_float_t; +typedef double ft_double_t; +typedef char ft_bool_t; + +#define FT_BYTE_SIZE (1) +#define FT_SHORT_SIZE (2) +#define FT_WORD_SIZE (4) +#define FT_DWORD_SIZE (8) + +#define FT_NUMBITS_IN_BYTE (1*8) +#define FT_NUMBITS_IN_SHORT (2*8) +#define FT_NUMBITS_IN_WORD (4*8) +#define FT_NUMBITS_IN_DWORD (8*8) + +#define ft_prog_uchar8_t ft_uchar8_t +#define ft_prog_char8_t ft_char8_t +#define ft_prog_uint16_t ft_uint16_t + +#define ft_random(x) (rand() % (x)) +//#define ft_millis() GetTickCount() + +#define ft_pgm_read_byte_near(x) (*(x)) +#define ft_pgm_read_byte(x) (*(x)) + +#define ft_strcpy_P strcpy +#define ft_strlen_P strlen + +#define FT_DBGPRINT(x) printf(x) +#define FT_PROGMEM + +#define ft_pgm_read_byte_near(x) (*(x)) +#define ft_pgm_read_byte(x) (*(x)) + +#define ft_pgm_read_word(addr) (*(ft_int16_t*)(addr)) + +#endif /*_FT_DATATYPES_H_*/ + + +/* Nothing beyond this*/ + + + + + + +

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/FT_Gpu.h Fri Jan 03 15:26:10 2014 +0000

@@ -0,0 +1,326 @@

+#ifndef _FT_GPU_H_

+#define _FT_GPU_H_

+

+/* Definitions used for FT800 co processor command buffer */

+#define FT_DL_SIZE (8*1024) //8KB Display List buffer size

+#define FT_CMD_FIFO_SIZE (4*1024) //4KB coprocessor Fifo size

+#define FT_CMD_SIZE (4) //4 byte per coprocessor command of EVE

+

+#define FT800_VERSION "1.9.0"

+#define ADC_DIFFERENTIAL 1UL

+#define ADC_SINGLE_ENDED 0UL

+#define ADPCM_SAMPLES 2UL

+#define ALWAYS 7UL

+#define ARGB1555 0UL

+#define ARGB2 5UL

+#define ARGB4 6UL

+#define BARGRAPH 11UL

+#define BILINEAR 1UL

+#define BITMAPS 1UL

+#define POINTS 2UL

+#define LINES 3UL

+#define LINE_STRIP 4UL

+#define EDGE_STRIP_R 5UL

+#define EDGE_STRIP_L 6UL

+#define EDGE_STRIP_A 7UL

+#define EDGE_STRIP_B 8UL

+#define RECTS 9UL

+#define BORDER 0UL

+

+#define CMDBUF_SIZE 4096UL

+#define CMD_APPEND 4294967070UL

+#define CMD_BGCOLOR 4294967049UL

+#define CMD_BITMAP_TRANSFORM 4294967073UL

+#define CMD_BUTTON 4294967053UL

+#define CMD_CALIBRATE 4294967061UL

+#define CMD_CLOCK 4294967060UL

+#define CMD_COLDSTART 4294967090UL

+#define CMD_CRC 4294967043UL

+#define CMD_DIAL 4294967085UL

+#define CMD_DLSTART 4294967040UL

+#define CMD_EXECUTE 4294967047UL

+#define CMD_FGCOLOR 4294967050UL

+#define CMD_GAUGE 4294967059UL

+#define CMD_GETMATRIX 4294967091UL

+#define CMD_GETPOINT 4294967048UL

+#define CMD_GETPROPS 4294967077UL

+#define CMD_GETPTR 4294967075UL

+#define CMD_GRADCOLOR 4294967092UL

+#define CMD_GRADIENT 4294967051UL

+#define CMD_HAMMERAUX 4294967044UL

+#define CMD_IDCT 4294967046UL

+#define CMD_INFLATE 4294967074UL

+#define CMD_INTERRUPT 4294967042UL

+#define CMD_KEYS 4294967054UL

+#define CMD_LOADIDENTITY 4294967078UL

+#define CMD_LOADIMAGE 4294967076UL

+#define CMD_LOGO 4294967089UL

+#define CMD_MARCH 4294967045UL

+#define CMD_MEMCPY 4294967069UL

+#define CMD_MEMCRC 4294967064UL

+#define CMD_MEMSET 4294967067UL

+#define CMD_MEMWRITE 4294967066UL

+#define CMD_MEMZERO 4294967068UL

+#define CMD_NUMBER 4294967086UL

+#define CMD_PROGRESS 4294967055UL

+#define CMD_REGREAD 4294967065UL

+#define CMD_ROTATE 4294967081UL

+#define CMD_SCALE 4294967080UL

+#define CMD_SCREENSAVER 4294967087UL

+#define CMD_SCROLLBAR 4294967057UL

+#define CMD_SETFONT 4294967083UL

+#define CMD_SETMATRIX 4294967082UL

+#define CMD_SKETCH 4294967088UL

+#define CMD_SLIDER 4294967056UL

+#define CMD_SNAPSHOT 4294967071UL

+#define CMD_SPINNER 4294967062UL

+#define CMD_STOP 4294967063UL

+#define CMD_SWAP 4294967041UL

+#define CMD_TEXT 4294967052UL

+#define CMD_TOGGLE 4294967058UL

+#define CMD_TOUCH_TRANSFORM 4294967072UL

+#define CMD_TRACK 4294967084UL

+#define CMD_TRANSLATE 4294967079UL

+

+#define DECR 4UL

+#define DECR_WRAP 7UL

+#define DLSWAP_DONE 0UL

+#define DLSWAP_FRAME 2UL

+#define DLSWAP_LINE 1UL

+#define DST_ALPHA 3UL

+#define EDGE_STRIP_A 7UL

+#define EDGE_STRIP_B 8UL

+#define EDGE_STRIP_L 6UL

+#define EDGE_STRIP_R 5UL

+#define EQUAL 5UL

+#define GEQUAL 4UL

+#define GREATER 3UL

+#define INCR 3UL

+#define INCR_WRAP 6UL

+#define INT_CMDEMPTY 32UL

+#define INT_CMDFLAG 64UL

+#define INT_CONVCOMPLETE 128UL

+#define INT_PLAYBACK 16UL

+#define INT_SOUND 8UL

+#define INT_SWAP 1UL

+#define INT_TAG 4UL

+#define INT_TOUCH 2UL

+#define INVERT 5UL

+

+#define KEEP 1UL

+#define L1 1UL

+#define L4 2UL

+#define L8 3UL

+#define LEQUAL 2UL

+#define LESS 1UL

+#define LINEAR_SAMPLES 0UL

+#define LINES 3UL

+#define LINE_STRIP 4UL

+#define NEAREST 0UL

+#define NEVER 0UL

+#define NOTEQUAL 6UL

+#define ONE 1UL

+#define ONE_MINUS_DST_ALPHA 5UL

+#define ONE_MINUS_SRC_ALPHA 4UL

+#define OPT_CENTER 1536UL

+#define OPT_CENTERX 512UL

+#define OPT_CENTERY 1024UL

+#define OPT_FLAT 256UL

+#define OPT_MONO 1UL

+#define OPT_NOBACK 4096UL

+#define OPT_NODL 2UL

+#define OPT_NOHANDS 49152UL

+#define OPT_NOHM 16384UL

+#define OPT_NOPOINTER 16384UL

+#define OPT_NOSECS 32768UL

+#define OPT_NOTICKS 8192UL

+#define OPT_RIGHTX 2048UL

+#define OPT_SIGNED 256UL

+#define PALETTED 8UL

+#define FTPOINTS 2UL

+#define RECTS 9UL

+

+#define RAM_CMD 1081344UL

+#define RAM_DL 1048576UL

+#define RAM_G 0UL

+#define RAM_PAL 1056768UL

+#define RAM_REG 1057792UL

+

+

+

+#define REG_ANALOG 1058104UL

+#define REG_ANA_COMP 1058160UL

+#define REG_CLOCK 1057800UL

+#define REG_CMD_DL 1058028UL

+#define REG_CMD_READ 1058020UL

+#define REG_CMD_WRITE 1058024UL

+#define REG_CPURESET 1057820UL

+#define REG_CRC 1058152UL

+#define REG_CSPREAD 1057892UL

+#define REG_CYA0 1058000UL

+#define REG_CYA1 1058004UL

+#define REG_CYA_TOUCH 1058100UL

+#define REG_DATESTAMP 1058108UL

+#define REG_DITHER 1057884UL

+#define REG_DLSWAP 1057872UL

+#define REG_FRAMES 1057796UL

+#define REG_FREQUENCY 1057804UL

+#define REG_GPIO 1057936UL

+#define REG_GPIO_DIR 1057932UL

+#define REG_HCYCLE 1057832UL

+#define REG_HOFFSET 1057836UL

+#define REG_HSIZE 1057840UL

+#define REG_HSYNC0 1057844UL

+#define REG_HSYNC1 1057848UL

+#define REG_ID 1057792UL

+#define REG_INT_EN 1057948UL

+#define REG_INT_FLAGS 1057944UL

+#define REG_INT_MASK 1057952UL

+#define REG_MACRO_0 1057992UL

+#define REG_MACRO_1 1057996UL

+#define REG_OUTBITS 1057880UL

+#define REG_PCLK 1057900UL

+#define REG_PCLK_POL 1057896UL

+#define REG_PLAY 1057928UL

+#define REG_PLAYBACK_FORMAT 1057972UL

+#define REG_PLAYBACK_FREQ 1057968UL

+#define REG_PLAYBACK_LENGTH 1057960UL

+#define REG_PLAYBACK_LOOP 1057976UL

+#define REG_PLAYBACK_PLAY 1057980UL

+#define REG_PLAYBACK_READPTR 1057964UL

+#define REG_PLAYBACK_START 1057956UL

+#define REG_PWM_DUTY 1057988UL

+#define REG_PWM_HZ 1057984UL

+#define REG_RENDERMODE 1057808UL

+#define REG_ROMSUB_SEL 1058016UL

+#define REG_ROTATE 1057876UL

+#define REG_SNAPSHOT 1057816UL

+#define REG_SNAPY 1057812UL

+#define REG_SOUND 1057924UL

+#define REG_SWIZZLE 1057888UL

+#define REG_TAG 1057912UL

+#define REG_TAG_X 1057904UL

+#define REG_TAG_Y 1057908UL

+#define REG_TAP_CRC 1057824UL

+#define REG_TAP_MASK 1057828UL

+#define REG_TOUCH_ADC_MODE 1058036UL

+#define REG_TOUCH_CHARGE 1058040UL

+#define REG_TOUCH_DIRECT_XY 1058164UL

+#define REG_TOUCH_DIRECT_Z1Z2 1058168UL

+#define REG_TOUCH_MODE 1058032UL

+#define REG_TOUCH_OVERSAMPLE 1058048UL

+#define REG_TOUCH_RAW_XY 1058056UL

+#define REG_TOUCH_RZ 1058060UL

+#define REG_TOUCH_RZTHRESH 1058052UL

+#define REG_TOUCH_SCREEN_XY 1058064UL

+#define REG_TOUCH_SETTLE 1058044UL

+#define REG_TOUCH_TAG 1058072UL

+#define REG_TOUCH_TAG_XY 1058068UL

+#define REG_TOUCH_TRANSFORM_A 1058076UL

+#define REG_TOUCH_TRANSFORM_B 1058080UL

+#define REG_TOUCH_TRANSFORM_C 1058084UL

+#define REG_TOUCH_TRANSFORM_D 1058088UL

+#define REG_TOUCH_TRANSFORM_E 1058092UL

+#define REG_TOUCH_TRANSFORM_F 1058096UL

+#define REG_TRACKER 1085440UL

+#define REG_TRIM 1058156UL

+#define REG_VCYCLE 1057852UL

+#define REG_VOFFSET 1057856UL

+#define REG_VOL_PB 1057916UL

+#define REG_VOL_SOUND 1057920UL

+#define REG_VSIZE 1057860UL

+#define REG_VSYNC0 1057864UL

+#define REG_VSYNC1 1057868UL

+

+

+#define REPEAT 1UL

+#define REPLACE 2UL

+#define RGB332 4UL

+#define RGB565 7UL

+#define SRC_ALPHA 2UL

+#define TEXT8X8 9UL

+#define TEXTVGA 10UL

+#define TOUCHMODE_CONTINUOUS 3UL

+#define TOUCHMODE_FRAME 2UL

+#define TOUCHMODE_OFF 0UL

+#define TOUCHMODE_ONESHOT 1UL

+#define ULAW_SAMPLES 1UL

+#define ZERO 0UL

+

+

+#define VERTEX2F(x,y) ((1UL<<30)|(((x)&32767UL)<<15)|(((y)&32767UL)<<0))

+#define VERTEX2II(x,y,handle,cell) ((2UL<<30)|(((x)&511UL)<<21)|(((y)&511UL)<<12)|(((handle)&31UL)<<7)|(((cell)&127UL)<<0))

+#define BITMAP_SOURCE(addr) ((1UL<<24)|(((addr)&1048575UL)<<0))

+#define CLEAR_COLOR_RGB(red,green,blue) ((2UL<<24)|(((red)&255UL)<<16)|(((green)&255UL)<<8)|(((blue)&255UL)<<0))

+#define TAG(s) ((3UL<<24)|(((s)&255UL)<<0))

+#define COLOR_RGB(red,green,blue) ((4UL<<24)|(((red)&255UL)<<16)|(((green)&255UL)<<8)|(((blue)&255UL)<<0))

+#define BITMAP_HANDLE(handle) ((5UL<<24)|(((handle)&31UL)<<0))

+#define CELL(cell) ((6UL<<24)|(((cell)&127UL)<<0))

+#define BITMAP_LAYOUT(format,linestride,height) ((7UL<<24)|(((format)&31UL)<<19)|(((linestride)&1023UL)<<9)|(((height)&511UL)<<0))

+#define BITMAP_SIZE(filter,wrapx,wrapy,width,height) ((8UL<<24)|(((filter)&1UL)<<20)|(((wrapx)&1UL)<<19)|(((wrapy)&1UL)<<18)|(((width)&511UL)<<9)|(((height)&511UL)<<0))

+#define ALPHA_FUNC(func,ref) ((9UL<<24)|(((func)&7UL)<<8)|(((ref)&255UL)<<0))

+#define STENCIL_FUNC(func,ref,mask) ((10UL<<24)|(((func)&7UL)<<16)|(((ref)&255UL)<<8)|(((mask)&255UL)<<0))

+#define BLEND_FUNC(src,dst) ((11UL<<24)|(((src)&7UL)<<3)|(((dst)&7UL)<<0))

+#define STENCIL_OP(sfail,spass) ((12UL<<24)|(((sfail)&7UL)<<3)|(((spass)&7UL)<<0))

+#define POINT_SIZE(size) ((13UL<<24)|(((size)&8191UL)<<0))

+#define LINE_WIDTH(width) ((14UL<<24)|(((width)&4095UL)<<0))

+#define CLEAR_COLOR_A(alpha) ((15UL<<24)|(((alpha)&255UL)<<0))

+#define COLOR_A(alpha) ((16UL<<24)|(((alpha)&255UL)<<0))

+#define CLEAR_STENCIL(s) ((17UL<<24)|(((s)&255UL)<<0))

+#define CLEAR_TAG(s) ((18UL<<24)|(((s)&255UL)<<0))

+#define STENCIL_MASK(mask) ((19UL<<24)|(((mask)&255UL)<<0))

+#define TAG_MASK(mask) ((20UL<<24)|(((mask)&1UL)<<0))

+#define BITMAP_TRANSFORM_A(a) ((21UL<<24)|(((a)&131071UL)<<0))

+#define BITMAP_TRANSFORM_B(b) ((22UL<<24)|(((b)&131071UL)<<0))

+#define BITMAP_TRANSFORM_C(c) ((23UL<<24)|(((c)&16777215UL)<<0))

+#define BITMAP_TRANSFORM_D(d) ((24UL<<24)|(((d)&131071UL)<<0))

+#define BITMAP_TRANSFORM_E(e) ((25UL<<24)|(((e)&131071UL)<<0))

+#define BITMAP_TRANSFORM_F(f) ((26UL<<24)|(((f)&16777215UL)<<0))

+#define SCISSOR_XY(x,y) ((27UL<<24)|(((x)&511UL)<<9)|(((y)&511UL)<<0))

+#define SCISSOR_SIZE(width,height) ((28UL<<24)|(((width)&1023UL)<<10)|(((height)&1023UL)<<0))

+#define CALL(dest) ((29UL<<24)|(((dest)&65535UL)<<0))

+#define JUMP(dest) ((30UL<<24)|(((dest)&65535UL)<<0))

+#define BEGIN(prim) ((31UL<<24)|(((prim)&15UL)<<0))

+#define COLOR_MASK(r,g,b,a) ((32UL<<24)|(((r)&1UL)<<3)|(((g)&1UL)<<2)|(((b)&1UL)<<1)|(((a)&1UL)<<0))

+#define CLEAR(c,s,t) ((38UL<<24)|(((c)&1UL)<<2)|(((s)&1UL)<<1)|(((t)&1UL)<<0))

+#define END() ((33UL<<24))

+#define SAVE_CONTEXT() ((34UL<<24))

+#define RESTORE_CONTEXT() ((35UL<<24))

+#define RETURN() ((36UL<<24))

+#define MACRO(m) ((37UL<<24)|(((m)&1UL)<<0))

+#define DISPLAY() ((0UL<<24))

+

+#define FT_GPU_NUMCHAR_PERFONT (128)

+#define FT_GPU_FONT_TABLE_SIZE (148)

+

+

+

+/* FT800 font table structure */

+/* Font table address in ROM can be found by reading the address from 0xFFFFC location. */

+/* 16 font tables are present at the address read from location 0xFFFFC */

+typedef struct FT_Gpu_Fonts

+{

+ /* All the values are in bytes */

+ /* Width of each character font from 0 to 127 */

+ ft_uint8_t FontWidth[FT_GPU_NUMCHAR_PERFONT];

+ /* Bitmap format of font wrt bitmap formats supported by FT800 - L1, L4, L8 */

+ ft_uint32_t FontBitmapFormat;

+ /* Font line stride in FT800 ROM */

+ ft_uint32_t FontLineStride;

+ /* Font width in pixels */

+ ft_uint32_t FontWidthInPixels;

+ /* Font height in pixels */

+ ft_uint32_t FontHeightInPixels;

+ /* Pointer to font graphics raw data */

+ ft_uint32_t PointerToFontGraphicsData;

+}FT_Gpu_Fonts_t;

+

+#endif /* #ifndef _FT_GPU_H_ */

+

+

+/* Nothing beyond this */

+

+

+

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/FT_Gpu_Hal.cpp Fri Jan 03 15:26:10 2014 +0000

@@ -0,0 +1,537 @@

+#include "FT_Platform.h"

+#include "mbed.h"

+#include "FT_LCD_Type.h"

+

+

+FT800::FT800(PinName mosi,

+ PinName miso,

+ PinName sck,

+ PinName ss,

+ PinName intr,

+ PinName pd)

+ :_spi(mosi, miso, sck),

+ _ss(ss),

+ _f800_isr(InterruptIn(intr)),

+ _pd(pd)

+ {

+ _spi.format(8,0); // 8 bit spi mode 0

+ _spi.frequency(10000000); // start with 10 Mhz SPI clock

+ _ss = 1; // cs high

+ _pd = 1; // PD high

+ Bootup();

+ }

+

+

+ft_bool_t FT800::Bootup(void){

+ Ft_Gpu_Hal_Open();

+ BootupConfig();

+

+ return(1);

+ }

+

+

+ft_void_t FT800::BootupConfig(void){

+ ft_uint8_t chipid;

+ /* Do a power cycle for safer side */

+ Ft_Gpu_Hal_Powercycle( FT_TRUE);

+

+ /* Access address 0 to wake up the FT800 */

+ Ft_Gpu_HostCommand( FT_GPU_ACTIVE_M);

+ Ft_Gpu_Hal_Sleep(20);

+

+ /* Set the clk to external clock */

+ Ft_Gpu_HostCommand( FT_GPU_EXTERNAL_OSC);

+ Ft_Gpu_Hal_Sleep(10);

+

+

+ /* Switch PLL output to 48MHz */

+ Ft_Gpu_HostCommand( FT_GPU_PLL_48M);

+ Ft_Gpu_Hal_Sleep(10);

+

+ /* Do a core reset for safer side */

+ Ft_Gpu_HostCommand( FT_GPU_CORE_RESET);

+

+ //Read Register ID to check if FT800 is ready.

+ chipid = Ft_Gpu_Hal_Rd8( REG_ID);

+ while(chipid != 0x7C)

+ chipid = Ft_Gpu_Hal_Rd8( REG_ID);

+

+

+ // Speed up

+ _spi.frequency(30000000); // 30 Mhz SPI clock

+

+ /* Configuration of LCD display */

+ FT_DispHCycle = my_DispHCycle;

+ Ft_Gpu_Hal_Wr16( REG_HCYCLE, FT_DispHCycle);

+ FT_DispHOffset = my_DispHOffset;

+ Ft_Gpu_Hal_Wr16( REG_HOFFSET, FT_DispHOffset);

+ FT_DispWidth = my_DispWidth;

+ Ft_Gpu_Hal_Wr16( REG_HSIZE, FT_DispWidth);

+ FT_DispHSync0 = my_DispHSync0;

+ Ft_Gpu_Hal_Wr16( REG_HSYNC0, FT_DispHSync0);

+ FT_DispHSync1 = my_DispHSync1;

+ Ft_Gpu_Hal_Wr16( REG_HSYNC1, FT_DispHSync1);

+ FT_DispVCycle = my_DispVCycle;

+ Ft_Gpu_Hal_Wr16( REG_VCYCLE, FT_DispVCycle);

+ FT_DispVOffset = my_DispVOffset;

+ Ft_Gpu_Hal_Wr16( REG_VOFFSET, FT_DispVOffset);

+ FT_DispHeight = my_DispHeight;

+ Ft_Gpu_Hal_Wr16( REG_VSIZE, FT_DispHeight);

+ FT_DispVSync0 = my_DispVSync0;

+ Ft_Gpu_Hal_Wr16( REG_VSYNC0, FT_DispVSync0);

+ FT_DispVSync1 = my_DispVSync1;

+ Ft_Gpu_Hal_Wr16( REG_VSYNC1, FT_DispVSync1);

+ FT_DispSwizzle = my_DispSwizzle;

+ //Ft_Gpu_Hal_Wr8( REG_SWIZZLE, FT_DispSwizzle);

+ FT_DispPCLKPol = my_DispPCLKPol;

+ //Ft_Gpu_Hal_Wr8( REG_PCLK_POL, FT_DispPCLKPol);

+ FT_DispPCLK = my_DispPCLK;

+ //Ft_Gpu_Hal_Wr8( REG_PCLK,FT_DispPCLK);//after this display is visible on the LCD

+

+ Ft_Gpu_Hal_Wr16( REG_PWM_HZ, 1000);

+

+#ifdef Inv_Backlite

+ Ft_Gpu_Hal_Wr16( REG_PWM_DUTY, 0);

+#else

+ Ft_Gpu_Hal_Wr16( REG_PWM_DUTY, 100);

+#endif

+

+ Ft_Gpu_Hal_Wr8( REG_GPIO_DIR,0x80); //| Ft_Gpu_Hal_Rd8( REG_GPIO_DIR));

+ Ft_Gpu_Hal_Wr8( REG_GPIO,0x080); //| Ft_Gpu_Hal_Rd8( REG_GPIO));

+

+ Ft_Gpu_Hal_Wr32( RAM_DL, CLEAR(1,1,1));

+ Ft_Gpu_Hal_Wr32( RAM_DL+4, DISPLAY());

+ Ft_Gpu_Hal_Wr32( REG_DLSWAP,1);

+

+ Ft_Gpu_Hal_Wr16( REG_PCLK, FT_DispPCLK);

+

+ /* Touch configuration - configure the resistance value to 1200 - this value is specific to customer requirement and derived by experiment */

+ Ft_Gpu_Hal_Wr16( REG_TOUCH_RZTHRESH,1200);

+

+}

+

+

+

+/* API to initialize the SPI interface */

+ft_bool_t FT800::Ft_Gpu_Hal_Init()

+{

+ // is done in constructor

+ return 1;

+}

+

+

+ft_bool_t FT800::Ft_Gpu_Hal_Open()

+{

+ ft_cmd_fifo_wp = ft_dl_buff_wp = 0;

+ status = FT_GPU_HAL_OPENED;

+ return 1;

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_Close( )

+{

+ status = FT_GPU_HAL_CLOSED;

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_DeInit()

+{

+

+}

+

+/*The APIs for reading/writing transfer continuously only with small buffer system*/

+ft_void_t FT800::Ft_Gpu_Hal_StartTransfer( FT_GPU_TRANSFERDIR_T rw,ft_uint32_t addr)

+{

+ if (FT_GPU_READ == rw){

+ _ss = 0; // cs low

+ _spi.write(addr >> 16);

+ _spi.write(addr >> 8);

+ _spi.write(addr & 0xff);

+ _spi.write(0); //Dummy Read Byte

+ status = FT_GPU_HAL_READING;

+ }else{

+ _ss = 0; // cs low

+ _spi.write(0x80 | (addr >> 16));

+ _spi.write(addr >> 8);

+ _spi.write(addr & 0xff);

+ status = FT_GPU_HAL_WRITING;

+ }

+}

+

+

+/*The APIs for writing transfer continuously only*/

+ft_void_t FT800::Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_TRANSFERDIR_T rw, ft_uint16_t count)

+{

+ Ft_Gpu_Hal_StartTransfer( rw, ft_cmd_fifo_wp + RAM_CMD);

+}

+

+ft_uint8_t FT800::Ft_Gpu_Hal_TransferString( const ft_char8_t *string)

+{

+ ft_uint16_t length = strlen(string);

+ while(length --){

+ Ft_Gpu_Hal_Transfer8( *string);

+ string ++;

+ }

+ //Append one null as ending flag

+ Ft_Gpu_Hal_Transfer8( 0);

+}

+

+

+ft_uint8_t FT800::Ft_Gpu_Hal_Transfer8( ft_uint8_t value)

+{

+ return _spi.write(value);

+}

+

+

+ft_uint16_t FT800::Ft_Gpu_Hal_Transfer16( ft_uint16_t value)

+{

+ ft_uint16_t retVal = 0;

+

+ if (status == FT_GPU_HAL_WRITING){

+ Ft_Gpu_Hal_Transfer8( value & 0xFF);//LSB first

+ Ft_Gpu_Hal_Transfer8( (value >> 8) & 0xFF);

+ }else{

+ retVal = Ft_Gpu_Hal_Transfer8( 0);

+ retVal |= (ft_uint16_t)Ft_Gpu_Hal_Transfer8( 0) << 8;

+ }

+

+ return retVal;

+}

+

+ft_uint32_t FT800::Ft_Gpu_Hal_Transfer32( ft_uint32_t value)

+{

+ ft_uint32_t retVal = 0;

+ if (status == FT_GPU_HAL_WRITING){

+ Ft_Gpu_Hal_Transfer16( value & 0xFFFF);//LSB first

+ Ft_Gpu_Hal_Transfer16( (value >> 16) & 0xFFFF);

+ }else{

+ retVal = Ft_Gpu_Hal_Transfer16( 0);

+ retVal |= (ft_uint32_t)Ft_Gpu_Hal_Transfer16( 0) << 16;

+ }

+ return retVal;

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_EndTransfer( )

+{

+ _ss = 1;

+ status = FT_GPU_HAL_OPENED;

+}

+

+

+ft_uint8_t FT800::Ft_Gpu_Hal_Rd8( ft_uint32_t addr)

+{

+ ft_uint8_t value;

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr);

+ value = Ft_Gpu_Hal_Transfer8( 0);

+ Ft_Gpu_Hal_EndTransfer( );

+ return value;

+}

+ft_uint16_t FT800::Ft_Gpu_Hal_Rd16( ft_uint32_t addr)

+{

+ ft_uint16_t value;

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr);

+ value = Ft_Gpu_Hal_Transfer16( 0);

+ Ft_Gpu_Hal_EndTransfer( );

+ return value;

+}

+ft_uint32_t FT800::Ft_Gpu_Hal_Rd32( ft_uint32_t addr)

+{

+ ft_uint32_t value;

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr);

+ value = Ft_Gpu_Hal_Transfer32( 0);

+ Ft_Gpu_Hal_EndTransfer( );

+ return value;

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_Wr8( ft_uint32_t addr, ft_uint8_t v)

+{

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr);

+ Ft_Gpu_Hal_Transfer8( v);

+ Ft_Gpu_Hal_EndTransfer( );

+}

+ft_void_t FT800::Ft_Gpu_Hal_Wr16( ft_uint32_t addr, ft_uint16_t v)

+{

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr);

+ Ft_Gpu_Hal_Transfer16( v);

+ Ft_Gpu_Hal_EndTransfer( );

+}

+ft_void_t FT800::Ft_Gpu_Hal_Wr32( ft_uint32_t addr, ft_uint32_t v)

+{

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr);

+ Ft_Gpu_Hal_Transfer32( v);

+ Ft_Gpu_Hal_EndTransfer( );

+}

+

+ft_void_t FT800::Ft_Gpu_HostCommand( ft_uint8_t cmd)

+{

+ _ss = 0;

+ _spi.write(cmd);

+ _spi.write(0);

+ _spi.write(0);

+ _ss = 1;

+}

+

+ft_void_t FT800::Ft_Gpu_ClockSelect( FT_GPU_PLL_SOURCE_T pllsource)

+{

+ Ft_Gpu_HostCommand( pllsource);

+}

+

+ft_void_t FT800::Ft_Gpu_PLL_FreqSelect( FT_GPU_PLL_FREQ_T freq)

+{

+ Ft_Gpu_HostCommand( freq);

+}

+

+ft_void_t FT800::Ft_Gpu_PowerModeSwitch( FT_GPU_POWER_MODE_T pwrmode)

+{

+ Ft_Gpu_HostCommand( pwrmode);

+}

+

+ft_void_t FT800::Ft_Gpu_CoreReset( )

+{

+ Ft_Gpu_HostCommand( 0x68);

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_Updatecmdfifo( ft_uint16_t count)

+{

+ ft_cmd_fifo_wp = ( ft_cmd_fifo_wp + count) & 4095;

+ //4 byte alignment

+ ft_cmd_fifo_wp = ( ft_cmd_fifo_wp + 3) & 0xffc;

+ Ft_Gpu_Hal_Wr16( REG_CMD_WRITE, ft_cmd_fifo_wp);

+}

+

+

+ft_uint16_t FT800::Ft_Gpu_Cmdfifo_Freespace( )

+{

+ ft_uint16_t fullness,retval;

+

+ fullness = ( ft_cmd_fifo_wp - Ft_Gpu_Hal_Rd16( REG_CMD_READ)) & 4095;

+ retval = (FT_CMD_FIFO_SIZE - 4) - fullness;

+ return (retval);

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_WrCmdBuf( ft_uint8_t *buffer,ft_uint16_t count)

+{

+ ft_uint32_t length =0, SizeTransfered = 0;

+

+#define MAX_CMD_FIFO_TRANSFER Ft_Gpu_Cmdfifo_Freespace( )

+ do {

+ length = count;

+ if (length > MAX_CMD_FIFO_TRANSFER){

+ length = MAX_CMD_FIFO_TRANSFER;

+ }

+ Ft_Gpu_Hal_CheckCmdBuffer( length);

+

+ Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_WRITE,length);

+

+ SizeTransfered = 0;

+ while (length--) {

+ Ft_Gpu_Hal_Transfer8( *buffer);

+ buffer++;

+ SizeTransfered ++;

+ }

+ length = SizeTransfered;

+

+ Ft_Gpu_Hal_EndTransfer( );

+ Ft_Gpu_Hal_Updatecmdfifo( length);

+

+ Ft_Gpu_Hal_WaitCmdfifo_empty( );

+

+ count -= length;

+ }while (count > 0);

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_WrCmdBufFromFlash( FT_PROGMEM ft_prog_uchar8_t *buffer,ft_uint16_t count)

+{

+ ft_uint32_t length =0, SizeTransfered = 0;

+

+#define MAX_CMD_FIFO_TRANSFER Ft_Gpu_Cmdfifo_Freespace( )

+ do {

+ length = count;

+ if (length > MAX_CMD_FIFO_TRANSFER){

+ length = MAX_CMD_FIFO_TRANSFER;

+ }

+ Ft_Gpu_Hal_CheckCmdBuffer( length);

+

+ Ft_Gpu_Hal_StartCmdTransfer( FT_GPU_WRITE,length);

+

+

+ SizeTransfered = 0;

+ while (length--) {

+ Ft_Gpu_Hal_Transfer8( ft_pgm_read_byte_near(buffer));

+ buffer++;

+ SizeTransfered ++;

+ }

+ length = SizeTransfered;

+

+ Ft_Gpu_Hal_EndTransfer( );

+ Ft_Gpu_Hal_Updatecmdfifo( length);

+

+ Ft_Gpu_Hal_WaitCmdfifo_empty( );

+

+ count -= length;

+ }while (count > 0);

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_CheckCmdBuffer( ft_uint16_t count)

+{

+ ft_uint16_t getfreespace;

+ do{

+ getfreespace = Ft_Gpu_Cmdfifo_Freespace( );

+ }while(getfreespace < count);

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_WaitCmdfifo_empty( )

+{

+ while(Ft_Gpu_Hal_Rd16( REG_CMD_READ) != Ft_Gpu_Hal_Rd16( REG_CMD_WRITE));

+

+ ft_cmd_fifo_wp = Ft_Gpu_Hal_Rd16( REG_CMD_WRITE);

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_WaitLogo_Finish( )

+{

+ ft_int16_t cmdrdptr,cmdwrptr;

+

+ do{

+ cmdrdptr = Ft_Gpu_Hal_Rd16( REG_CMD_READ);

+ cmdwrptr = Ft_Gpu_Hal_Rd16( REG_CMD_WRITE);

+ }while ((cmdwrptr != cmdrdptr) || (cmdrdptr != 0));

+ ft_cmd_fifo_wp = 0;

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_ResetCmdFifo( )

+{

+ ft_cmd_fifo_wp = 0;

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_WrCmd32( ft_uint32_t cmd)

+{

+ Ft_Gpu_Hal_CheckCmdBuffer( sizeof(cmd));

+

+ Ft_Gpu_Hal_Wr32( RAM_CMD + ft_cmd_fifo_wp,cmd);

+

+ Ft_Gpu_Hal_Updatecmdfifo( sizeof(cmd));

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_ResetDLBuffer( )

+{

+ ft_dl_buff_wp = 0;

+}

+

+/* Toggle PD_N pin of FT800 board for a power cycle*/

+ft_void_t FT800::Ft_Gpu_Hal_Powercycle( ft_bool_t up)

+{

+ if (up)

+ {

+ //Toggle PD_N from low to high for power up switch

+ _pd = 0;

+ Ft_Gpu_Hal_Sleep(20);

+

+ _pd = 1;

+ Ft_Gpu_Hal_Sleep(20);

+ }else

+ {

+ //Toggle PD_N from high to low for power down switch

+ _pd = 1;

+ Ft_Gpu_Hal_Sleep(20);

+

+ _pd = 0;

+ Ft_Gpu_Hal_Sleep(20);

+ }

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_WrMemFromFlash( ft_uint32_t addr,const ft_prog_uchar8_t *buffer, ft_uint32_t length)

+{

+ ft_uint32_t SizeTransfered = 0;

+

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr);

+

+ while (length--) {

+ Ft_Gpu_Hal_Transfer8( ft_pgm_read_byte_near(buffer));

+ buffer++;

+ }

+

+ Ft_Gpu_Hal_EndTransfer( );

+}

+

+ft_void_t FT800::Ft_Gpu_Hal_WrMem( ft_uint32_t addr,const ft_uint8_t *buffer, ft_uint32_t length)

+{

+ ft_uint32_t SizeTransfered = 0;

+

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_WRITE,addr);

+

+ while (length--) {

+ Ft_Gpu_Hal_Transfer8( *buffer);

+ buffer++;

+ }

+

+ Ft_Gpu_Hal_EndTransfer( );

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_RdMem( ft_uint32_t addr, ft_uint8_t *buffer, ft_uint32_t length)

+{

+ ft_uint32_t SizeTransfered = 0;

+

+ Ft_Gpu_Hal_StartTransfer( FT_GPU_READ,addr);

+

+ while (length--) {

+ *buffer = Ft_Gpu_Hal_Transfer8( 0);

+ buffer++;

+ }

+

+ Ft_Gpu_Hal_EndTransfer( );

+}

+

+ft_int32_t FT800::Ft_Gpu_Hal_Dec2Ascii(ft_char8_t *pSrc,ft_int32_t value)

+{

+ ft_int16_t Length;

+ ft_char8_t *pdst,charval;

+ ft_int32_t CurrVal = value,tmpval,i;

+ ft_char8_t tmparray[16],idx = 0;

+

+ Length = strlen(pSrc);

+ pdst = pSrc + Length;

+

+ if(0 == value)

+ {

+ *pdst++ = '0';

+ *pdst++ = '\0';

+ return 0;

+ }

+

+ if(CurrVal < 0)

+ {

+ *pdst++ = '-';

+ CurrVal = - CurrVal;

+ }

+ /* insert the value */

+ while(CurrVal > 0){

+ tmpval = CurrVal;

+ CurrVal /= 10;

+ tmpval = tmpval - CurrVal*10;

+ charval = '0' + tmpval;

+ tmparray[idx++] = charval;

+ }

+

+ for(i=0;i<idx;i++)

+ {

+ *pdst++ = tmparray[idx - i - 1];

+ }

+ *pdst++ = '\0';

+

+ return 0;

+}

+

+

+ft_void_t FT800::Ft_Gpu_Hal_Sleep(ft_uint16_t ms)

+{

+ wait_ms(ms);

+}

+

+

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/FT_Gpu_Hal.h Fri Jan 03 15:26:10 2014 +0000

@@ -0,0 +1,261 @@

+/*!

+ * \file FT_GPU_HAL.h

+ *

+ * \author FTDI

+ * \date 2013.04.24

+ *

+ * Copyright 2013 Future Technology Devices International Limited

+ *

+ * Project: FT800 or EVE compatible silicon

+ * File Description:

+ * This file defines the generic APIs of host access layer for the FT800 or EVE compatible silicon.

+ * Application shall access FT800 or EVE resources over these APIs,regardless of I2C or SPI protocol.

+ * I2C and SPI is selected by compiler switch "FT_I2C_MODE" and "FT_SPI_MODE". In addition, there are

+ * some helper functions defined for FT800 coprocessor engine as well as host commands.

+ * Rivision History:

+ */

+#ifndef FT_GPU_HAL_H

+#define FT_GPU_HAL_H

+

+#include "mbed.h"

+#include "FT_DataTypes.h"

+

+typedef enum {

+ FT_GPU_I2C_MODE = 0,

+ FT_GPU_SPI_MODE,

+

+ FT_GPU_MODE_COUNT,

+ FT_GPU_MODE_UNKNOWN = FT_GPU_MODE_COUNT

+} FT_GPU_HAL_MODE_E;

+

+typedef enum {

+ FT_GPU_HAL_OPENED,

+ FT_GPU_HAL_READING,

+ FT_GPU_HAL_WRITING,

+ FT_GPU_HAL_CLOSED,

+

+ FT_GPU_HAL_STATUS_COUNT,

+ FT_GPU_HAL_STATUS_ERROR = FT_GPU_HAL_STATUS_COUNT

+} FT_GPU_HAL_STATUS_E;

+

+typedef struct {

+ ft_uint8_t reserved;

+} Ft_Gpu_App_Context_t;

+

+typedef struct {

+ /* Total number channels for libmpsse */

+ ft_uint32_t TotalChannelNum;

+} Ft_Gpu_HalInit_t;

+

+typedef enum {

+ FT_GPU_READ = 0,

+ FT_GPU_WRITE,

+} FT_GPU_TRANSFERDIR_T;

+

+

+typedef struct {

+ ft_uint32_t length; //IN and OUT

+ ft_uint32_t address;

+ ft_uint8_t *buffer;

+} Ft_Gpu_App_Transfer_t;

+

+class FT800

+{

+public:

+ FT800(PinName mosi,

+ PinName miso,

+ PinName sck,

+ PinName ss,

+ PinName intr,

+ PinName pd);

+

+private:

+ SPI _spi;

+ DigitalOut _ss;

+ DigitalOut _pd;

+ InterruptIn _f800_isr;

+public:

+ /* Global used for buffer optimization */

+ //Ft_Gpu_Hal_Context_t host,*phost;

+ Ft_Gpu_App_Context_t app_header;

+ ft_uint16_t ft_cmd_fifo_wp; //coprocessor fifo write pointer

+ ft_uint16_t ft_dl_buff_wp; //display command memory write pointer

+ FT_GPU_HAL_STATUS_E status; //OUT

+ ft_void_t* hal_handle; //IN/OUT

+ ft_uint32_t Ft_CmdBuffer_Index;

+ ft_uint32_t Ft_DlBuffer_Index;

+ ft_int16_t FT_DispWidth;

+ ft_int16_t FT_DispHeight;

+ ft_int16_t FT_DispHCycle;

+ ft_int16_t FT_DispHOffset;

+ ft_int16_t FT_DispHSync0;

+ ft_int16_t FT_DispHSync1;

+ ft_int16_t FT_DispVCycle;

+ ft_int16_t FT_DispVOffset;

+ ft_int16_t FT_DispVSync0;

+ ft_int16_t FT_DispVSync1;

+ ft_uint8_t FT_DispPCLK;

+ ft_char8_t FT_DispSwizzle;

+ ft_char8_t FT_DispPCLKPol;

+

+

+ ft_void_t BootupConfig(void);

+ ft_bool_t Bootup(void);

+

+

+ /*The basic APIs Level 1*/

+ ft_bool_t Ft_Gpu_Hal_Init( );

+ ft_bool_t Ft_Gpu_Hal_Open( );

+

+ /*The APIs for reading/writing transfer continuously only with small buffer system*/

+ ft_void_t Ft_Gpu_Hal_StartTransfer(FT_GPU_TRANSFERDIR_T rw,ft_uint32_t addr);

+ ft_uint8_t Ft_Gpu_Hal_Transfer8(ft_uint8_t value);

+ ft_uint16_t Ft_Gpu_Hal_Transfer16(ft_uint16_t value);

+ ft_uint32_t Ft_Gpu_Hal_Transfer32(ft_uint32_t value);

+ ft_void_t Ft_Gpu_Hal_EndTransfer( );

+

+ /*Read & Write APIs for both burst and single transfer,depending on buffer size*/

+ ft_void_t Ft_Gpu_Hal_Read(Ft_Gpu_App_Transfer_t *transfer);

+ ft_void_t Ft_Gpu_Hal_Write(Ft_Gpu_App_Transfer_t *transfer);

+

+ ft_void_t Ft_Gpu_Hal_Close();

+ ft_void_t Ft_Gpu_Hal_DeInit();

+

+ /*Helper function APIs Read*/

+ ft_uint8_t Ft_Gpu_Hal_Rd8(ft_uint32_t addr);

+ ft_uint16_t Ft_Gpu_Hal_Rd16(ft_uint32_t addr);

+ ft_uint32_t Ft_Gpu_Hal_Rd32(ft_uint32_t addr);

+

+ /*Helper function APIs Write*/

+ ft_void_t Ft_Gpu_Hal_Wr8(ft_uint32_t addr, ft_uint8_t v);

+ ft_void_t Ft_Gpu_Hal_Wr16(ft_uint32_t addr, ft_uint16_t v);

+ ft_void_t Ft_Gpu_Hal_Wr32(ft_uint32_t addr, ft_uint32_t v);

+

+ /*******************************************************************************/

+ /*******************************************************************************/

+ /*APIs for coprocessor Fifo read/write and space management*/

+ ft_void_t Ft_Gpu_Hal_Updatecmdfifo(ft_uint16_t count);

+ ft_void_t Ft_Gpu_Hal_WrCmd32(ft_uint32_t cmd);

+ ft_void_t Ft_Gpu_Hal_WrCmdBuf(ft_uint8_t *buffer,ft_uint16_t count);

+ ft_void_t Ft_Gpu_Hal_WaitCmdfifo_empty();

+ ft_void_t Ft_Gpu_Hal_ResetCmdFifo();

+ ft_void_t Ft_Gpu_Hal_CheckCmdBuffer(ft_uint16_t count);

+ ft_void_t Ft_Gpu_Hal_ResetDLBuffer();

+

+ ft_void_t Ft_Gpu_Hal_StartCmdTransfer(FT_GPU_TRANSFERDIR_T rw, ft_uint16_t count);

+ ft_void_t Ft_Gpu_Hal_Powercycle(ft_bool_t up);

+

+

+ /*******************************************************************************/

+ /*******************************************************************************/

+ /*APIs for Host Commands*/

+ typedef enum {

+ FT_GPU_INTERNAL_OSC = 0x48, //default

+ FT_GPU_EXTERNAL_OSC = 0x44,

+ } FT_GPU_PLL_SOURCE_T;

+ typedef enum {

+ FT_GPU_PLL_48M = 0x62, //default

+ FT_GPU_PLL_36M = 0x61,

+ FT_GPU_PLL_24M = 0x64,

+ } FT_GPU_PLL_FREQ_T;

+

+ typedef enum {

+ FT_GPU_ACTIVE_M = 0x00,

+ FT_GPU_STANDBY_M = 0x41,//default

+ FT_GPU_SLEEP_M = 0x42,

+ FT_GPU_POWERDOWN_M = 0x50,

+ } FT_GPU_POWER_MODE_T;

+

+#define FT_GPU_CORE_RESET (0x68)

+

+ ft_int32_t hal_strlen(const ft_char8_t *s);

+ ft_void_t Ft_Gpu_Hal_Sleep(ft_uint16_t ms);

+ ft_void_t Ft_Gpu_ClockSelect(FT_GPU_PLL_SOURCE_T pllsource);

+ ft_void_t Ft_Gpu_PLL_FreqSelect(FT_GPU_PLL_FREQ_T freq);

+ ft_void_t Ft_Gpu_PowerModeSwitch(FT_GPU_POWER_MODE_T pwrmode);

+ ft_void_t Ft_Gpu_CoreReset();

+//ft_void_t Ft_Gpu_Hal_StartTransfer( ,FT_GPU_TRANSFERDIR_T rw,ft_uint32_t addr);

+ ft_void_t Ft_Gpu_Hal_WrMem(ft_uint32_t addr, const ft_uint8_t *buffer, ft_uint32_t length);

+ ft_void_t Ft_Gpu_Hal_WrMemFromFlash(ft_uint32_t addr,const ft_prog_uchar8_t *buffer, ft_uint32_t length);

+ ft_void_t Ft_Gpu_Hal_WrCmdBufFromFlash(FT_PROGMEM ft_prog_uchar8_t *buffer,ft_uint16_t count);

+ ft_void_t Ft_Gpu_Hal_RdMem(ft_uint32_t addr, ft_uint8_t *buffer, ft_uint32_t length);

+ ft_void_t Ft_Gpu_Hal_WaitLogo_Finish();

+ ft_uint8_t Ft_Gpu_Hal_TransferString(const ft_char8_t *string);

+ ft_void_t Ft_Gpu_HostCommand(ft_uint8_t cmd);

+ ft_int32_t Ft_Gpu_Hal_Dec2Ascii(ft_char8_t *pSrc,ft_int32_t value);

+

+ ft_void_t Ft_Gpu_CoCmd_Text(ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s);

+ ft_void_t Ft_Gpu_CoCmd_Number(ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, ft_int32_t n);

+ ft_void_t Ft_Gpu_CoCmd_LoadIdentity();

+ ft_void_t Ft_Gpu_CoCmd_Toggle(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t font, ft_uint16_t options, ft_uint16_t state, const ft_char8_t* s);

+ ft_void_t Ft_Gpu_CoCmd_Gauge(ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t major, ft_uint16_t minor, ft_uint16_t val, ft_uint16_t range);

+ ft_void_t Ft_Gpu_CoCmd_RegRead(ft_uint32_t ptr, ft_uint32_t result);

+ ft_void_t Ft_Gpu_CoCmd_GetProps(ft_uint32_t ptr, ft_uint32_t w, ft_uint32_t h);

+ ft_void_t Ft_Gpu_CoCmd_Memcpy(ft_uint32_t dest, ft_uint32_t src, ft_uint32_t num);

+ ft_void_t Ft_Gpu_CoCmd_Spinner(ft_int16_t x, ft_int16_t y, ft_uint16_t style, ft_uint16_t scale);

+ ft_void_t Ft_Gpu_CoCmd_BgColor(ft_uint32_t c);

+ ft_void_t Ft_Gpu_CoCmd_Swap();

+ ft_void_t Ft_Gpu_CoCmd_Inflate(ft_uint32_t ptr);

+ ft_void_t Ft_Gpu_CoCmd_Translate(ft_int32_t tx, ft_int32_t ty);

+ ft_void_t Ft_Gpu_CoCmd_Stop();

+ ft_void_t Ft_Gpu_CoCmd_Slider(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range);

+ ft_void_t Ft_Gpu_CoCmd_Interrupt(ft_uint32_t ms);

+ ft_void_t Ft_Gpu_CoCmd_FgColor(ft_uint32_t c);

+ ft_void_t Ft_Gpu_CoCmd_Rotate(ft_int32_t a);

+ ft_void_t Ft_Gpu_CoCmd_Button(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s);

+ ft_void_t Ft_Gpu_CoCmd_MemWrite(ft_uint32_t ptr, ft_uint32_t num);

+ ft_void_t Ft_Gpu_CoCmd_Scrollbar(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t size, ft_uint16_t range);

+ ft_void_t Ft_Gpu_CoCmd_GetMatrix(ft_int32_t a, ft_int32_t b, ft_int32_t c, ft_int32_t d, ft_int32_t e, ft_int32_t f);

+ ft_void_t Ft_Gpu_CoCmd_Sketch(ft_int16_t x, ft_int16_t y, ft_uint16_t w, ft_uint16_t h, ft_uint32_t ptr, ft_uint16_t format);

+ ft_void_t Ft_Gpu_CoCmd_MemSet(ft_uint32_t ptr, ft_uint32_t value, ft_uint32_t num);

+ ft_void_t Ft_Gpu_CoCmd_Calibrate(ft_uint32_t result);

+ ft_void_t Ft_Gpu_CoCmd_SetFont(ft_uint32_t font, ft_uint32_t ptr);

+ ft_void_t Ft_Gpu_CoCmd_Bitmap_Transform(ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result);

+ ft_void_t Ft_Gpu_CoCmd_GradColor(ft_uint32_t c);

+ ft_void_t Ft_Gpu_CoCmd_Append(ft_uint32_t ptr, ft_uint32_t num);

+ ft_void_t Ft_Gpu_CoCmd_MemZero(ft_uint32_t ptr, ft_uint32_t num);

+ ft_void_t Ft_Gpu_CoCmd_Scale(ft_int32_t sx, ft_int32_t sy);

+ ft_void_t Ft_Gpu_CoCmd_Clock(ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t h, ft_uint16_t m, ft_uint16_t s, ft_uint16_t ms);

+ ft_void_t Ft_Gpu_CoCmd_Gradient(ft_int16_t x0, ft_int16_t y0, ft_uint32_t rgb0, ft_int16_t x1, ft_int16_t y1, ft_uint32_t rgb1);

+ ft_void_t Ft_Gpu_CoCmd_SetMatrix();

+ ft_void_t Ft_Gpu_CoCmd_Track(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t tag);

+ ft_void_t Ft_Gpu_CoCmd_GetPtr(ft_uint32_t result);

+ ft_void_t Ft_Gpu_CoCmd_Progress(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_uint16_t options, ft_uint16_t val, ft_uint16_t range);

+ ft_void_t Ft_Gpu_CoCmd_ColdStart();

+ ft_void_t Ft_Gpu_CoCmd_Keys(ft_int16_t x, ft_int16_t y, ft_int16_t w, ft_int16_t h, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s);

+ ft_void_t Ft_Gpu_CoCmd_Dial(ft_int16_t x, ft_int16_t y, ft_int16_t r, ft_uint16_t options, ft_uint16_t val);

+ ft_void_t Ft_Gpu_CoCmd_LoadImage(ft_uint32_t ptr, ft_uint32_t options);

+ ft_void_t Ft_Gpu_CoCmd_Dlstart();

+ ft_void_t Ft_Gpu_CoCmd_Snapshot(ft_uint32_t ptr);

+ ft_void_t Ft_Gpu_CoCmd_ScreenSaver();

+ ft_void_t Ft_Gpu_CoCmd_Memcrc(ft_uint32_t ptr, ft_uint32_t num, ft_uint32_t result);

+

+ ft_void_t Ft_Gpu_CoCmd_Logo();

+//ft_void_t Ft_Gpu_CoCmd_Calibrate( ft_uint32_t result);

+//ft_void_t Ft_Gpu_CoCmd_Text( ft_int16_t x, ft_int16_t y, ft_int16_t font, ft_uint16_t options, const ft_char8_t* s);

+

+ ft_void_t Ft_Gpu_Copro_SendCmd( ft_uint32_t cmd);

+ ft_void_t Ft_Gpu_CoCmd_SendStr( const ft_char8_t *s);

+ ft_void_t Ft_Gpu_CoCmd_StartFunc( ft_uint16_t count);

+ ft_void_t Ft_Gpu_CoCmd_EndFunc( ft_uint16_t count);

+ ft_void_t Ft_Gpu_CoCmd_TouchTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result);

+ ft_void_t Ft_Gpu_CoCmd_BitmapTransform( ft_int32_t x0, ft_int32_t y0, ft_int32_t x1, ft_int32_t y1, ft_int32_t x2, ft_int32_t y2, ft_int32_t tx0, ft_int32_t ty0, ft_int32_t tx1, ft_int32_t ty1, ft_int32_t tx2, ft_int32_t ty2, ft_uint16_t result);

+ ft_void_t Ft_Gpu_CoCmd_MemCrc( ft_uint32_t ptr, ft_uint32_t num, ft_uint32_t result);

+

+ ft_uint16_t Ft_Gpu_Cmdfifo_Freespace( );

+

+ ft_void_t Ft_App_WrCoCmd_Buffer(ft_uint32_t cmd);

+ ft_void_t Ft_App_WrDlCmd_Buffer(ft_uint32_t cmd);

+ ft_void_t Ft_App_Flush_DL_Buffer();

+ ft_void_t Ft_App_Flush_Co_Buffer();

+ ft_void_t TFT_fadeout();

+ ft_void_t TFT_fadein();

+ ft_void_t GPU_DLSwap(ft_uint8_t DL_Swap_Type);

+

+

+}; // end of class

+

+#endif /*FT_GPU_HAL_H*/

+

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/FT_Hal_Utils.h Fri Jan 03 15:26:10 2014 +0000 @@ -0,0 +1,20 @@ +#ifndef _FT_HAL_UTILS_H_ +#define _FT_HAL_UTILS_H_ + + +#define RGB(r, g, b) ((((vc_int32_t)(r)) << 16) | (((vc_int32_t)(g)) << 8) | (b)) +#define SQ(v) ((v) * (v)) +#define MIN(x,y) ((x) > (y) ? (y) : (x)) +#define MAX(x,y) ((x) > (y) ? (x) : (y)) +#define PLAYCOLOR 0x00A0A080 +#define NOTE(n, sharp) (((n) - 'C') + ((sharp) * 128)) +#define F16(s) ((vc_int32_t)((s) * 65536)) +#define INVALID_TOUCH_XY 0x8000 +#define ABS(x) ((x) > (0) ? (x) : (-x)) + + +#endif /* _FT_HAL_UTILS_H_ */ + + + +

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/FT_LCD_Type.h Fri Jan 03 15:26:10 2014 +0000 @@ -0,0 +1,24 @@ +#ifndef FT_LCD_TYPE_H +#define FT_LCD_TYPE_H + +/* Global variables for display resolution to support various display panels */ +/* Default is WQVGA - 480x272 */ + +#define my_DispWidth 480 +#define my_DispHeight 272 +#define my_DispHCycle 548 +#define my_DispHOffset 43 +#define my_DispHSync0 0 +#define my_DispHSync1 41 +#define my_DispVCycle 292 +#define my_DispVOffset 12 +#define my_DispVSync0 0 +#define my_DispVSync1 10 +#define my_DispPCLK 5 +#define my_DispSwizzle 0 +#define my_DispPCLKPol 1 + +/* the GLYN display has inverted backlite */ +#define Inv_Backlite + +#endif

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/FT_Platform.h Fri Jan 03 15:26:10 2014 +0000 @@ -0,0 +1,18 @@ +#ifndef _FT_PLATFORM_H_ +#define _FT_PLATFORM_H_ + +#include "FT_DataTypes.h" +#include "FT_Gpu_Hal.h" +#include "FT_Gpu.h" +//#include "FT_CoPro_Cmds.h" +//#include "FT_LCD_Type.h" + + +#endif /*_FT_PLATFORM_H_*/ +/* Nothing beyond this*/ + + + + + +

EVE FT800

EVE FT800

ADAM

ADAM