Home Page : http://www.mcugear.com/en/ MCU Gear manual mode (circuit quick changer!) You can save 8 schematic(bank 0-7) manually and change it quickly.

Fork of MCUGear by

This is a MCU Gear manual mode library.

(日本語は英語の次に書いてあります。)

MCU Gear is a digital wiring extension board.(A kind of dynamic circuit changer.)

It can change its wiring dynamically, without the need of rewiring your device.

Your MCU can be connected to a theoretical maximum of 120 devices.

detail : http://mcugear.com/en/

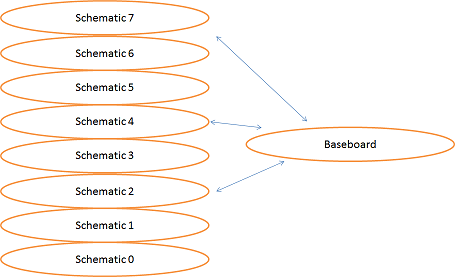

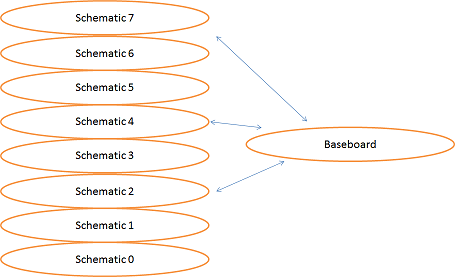

You can save 8 schematics (bank 0-7) on Baseboard.

How to use it?

1,include library

1,include library

#include "mbed.h" #include "MCUGearBaseM.h" #include "MCUGearM.h" #include "commonM.h"

2,Declare Module

(! You do not pile up each module if you want to open module gate simultaneously.)

2,Declare Module

MCUGear myModule1(p28, p27, N_***_***_***); MCUGear myModule2(p28, p27, N_***_***_***);

myModule: Optional name for Module.

p28, p27, : I2C pins (KL25Z is "PTE0, PTE1")

N_*_*_* : Address. You can set it on the reverse side of the Module board.

3,Initialize baseboard

3,Initialize baseboard

initBase();

4,Make wiring data

4,Call wiring register

startReg(bank);

myModule1.setWire(IO_MBED_P9, IO_REG_IN_DIR, 5);

myModule1.setWire(IO_MBED_P15, IO_REG_OUT_DIR, 2);

myModule1.setWire(IO_MBED_P12, IO_REG_OUT_DIR, 0);

myModule2.setWire(IO_MBED_P13, IO_REG_OUT_DIR, 1);

myModule2.setWire(IO_MBED_P14, IO_REG_IN_DIR, 3);

myModule2.setWire(IO_MBED_P16, IO_REG_IN_DIR, 4);

endReg(bank);

see the reference on MCUGearBaseboard.h file.

4,Call wiring register

// CPU I/O

typedef enum {

#if defined TARGET_LPC1768

IO_MBED_P15 = 0x80,

IO_MBED_P13,

IO_MBED_P16,

IO_MBED_P12,

IO_MBED_P5,

IO_MBED_P11,

IO_MBED_P23,

IO_MBED_P22,

IO_MBED_P26,

IO_MBED_P10,

IO_MBED_P21,

IO_MBED_P9,

IO_MBED_P6,

IO_MBED_P7,

IO_MBED_P8,

IO_MBED_P14,

IO_MBED_P24,

IO_MBED_P25,

IO_MBED_P28,

IO_MBED_P27

#endif

#if defined TARGET_KL25Z

IO_MBED_PTA5 = 0x80,

IO_MBED_PTC8,

IO_MBED_PTC9,

IO_MBED_PTD5,

IO_MBED_PTA13,

IO_MBED_PTD2,

IO_MBED_PTB1,

IO_MBED_PTB2,

IO_MBED_PTA2,

IO_MBED_PTD4,

IO_MBED_PTB3,

IO_MBED_PTA12,

IO_MBED_PTD0,

IO_MBED_PTD3,

IO_MBED_PTD1,

IO_MBED_PTA4,

IO_MBED_PTB0,

IO_MBED_PTA1,

IO_MBED_PTE0, //SDA

IO_MBED_PTE1 //SCL

#endif

} en_cpu_io;

-

startReg function

void startReg(uint8_t bank);

uint8_t bank : The "bank" is schematic layer. You can select from 0 to 7 bank.

setWire function

uint8_t setWire(uint8_t mcuIO, uint8_t direction, uint8_t moduleIO);

setWire() is wiring data to connect pin of MCU to pin of Module.

uint8_t mcuIO : You can choose 18 IOs.

uint8_t direction: choose signal direction IO_REG_OUT_DIR : output from MCU IO_REG_IN_DIR : input to MCU

uint8_t moduleIO: You can select module pin.

endReg function

void endReg(uint8_t bank);

uint8_t bank : The "bank" is schematic layer. You can select from 0 to 7 bank. Must be same as "starReg()".

You can make other schematic(bank) as with the code 4,.

5,Change the schematic (bank)

5,Change the schematic (bank)

void changeBank(uint8_t bank);

You can select the schematic form 0 to 7.

6,Open or close the module gate

6,Open or close the module gate

myModule1.connectModule(); myModule2.connectModule(); ... (same as normal mbed code) ... myModule1.disconnectModule(); myModule2.disconnectModule();

Now, you can connect the many modules simultaneously with bank system!

Sample code 1

Universal Module and LCD module test program. This is show you that is possible to connect both modules simultaneously.

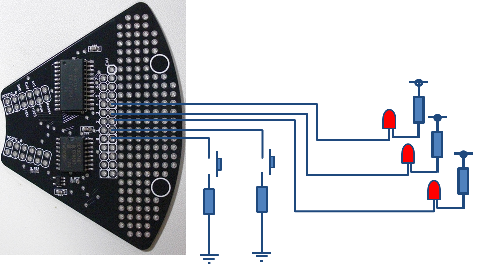

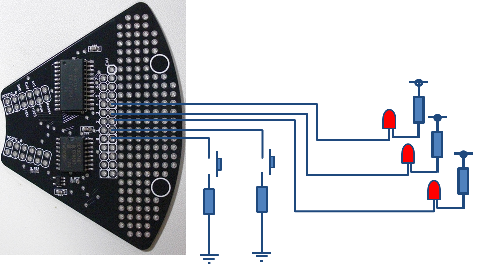

I set test function board like the below picture.(Universal module)

Sample code 1

#include "mbed.h"

#include "TextLCD.h"

#include "MCUGearBaseM.h"

#include "MCUGearM.h"

#include "commonM.h"

Serial pc(USBTX, USBRX);

void setIOUni(MCUGear *mcugear);

void setIOLCD(MCUGear *mcugear);

DigitalOut myled(LED1);

MCUGear UniM(p28, p27, N_VDD_VDD_VDD); //2 Connector Universal Module

MCUGear LCDM(p28, p27, N_VDD_VSS_VSS); //LCD Module

DigitalOut Dout1(p11);

DigitalOut Dout2(p12);

DigitalOut Dout3(p13);

DigitalOut Dout4(p14);

DigitalOut Dout5(p15);

DigitalIn Din1(p9);

DigitalIn Din2(p10);

int main() {

int sw1 = 0;

int sw2 = 0;

int nowBank = 0;

initBase(); //initialize Baseboard

//set schematic select 0-7

UniM.detectModule(); //save location data in MCUGear class.

LCDM.detectModule(); //save location data in MCUGear class.

startReg(0);

setIOUni(&UniM);//make schematic Bank0

setIOLCD(&LCDM);//make schematic Bank0

endReg(0);

changeBank(0);//select Bank

LCDM.connectModule();

TextLCD lcd(p21, p22, p23, p24, p25, p26, TextLCD::LCD16x2); // rs, e, d4-d7

lcd.cls();

lcd.printf("Hello World!\n");

wait(1);

LCDM.disconnectModule();

UniM.connectModule();//open the module gate

LCDM.connectModule();//open the module gate

while(1) {

//UniM.connectModule();

//LCDM.connectModule();

sw1 = Din1.read();

sw2 = Din2.read();

printf("sw1 = %d sw2 = %d\r\n",sw1,sw2);

lcd.printf(" "); //set IO as a neutral position

lcd.cls(); //clear LCD

lcd.printf("sw1 = %d\nsw2 = %d",sw1,sw2); //write LCD data

wait_ms(10); //delay for view the LCD

Dout1 = 0;

Dout2 = 1;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 0;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 1;

Dout3 = 0;

wait(0.3);

//UniM.disconnectModule();//close the module gate

//LCDM.disconnectModule();//close the module gate

}

}

void setIOUni(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P11, IO_REG_OUT_DIR,2);

mcugear->setWire(IO_MBED_P12, IO_REG_OUT_DIR,3);

mcugear->setWire(IO_MBED_P13, IO_REG_OUT_DIR,4);

}

void setIOLCD(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR,0);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR,1);

mcugear->setWire(IO_MBED_P23, IO_REG_OUT_DIR,2);

mcugear->setWire(IO_MBED_P24, IO_REG_OUT_DIR,3);

mcugear->setWire(IO_MBED_P25, IO_REG_OUT_DIR,4);

mcugear->setWire(IO_MBED_P26, IO_REG_OUT_DIR,5);

}

Sample code 2

Universal Module test program. This is show you that is possible to change schematic(bank).

Sample code 2

#include "mbed.h"

#include "TextLCD.h"

#include "MCUGearBaseM.h"

#include "MCUGearM.h"

#include "commonM.h"

Serial pc(USBTX, USBRX);

void setIOBank0(MCUGear *mcugear);

void setIOBank1(MCUGear *mcugear);

void setIOBank2(MCUGear *mcugear);

void setIOBank3(MCUGear *mcugear);

void setIOBank4(MCUGear *mcugear);

void setIOBank5(MCUGear *mcugear);

void setIOBank6(MCUGear *mcugear);

void setIOBank7(MCUGear *mcugear);

DigitalOut myled(LED1);

MCUGear UniM(p28, p27, N_VDD_VDD_VDD); //2 Connector Universal Module

DigitalOut Dout1(p16);

DigitalOut Dout2(p21);

DigitalOut Dout3(p22);

DigitalOut Dout4(p23);

DigitalOut Dout5(p24);

DigitalIn Din1(p9);

DigitalIn Din2(p10);

int main() {

int sw1 = 0;

int sw2 = 0;

int nowBank = 0;

initBase(); //initialize Baseboard

//set schematic select 0-7

int location = UniM.detectModule(); //save location data in MCUGear class and you can check return data.Baseboard has 0-47 pin.

printf("location = %d\n", &location);

startReg(0);

setIOBank0(&UniM);//make schematic Bank0

endReg(0);

startReg(1);

setIOBank1(&UniM);//make schematic Bank1

endReg(1);

startReg(2);

setIOBank2(&UniM);//make schematic Bank2

endReg(2);

startReg(3);

setIOBank3(&UniM);//make schematic Bank3

endReg(3);

startReg(4);

setIOBank4(&UniM);//make schematic Bank4

endReg(4);

startReg(5);

setIOBank5(&UniM);//make schematic Bank5

endReg(5);

startReg(6);

setIOBank6(&UniM);//make schematic Bank6

endReg(6);

startReg(7);

setIOBank7(&UniM);//make schematic Bank7

endReg(7);

changeBank(0);//select Bank

while(1) {

UniM.connectModule();

sw1 = Din1.read();

sw2 = Din2.read();

printf("sw1 = %d sw2 = %d\r\n",sw1,sw2);

Dout1 = 0;

Dout2 = 1;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 0;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 1;

Dout3 = 0;

wait(0.3);

UniM.disconnectModule();

if(sw1==0){//chage Bank

++nowBank;

if(nowBank >= 8){

nowBank = 0;

}

changeBank(nowBank);

printf("nowBank = %d\r\n",nowBank);

}

}

}

void setIOBank0(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

}

void setIOBank1(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

}

void setIOBank2(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 4);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 2);

}

void setIOBank3(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 2);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 4);

}

void setIOBank4(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 4);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 2);

}

void setIOBank5(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 2);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 4);

}

void setIOBank6(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 4);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 2);

}

void setIOBank7(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 2);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 4);

}

日本語説明

MCU Gearのマニュアルモードライブラリです。

detail : http://mcugear.com/en/ 8つの回路図(Bank 0~7 )をベースボードに保存できます。

使い方

1,ライブラリをインクルード

1,include library

#include "mbed.h" #include "MCUGearBaseM.h" #include "MCUGearM.h" #include "commonM.h"

2,モジュールを定義します。

(! 同じ回路図(Bank)で使うモジュールは積層しないでください。)

2,Declare Module

MCUGear myModule1(p28, p27, N_***_***_***); MCUGear myModule2(p28, p27, N_***_***_***);

myModule: モジュールに好きな名前を付けてください。

p28, p27, : I2C pins (KL25Z is "PTE0, PTE1")

N_*_*_* : Address. モジュールの裏面に設定したアドレスです。

3,ベースボードの初期化

3,Initialize baseboard

initBase();

4,配線データの作成

4,Call wiring register

startReg(bank);

myModule1.setWire(IO_MBED_P9, IO_REG_IN_DIR, 5);

myModule1.setWire(IO_MBED_P15, IO_REG_OUT_DIR, 2);

myModule1.setWire(IO_MBED_P12, IO_REG_OUT_DIR, 0);

myModule2.setWire(IO_MBED_P13, IO_REG_OUT_DIR, 1);

myModule2.setWire(IO_MBED_P14, IO_REG_IN_DIR, 3);

myModule2.setWire(IO_MBED_P16, IO_REG_IN_DIR, 4);

endReg(bank);

IOの定義番号などは MCUGearBaseboard.h ファイルを参考にしてください。

4,Call wiring register

// CPU I/O

typedef enum {

#if defined TARGET_LPC1768

IO_MBED_P15 = 0x80,

IO_MBED_P13,

IO_MBED_P16,

IO_MBED_P12,

IO_MBED_P5,

IO_MBED_P11,

IO_MBED_P23,

IO_MBED_P22,

IO_MBED_P26,

IO_MBED_P10,

IO_MBED_P21,

IO_MBED_P9,

IO_MBED_P6,

IO_MBED_P7,

IO_MBED_P8,

IO_MBED_P14,

IO_MBED_P24,

IO_MBED_P25,

IO_MBED_P28,

IO_MBED_P27

#endif

#if defined TARGET_KL25Z

IO_MBED_PTA5 = 0x80,

IO_MBED_PTC8,

IO_MBED_PTC9,

IO_MBED_PTD5,

IO_MBED_PTA13,

IO_MBED_PTD2,

IO_MBED_PTB1,

IO_MBED_PTB2,

IO_MBED_PTA2,

IO_MBED_PTD4,

IO_MBED_PTB3,

IO_MBED_PTA12,

IO_MBED_PTD0,

IO_MBED_PTD3,

IO_MBED_PTD1,

IO_MBED_PTA4,

IO_MBED_PTB0,

IO_MBED_PTA1,

IO_MBED_PTE0, //SDA

IO_MBED_PTE1 //SCL

#endif

} en_cpu_io;

-

startReg function

void startReg(uint8_t bank);

uint8_t bank : bankは回路図の事で、0~7まで設定できます。動作中にも何度も書き換えも可能です。

setWire function

uint8_t setWire(uint8_t mcuIO, uint8_t direction, uint8_t moduleIO);

setWire()関数はmbedの端子とモジュールの端子の割り振り方を決める関数です。

uint8_t mcuIO : mbedの18端子がアダプターボード(MCUボード)を介してベースボードに接続されています。(残りの端子はアダプターボード(MCUボード)から端子が出ています。)

uint8_t direction: mbedから見て入力か出力かを設定します。 IO_REG_OUT_DIR : output from MCU IO_REG_IN_DIR : input to MCU

uint8_t moduleIO: モジュールの出口の端子をどれにするかを決めます。

endReg function

void endReg(uint8_t bank);

uint8_t bank : bankは回路図の事で、0~7まで設定できます。動作中にも何度も書き換えも可能です。必ず "starReg()"のBankと同じ値にしてください。

上記と同様に、他の回路図(Bank)も作ることができます。

5,回路図(Bank)の切替

5,Change the schematic (bank)

void changeBank(uint8_t bank);

回路図は上記の関数で、Bankの値を0~7を入れれば、すぐに切り替えることができます。 (実行前にモジュールのゲートは閉じておくと安全です。)

6,モジュールのゲート開閉

6,Open or close the module gate

myModule1.connectModule(); myModule2.connectModule(); ... (same as normal mbed code) ... myModule1.disconnectModule(); myModule2.disconnectModule();

モジュールのゲートを開けるにはconnectModule()関数、閉じるにはdisconnectModule()関数です。

回路図(Bank)を保存して、複数のモジュールゲートを開いたまま動作させることができます!

Sample code 1

ユニバーサルモジュールとLCDモジュールを同時に接続したまま使うテストプログラムです。

ユニバーサルモジュールは以下の図のように接続します。

Sample code 1

#include "mbed.h"

#include "TextLCD.h"

#include "MCUGearBase.h"

#include "MCUGear.h"

#include "common.h"

Serial pc(USBTX, USBRX);

void setIOUni(MCUGear *mcugear);

void setIOLCD(MCUGear *mcugear);

DigitalOut myled(LED1);

MCUGear UniM(p28, p27, N_VDD_VDD_VDD); //2 Connector Universal Module

MCUGear LCDM(p28, p27, N_VDD_VSS_VSS); //LCD Module

DigitalOut Dout1(p11);

DigitalOut Dout2(p12);

DigitalOut Dout3(p13);

DigitalOut Dout4(p14);

DigitalOut Dout5(p15);

DigitalIn Din1(p9);

DigitalIn Din2(p10);

int main() {

int sw1 = 0;

int sw2 = 0;

int nowBank = 0;

initBase(); //initialize Baseboard

//set schematic select 0-7

UniM.detectModule(); //save location data in MCUGear class.

LCDM.detectModule(); //save location data in MCUGear class.

startReg(0);

setIOUni(&UniM);//make schematic Bank0

setIOLCD(&LCDM);//make schematic Bank0

endReg(0);

changeBank(0);//select Bank

LCDM.connectModule();

TextLCD lcd(p21, p22, p23, p24, p25, p26, TextLCD::LCD16x2); // rs, e, d4-d7

lcd.cls();

lcd.printf("Hello World!\n");

wait(1);

LCDM.disconnectModule();

UniM.connectModule();//open the module gate

LCDM.connectModule();//open the module gate

while(1) {

//UniM.connectModule();

//LCDM.connectModule();

sw1 = Din1.read();

sw2 = Din2.read();

printf("sw1 = %d sw2 = %d\r\n",sw1,sw2);

lcd.printf(" "); //set IO as a neutral position

lcd.cls(); //clear LCD

lcd.printf("sw1 = %d\nsw2 = %d",sw1,sw2); //write LCD data

wait_ms(10); //delay for view the LCD

Dout1 = 0;

Dout2 = 1;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 0;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 1;

Dout3 = 0;

wait(0.3);

//UniM.disconnectModule();//close the module gate

//LCDM.disconnectModule();//close the module gate

}

}

void setIOUni(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P11, IO_REG_OUT_DIR,2);

mcugear->setWire(IO_MBED_P12, IO_REG_OUT_DIR,3);

mcugear->setWire(IO_MBED_P13, IO_REG_OUT_DIR,4);

}

void setIOLCD(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR,0);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR,1);

mcugear->setWire(IO_MBED_P23, IO_REG_OUT_DIR,2);

mcugear->setWire(IO_MBED_P24, IO_REG_OUT_DIR,3);

mcugear->setWire(IO_MBED_P25, IO_REG_OUT_DIR,4);

mcugear->setWire(IO_MBED_P26, IO_REG_OUT_DIR,5);

}

Sample code 2

ユニバーサルモジュールに、沢山の回路図(Bank)を設定して、スイッチ1(sw1)に当たる端子が押されたときにバンクを切り替えて動きます。

Sample code 2

#include "mbed.h"

#include "TextLCD.h"

#include "MCUGearBaseM.h"

#include "MCUGearM.h"

#include "commonM.h"

Serial pc(USBTX, USBRX);

void setIOBank0(MCUGear *mcugear);

void setIOBank1(MCUGear *mcugear);

void setIOBank2(MCUGear *mcugear);

void setIOBank3(MCUGear *mcugear);

void setIOBank4(MCUGear *mcugear);

void setIOBank5(MCUGear *mcugear);

void setIOBank6(MCUGear *mcugear);

void setIOBank7(MCUGear *mcugear);

DigitalOut myled(LED1);

MCUGear UniM(p28, p27, N_VDD_VDD_VDD); //2 Connector Universal Module

DigitalOut Dout1(p16);

DigitalOut Dout2(p21);

DigitalOut Dout3(p22);

DigitalOut Dout4(p23);

DigitalOut Dout5(p24);

DigitalIn Din1(p9);

DigitalIn Din2(p10);

int main() {

int sw1 = 0;

int sw2 = 0;

int nowBank = 0;

initBase(); //initialize Baseboard

//set schematic select 0-7

int location = UniM.detectModule(); //save location data in MCUGear class and you can check return data.Baseboard has 0-47 pin.

printf("location = %d\n", &location);

startReg(0);

setIOBank0(&UniM);//make schematic Bank0

endReg(0);

startReg(1);

setIOBank1(&UniM);//make schematic Bank1

endReg(1);

startReg(2);

setIOBank2(&UniM);//make schematic Bank2

endReg(2);

startReg(3);

setIOBank3(&UniM);//make schematic Bank3

endReg(3);

startReg(4);

setIOBank4(&UniM);//make schematic Bank4

endReg(4);

startReg(5);

setIOBank5(&UniM);//make schematic Bank5

endReg(5);

startReg(6);

setIOBank6(&UniM);//make schematic Bank6

endReg(6);

startReg(7);

setIOBank7(&UniM);//make schematic Bank7

endReg(7);

changeBank(0);//select Bank

while(1) {

UniM.connectModule();

sw1 = Din1.read();

sw2 = Din2.read();

printf("sw1 = %d sw2 = %d\r\n",sw1,sw2);

Dout1 = 0;

Dout2 = 1;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 0;

Dout3 = 1;

wait(0.3);

Dout1 = 1;

Dout2 = 1;

Dout3 = 0;

wait(0.3);

UniM.disconnectModule();

if(sw1==0){//chage Bank

++nowBank;

if(nowBank >= 8){

nowBank = 0;

}

changeBank(nowBank);

printf("nowBank = %d\r\n",nowBank);

}

}

}

void setIOBank0(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

}

void setIOBank1(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

}

void setIOBank2(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 4);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 2);

}

void setIOBank3(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 2);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 4);

}

void setIOBank4(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 4);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 2);

}

void setIOBank5(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 2);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 4);

}

void setIOBank6(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 4);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 2);

}

void setIOBank7(MCUGear *mcugear){

mcugear->setWire(IO_MBED_P10, IO_REG_IN_DIR, 0);

mcugear->setWire(IO_MBED_P9, IO_REG_IN_DIR, 1);

mcugear->setWire(IO_MBED_P16, IO_REG_OUT_DIR, 2);

mcugear->setWire(IO_MBED_P21, IO_REG_OUT_DIR, 3);

mcugear->setWire(IO_MBED_P22, IO_REG_OUT_DIR, 4);

}

Revision 0:d2cb480cd5e0, committed 2013-09-29

- Comitter:

- Info

- Date:

- Sun Sep 29 10:16:02 2013 +0000

- Child:

- 1:bbcba1a79e7b

- Commit message:

- Ver1.0.0 MCUGear test program for mbed

; You should change the defines in common.h.

Changed in this revision

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/MCUGear.cpp Sun Sep 29 10:16:02 2013 +0000

@@ -0,0 +1,471 @@

+/* MCU Gear Library, only for testing MCUGear without any circuit you connected.

+ * Copyright (c) 2013, NestEgg Inc., http://www.mcugear.com/

+ *

+ * Permission is hereby granted, free of charge, to any person obtaining a copy

+ * of this software and associated documentation files (the "Software"), to deal

+ * in the Software without restriction, including without limitation the rights

+ * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

+ * copies of the Software, and to permit persons to whom the Software is

+ * furnished to do so, subject to the following conditions:

+ *

+ * The above copyright notice and this permission notice shall be included in

+ * all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

+ * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

+ * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

+ * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

+ * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

+ * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

+ * THE SOFTWARE.

+ */

+

+

+#include "mbed.h"

+#include "MCUGear.h"

+#include "MCUGearBase.h"

+

+#ifdef DEBUG

+Serial MCUGear_pc(USBTX, USBRX); // tx, rx

+#endif

+

+

+unsigned char Layer[12];

+unsigned char BankSetting[12][32];

+unsigned char BankAndInPins[7][20];

+

+unsigned char NowBank;

+

+//init

+//#ifdef BANK_MODE

+MCUGear::MCUGear(PinName scl, PinName sda, char addr, char NumberOfPin)

+ : _i2c(scl, sda) {

+ _i2c.frequency(FPGA_I2C_CLOCK);

+ _addr = addr;

+ data = 0x00;

+ flgReg = 0;

+ NowBank = 0;

+ numPin = NumberOfPin;

+// numCon = ConnectorNumber;

+ if(numPin<=4){

+ numCon = 1;

+ }else if((numPin > 4)&&(numPin <= 8)){

+ numCon = 2;

+ }else if(numPin > 8){

+ numCon = 3;

+ }else{

+ ;//error

+ }

+

+ write(0xff);

+

+}

+/*

+#else

+MCUGear::MCUGear(PinName scl, PinName sda, char a)

+ : _i2c(scl, sda) {

+ _i2c.frequency(FPGA_I2C_CLOCK);

+ _addr = a;

+ Bank = 0;

+ data = 0x00;

+ flgReg = 0;

+}

+

+#endif

+*/

+

+//insert data function

+

+void MCUGear::savePinSetting(uint8_t number, unsigned char CPUPin,unsigned char Direction ,unsigned char ModulePin){

+ ip[number] = CPUPin;

+ op[number] = (Direction|ModulePin);

+

+#ifdef DEBUG

+ MCUGear_pc.printf("ModulePin = %x :op[%d] = %x : ip[%d] = %x\n",ModulePin, number, op[number], number, ip[number]);

+ wait(0.1);

+ //MCUGear_pc.printf("sizeof(ModulePin) = %ubyte\n",sizeof(ModulePin));

+ //wait(0.1);

+#endif

+

+}

+/*

+uint8_t MCUGear::disconnectModule(void){

+

+ write(0xff); //close module gate

+

+ if(Bank == 0){

+ fpga_write(0x0c,(0|0x80));//regist - Delete all connection on Bank 0.

+ wait(0.001);

+ fpga_write(0x10, 0);//enable

+ }

+

+ return 1;

+

+}

+*/

+uint8_t MCUGear::disconnectModule(void){

+

+ write(0xff); //close module gate

+

+ if(Bank == 0){

+

+//#ifdef test

+ fpga_write(0x0c,(Bank|0x80));//regist - Delete all connection on Bank 0.

+ wait(0.001);

+ fpga_write(0x10, Bank);//enable

+/*#else

+ int i=0;

+

+ fpga_write(0x0c, 0);//regist

+ //Rest all IO connction on Bank 0.

+

+ for(i=0; i<16; ++i){

+ fpga_write(ip[i], (IO_REG_DISABLE | op[i]));

+ wait(0.0001);

+ }

+ fpga_write(0x10, (Bank|0x40));//enable

+

+#endif

+*/

+ }

+ return 1;

+

+}

+

+uint8_t MCUGear::connectModule(void){

+

+#ifdef DEBUG

+ MCUGear_pc.printf("_addr = %x, [NowBank = %d ,Bank = %d] \n",_addr, NowBank, Bank);

+ wait(0.1);

+#endif

+

+ int i=0;

+

+ if(flgReg==0){

+ fpga_write(0x0c,Bank);//init regist

+

+ }else{

+ if(Bank == NowBank){

+ ; //Nothing to do

+#ifdef DEBUG

+ MCUGear_pc.printf("_Nothing to do \n");

+ wait(0.1);

+#endif

+ }else{

+ fpga_write(0x0c,Bank);//regist

+ }

+ }

+

+

+ if(Bank != 0){ //Bank is between 1-7

+ if(flgReg==0){ //Onetime IO connections

+

+ for(i=0; i<16; ++i){

+ fpga_write(ip[i], (IO_REG_EN | op[i]));

+ wait(0.0001);

+

+ if((numCon==1)&&(i==3)){

+ write(0xfe); //1111 1110

+ break;

+

+ }else if((numCon==2)&&(i==7)){

+ write(0xfc); //1111 1100

+ break;

+

+ }else if((numCon==3)&&(i==11)){

+ write(0xf8); //1111 1000

+ break;

+

+ }else if(i > 12){

+ return 2;//error

+ }

+ }

+

+ fpga_write(0x10,Bank);//init regist///////

+ flgReg = 1;

+ }else{ //only change module gate

+

+ if(numCon==1){

+ write(0xfe); //1111 1110

+

+ }else if(numCon==2){

+ write(0xfc); //1111 1100

+

+ }else if(numCon==3){

+ write(0xf8); //1111 1000

+

+ }else{

+ return 2;//error

+ }

+

+ }

+//#else

+ }else{ //You need to change IO connections evrytime on Bank 0.

+ for(i=0; i<16; ++i){

+ fpga_write(ip[i], (IO_REG_EN | op[i]));

+ wait(0.0001);

+

+ if((numCon==1)&&(i==3)){

+ write(0xfe); //1111 1110

+ break;

+

+ }else if((numCon==2)&&(i==7)){

+ write(0xfc); //1111 1100

+ break;

+

+ }else if((numCon==3)&&(i==11)){

+ write(0xf8); //1111 1000

+ break;

+

+ }else if(i > 12){

+ return 2;//error

+ }

+ }

+ fpga_write(0x10,Bank);//init regist///////

+ }

+//#endif

+/*

+ if(flgReg==0){

+ flgReg = 1;

+ fpga_write(0x10,Bank);//init regist

+

+ }else{

+ if(Bank == NowBank){

+ ; //Nothing to do

+#ifdef DEBUG

+ MCUGear_pc.printf("_Nothing to do \n");

+ wait(0.1);

+#endif

+ }else{

+ fpga_write(0x10,Bank);//regist

+ }

+ }

+*/

+

+ /*

+ if((Bank != NowBank)){

+ fpga_write(0x10, Bank); //Bank enable

+ }

+ */

+ NowBank = Bank; //set NowBank

+

+ return 1;

+}

+

+

+

+void MCUGear::fpga_write(unsigned char adr, unsigned char data) {

+ char cmd[2];

+ cmd[0] = adr;

+ cmd[1] = data;

+ _i2c.write(FPGA_I2C_ADR, cmd, 2);

+ //wait(0.01);

+ //pc.printf("fpga write adr:%x data:%x\n", adr,data);

+}

+

+

+void MCUGear::set_addr(char s){

+ _addr = s;

+}

+

+void MCUGear::set_data(char c){

+ data = c;

+}

+

+//send I2C signal function

+void MCUGear::write(char c){

+

+ char cmd[1];

+ cmd[0] = c;

+ _i2c.write(_addr, cmd, 1);

+ //wait(0.01);

+

+}

+

+////detect module

+void MCUGear::detect_module(uint8_t *fio) {

+ int i;

+ uint8_t pnum=0xff;

+ uint8_t iio;

+ //1pin GND

+

+ write(0x7f); //0111 1111

+ //wait(0.1);

+ pnum =fpga_read(FPGA_I2C_ADR,FPGA_DETECT);

+

+#ifdef DEBUG

+ wait(1);

+ MCUGear_pc.printf("detected. port %d \n",pnum);

+ wait(0.1);

+#endif

+ write(0xff); //1111 1111

+

+ iio = pnum;

+ if(iio != 0xff){

+ //Resolve boundary value problem

+ pinArrey[0] = iio;

+

+ iio = iio + 4;

+

+ if((iio > 44)){

+ iio = 0;;

+ }

+ pinArrey[1] = iio;

+

+

+ iio = iio + 4;

+

+ if((iio > 44)){

+ iio = 0;

+ }

+ pinArrey[2] = iio;

+

+#ifdef DEBUG

+ MCUGear_pc.printf("detected. pinArrey[0] = %d \n",pinArrey[0]);

+ wait(0.1);

+#endif

+

+ //makeCircuit();

+ }

+

+ for(i=0;i<12;++i){

+ if(pnum+i>47){

+ fio[i] = pnum+i-48;

+ }else{

+ fio[i] = pnum+i;

+ }

+

+

+#ifdef DEBUG

+ //MCUGear_pc.printf("detected. fio[%d] = %d \n",i,fio[i]);

+ //wait(0.1);

+#endif

+

+ }

+

+ // return pnum;

+}

+

+

+

+///making onecircuit

+void MCUGear::makeCircuit(void){

+ //unsigned char i = 0;

+ char i = 0;

+ unsigned char j = 0;

+ int k = 0;

+ unsigned char con = 0;

+ unsigned char conNum2 = 0;

+ unsigned char MaxLayer = 0;

+

+ con = (pinArrey[0]/4)+1; //creat connector number

+

+#ifdef DEBUG

+ MCUGear_pc.printf("makeCircuit con = (pinArrey[%d]/4)+1 = %d \n",i,con);

+ wait(0.1);

+#endif

+

+ //find MaxLayer

+ for(i=0; i<numCon; ++i){

+ if((con+i) > 12){

+ ++Layer[con + i - 12];

+

+ if(MaxLayer < Layer[con + i - 12]){

+ MaxLayer = Layer[con + i - 12];

+ }

+ }else{

+ ++Layer[con + i];

+

+ if(MaxLayer < Layer[con + i]){

+ MaxLayer = Layer[con + i];

+ }

+ }

+ }

+

+ //Check over rap CPU pins on a Bank

+ //If it find over rap, set other layers.

+ conNum2 = numCon * 4;

+

+ for(i=0; i<20; ++i){

+ for(j=0; j<numPin; ++j){

+ if(BankAndInPins[MaxLayer][i] == ip[j]){

+ ++MaxLayer;

+

+#ifdef DEBUG

+ MCUGear_pc.printf("CPU IO over rap! ++MaxLayer : %d \n",MaxLayer);

+ wait(0.1);

+#endif

+ //i = 0x20;

+ //j = numPin;

+ //break;

+ i = 0;

+ j = 0;

+ }

+ }

+ }

+

+ //Save Datas

+ for(j=0; j<conNum2; ++j){

+ k = (int)(ip[j]-0x80);

+ BankAndInPins[MaxLayer][k] = ip[j];

+#ifdef DEBUG

+ MCUGear_pc.printf("BankAndInPins[%d][%d] = %x \n",MaxLayer,k,ip[j]);

+ wait(0.1);

+#endif

+ }

+

+

+ //save MaxLayer to all connectors

+ for(i=0; i<numCon; ++i){

+ if(MaxLayer > Layer[con + i]){

+ Layer[con + i] = MaxLayer;

+ }

+

+ }

+

+

+#ifdef DEBUG

+ MCUGear_pc.printf("MaxLayer = %d \n",MaxLayer);

+ wait(0.1);

+#endif

+

+ for(i=0; i<numCon; ++i){

+

+ if((con + i)>12){

+ BankSetting[con + i - 12][MaxLayer] = _addr;

+

+#ifdef DEBUG

+ MCUGear_pc.printf("BankSetting[CON %d][Layer %d] = %x \n",(con + i - 12),MaxLayer,_addr);

+ wait(0.1);

+#endif

+ }else{

+ BankSetting[con + i][MaxLayer] = _addr;

+

+#ifdef DEBUG

+ MCUGear_pc.printf("BankSetting[CON %d][Layer %d] = %x \n",(con + i),MaxLayer,_addr);

+ wait(0.1);

+#endif

+ }

+ }

+

+

+ //make 0-6 BANKs others are chang single pin

+ //MaxLayer = BANK No

+

+ if(MaxLayer <= BankMaxNum){

+ fpga_write(0x0c, MaxLayer); //regist to Bank

+ Bank = MaxLayer;

+ }else{

+ Bank = 0;

+#ifdef DEBUG

+ MCUGear_pc.printf("set Bank = 0\n");

+ wait(0.1);

+#endif

+

+ }

+

+}

+

+

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/MCUGear.h Sun Sep 29 10:16:02 2013 +0000

@@ -0,0 +1,66 @@

+/* MCU Gear Library, only for testing MCUGear without any circuit you connected.

+ * Copyright (c) 2013, NestEgg Inc., http://www.mcugear.com/

+ *

+ * Permission is hereby granted, free of charge, to any person obtaining a copy

+ * of this software and associated documentation files (the "Software"), to deal

+ * in the Software without restriction, including without limitation the rights

+ * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

+ * copies of the Software, and to permit persons to whom the Software is

+ * furnished to do so, subject to the following conditions:

+ *

+ * The above copyright notice and this permission notice shall be included in

+ * all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

+ * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

+ * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

+ * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

+ * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

+ * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

+ * THE SOFTWARE.

+ */

+

+#include "common.h"

+

+class MCUGear

+{

+ public:

+//#ifdef BANK_MODE

+ MCUGear(PinName sda, PinName scl, char addr, char NumberOfPin);

+//#else

+// MCUGear(PinName sda, PinName scl, char a);

+//#endif

+ void set_addr(char s);

+ void set_data(char c);

+ void write(char c);

+ char data;

+ char _addr;

+ void savePinSetting(uint8_t number, unsigned char CPUPin, unsigned char Direction ,unsigned char ModulePin);

+ uint8_t connectModule(void);

+ uint8_t disconnectModule(void);

+ void fpga_write(unsigned char adr, unsigned char data);

+ void detect_module(uint8_t *fio);

+ void makeCircuit(void);

+

+ protected:

+ I2C _i2c;

+ char Bank;

+ char flgReg;

+ char numPin;

+ char numCon;

+ unsigned char pinArrey[3];

+

+ uint8_t ip[12];

+ uint8_t op[12];

+

+ typedef enum {

+ IO_REG_EN = 0x80,

+ IO_REG_OUT_DIR = 0x40,

+ IO_REG_IN_DIR = 0x00,

+ IO_REG_DISABLE = 0x3f

+ } en_fpga_io_reg;

+

+};

+

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/MCUGearBase.cpp Sun Sep 29 10:16:02 2013 +0000

@@ -0,0 +1,117 @@

+/* MCU Gear Library, only for testing MCUGear without any circuit you connected.

+ * Copyright (c) 2013, NestEgg Inc., http://www.mcugear.com/

+ *

+ * Permission is hereby granted, free of charge, to any person obtaining a copy

+ * of this software and associated documentation files (the "Software"), to deal

+ * in the Software without restriction, including without limitation the rights

+ * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

+ * copies of the Software, and to permit persons to whom the Software is

+ * furnished to do so, subject to the following conditions:

+ *

+ * The above copyright notice and this permission notice shall be included in

+ * all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

+ * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

+ * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

+ * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

+ * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

+ * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

+ * THE SOFTWARE.

+ */

+

+#include "mbed.h"

+#include "MCUGearBase.h"

+

+#ifdef LPC1768_mbed

+I2C fpga_i2c(p28, p27);

+#endif

+

+#ifdef FS_KL25Z

+I2C fpga_i2c(PTE0, PTE1);

+#endif

+

+

+

+

+#ifdef DEBUG

+Serial fpga_pc(USBTX, USBRX); // tx, rx

+#endif

+

+void fpga_write(int dev_adr,unsigned char adr, unsigned char data) {

+ char cmd[2];

+ cmd[0] = adr;

+ cmd[1] = data;

+ fpga_i2c.frequency (FPGA_I2C_CLOCK);

+ fpga_i2c.write(dev_adr, cmd, 2);

+ //wait(0.01);

+

+#ifdef DEBUG

+ fpga_pc.printf("fpga write adr:%x data:%x\n", adr,data);

+#endif

+

+}

+

+unsigned char fpga_read(int dev_adr,unsigned char adr) {

+ char cmd[2];

+ cmd[0] = adr;

+ fpga_i2c.write(dev_adr, cmd, 1);

+ //wait(0.01);

+ fpga_i2c.read(dev_adr, cmd, 1);

+ //wait(0.01);

+ //pc.printf("fpga read adr:%x data:%x\n", adr,cmd[0]);

+ return cmd[0];

+}

+

+void initBase(void){

+

+#ifdef DEBUG

+ fpga_pc.baud(BaudRate);

+#endif

+

+ // FPGA reg clear

+ for (int i=0;i<20;i++)

+ fpga_write(FPGA_I2C_ADR,0x80+i,0);

+

+ // read FPGA registers

+

+#ifdef DEBUG

+ fpga_pc.printf("I2C test\n");

+#endif

+ fpga_read(FPGA_I2C_ADR,FPGA_SYSINFO_0);

+ fpga_read(FPGA_I2C_ADR,FPGA_SYSINFO_0+1);

+ fpga_read(FPGA_I2C_ADR,FPGA_SYSINFO_0+2);

+ fpga_read(FPGA_I2C_ADR,FPGA_SYSINFO_0+3);

+ // FPGA enable

+ fpga_write(FPGA_I2C_ADR,FPGA_ENABLE,1);

+

+}

+

+

+void I2Cwrite(char addr, char data){

+

+ char cmd[1];

+ cmd[0] = data;

+ fpga_i2c.write(addr, cmd, 1);

+ //wait(0.01);

+

+}

+

+int detect_module(char addr) {

+ int pnum=0xff;

+ //1pin GND

+ I2Cwrite(addr,0x7f); //0111 1111

+ //wait(0.1);

+ pnum =fpga_read(FPGA_I2C_ADR,FPGA_DETECT);

+ wait(1);

+#ifdef DEBUG

+ fpga_pc.printf("detected. port %d \n",pnum);

+#endif

+ I2Cwrite(addr,0xff); //1111 1111

+ //wait(0.1);

+ return pnum;

+}

+

+

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000

+++ b/MCUGearBase.h Sun Sep 29 10:16:02 2013 +0000

@@ -0,0 +1,157 @@

+/* MCU Gear Library, only for testing MCUGear without any circuit you connected.

+ * Copyright (c) 2013, NestEgg Inc., http://www.mcugear.com/

+ *

+ * Permission is hereby granted, free of charge, to any person obtaining a copy

+ * of this software and associated documentation files (the "Software"), to deal

+ * in the Software without restriction, including without limitation the rights

+ * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

+ * copies of the Software, and to permit persons to whom the Software is

+ * furnished to do so, subject to the following conditions:

+ *

+ * The above copyright notice and this permission notice shall be included in

+ * all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

+ * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

+ * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

+ * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

+ * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

+ * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN

+ * THE SOFTWARE.

+ */

+

+#include "common.h"

+

+

+#define FPGA_SYSINFO_0 0x00

+#define FPGA_SYSINFO_1 0x04

+#define FPGA_ENABLE 0x08

+#define FPGA_DETECT 0x14

+

+/*

+// cpu port mapping

+#define P5 0

+//

+#define CON1_1 0

+#define CON1_2 0

+#define CON1_3 0

+#define CON1_4 0

+*/

+void fpga_write(int dev_adr,unsigned char adr, unsigned char data);

+unsigned char fpga_read(int dev_adr,unsigned char adr);

+void initBase(void);

+int detect_module(char addr);

+

+

+// FGPGA CPU I/O

+typedef enum {

+

+#ifdef LPC1768_mbed

+ IO_MBED_P15 = 0x80,

+ IO_MBED_P13,

+ IO_MBED_P16,

+ IO_MBED_P12,

+ IO_MBED_P5,

+ IO_MBED_P11,

+ IO_MBED_P23,

+ IO_MBED_P22,

+ IO_MBED_P26,

+ IO_MBED_P10,

+ IO_MBED_P21,

+ IO_MBED_P9,

+ IO_MBED_P6,

+ IO_MBED_P7,

+ IO_MBED_P8,

+ IO_MBED_P14,

+ IO_MBED_P24,

+ IO_MBED_P25,

+ IO_MBED_P28,

+ IO_MBED_P27

+#endif

+

+#ifdef FS_KL25Z

+

+ IO_MBED_PTA5 = 0x80,

+ IO_MBED_PTC8,

+ IO_MBED_PTC9,

+ IO_MBED_PTD5,

+ IO_MBED_PTA13,

+ IO_MBED_PTD2,

+ IO_MBED_PTB1,

+ IO_MBED_PTB2,

+ IO_MBED_PTA2,

+ IO_MBED_PTD4,

+ IO_MBED_PTB3,

+ IO_MBED_PTA12,

+ IO_MBED_PTD0,

+ IO_MBED_PTD3,

+ IO_MBED_PTD1,

+ IO_MBED_PTA4,

+ IO_MBED_PTB0,

+ IO_MBED_PTA1,

+ IO_MBED_PTE0, //SDA

+ IO_MBED_PTE1 //SCL

+#endif

+

+} en_cpu_io;

+

+// FPGA EXT I/O

+typedef enum {

+ IO_CON1_1 = 0,

+ IO_CON1_2,

+ IO_CON1_3,

+ IO_CON1_4,

+ IO_CON2_1,

+ IO_CON2_2,

+ IO_CON2_3,

+ IO_CON2_4,

+ IO_CON3_1,

+ IO_CON3_2,

+ IO_CON3_3,

+ IO_CON3_4,

+ IO_CON4_1,

+ IO_CON4_2,

+ IO_CON4_3,

+ IO_CON4_4,

+ IO_CON5_1,

+ IO_CON5_2,

+ IO_CON5_3,

+ IO_CON5_4,

+ IO_CON6_1,

+ IO_CON6_2,

+ IO_CON6_3,

+ IO_CON6_4,

+ IO_CON7_1,

+ IO_CON7_2,

+ IO_CON7_3,

+ IO_CON7_4,

+ IO_CON8_1,

+ IO_CON8_2,

+ IO_CON8_3,

+ IO_CON8_4,

+ IO_CON9_1,

+ IO_CON9_2,

+ IO_CON9_3,

+ IO_CON9_4,

+ IO_CON10_1,

+ IO_CON10_2,

+ IO_CON10_3,

+ IO_CON10_4,

+ IO_CON11_1,

+ IO_CON11_2,

+ IO_CON11_3,

+ IO_CON11_4,

+ IO_CON12_1,

+ IO_CON12_2,

+ IO_CON12_3,

+ IO_CON12_4

+} en_fpga_io;

+

+typedef enum {

+ IO_REG_EN = 0x80,

+ IO_REG_OUT_DIR = 0x40,

+ IO_REG_IN_DIR = 0x00,

+ IO_REG_DISABLE = 0x3f

+} en_fpga_io_reg;

+

+

--- /dev/null Thu Jan 01 00:00:00 1970 +0000 +++ b/common.h Sun Sep 29 10:16:02 2013 +0000 @@ -0,0 +1,206 @@ +/* MCU Gear Library, only for testing MCUGear without any circuit you connected. + * Copyright (c) 2013, NestEgg Inc., http://www.mcugear.com/ + * + * Permission is hereby granted, free of charge, to any person obtaining a copy + * of this software and associated documentation files (the "Software"), to deal + * in the Software without restriction, including without limitation the rights + * to use, copy, modify, merge, publish, distribute, sublicense, and/or sell + * copies of the Software, and to permit persons to whom the Software is + * furnished to do so, subject to the following conditions: + * + * The above copyright notice and this permission notice shall be included in + * all copies or substantial portions of the Software. + * + * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR + * IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, + * FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE + * AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER + * LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, + * OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN + * THE SOFTWARE. + */ + + +//select your mbed-------------------------------------------- +#define LPC1768_mbed +//#define FS_KL25Z + +//#define BOOST_MODE //if you want use BANK System, define this. +//------------------------------------------------------------ + +//For Sample Mltifunction Mofdule----------------------------- +//#define AD_MODE +//#define PWM_MODE +//#define I2C_MODE + +//------------------------------------------------------------ + + + + +//#define DEBUG //If you need to debug, define this. +#ifdef LPC1768_mbed + +#define BaudRate 9600 +#define FPGA_I2C_CLOCK 1000000 +#define MODULE_I2C_CLOCK 1000000 + +#endif + +#ifdef FS_KL25Z + +#define BaudRate 19200 +#define FPGA_I2C_CLOCK 2000000 //about 769kHz +#define MODULE_I2C_CLOCK 2000000 + +#endif + + +#define FPGA_I2C_ADR 0x78 + +#ifdef DEBUG +#define BankMaxNum 3 //you can set 1 to 7 BANKs for Debug Mode. + +#else +#define BankMaxNum 7 //BANK layers + +#endif + +//PCA9674 + //VSS = GND VDD = +3.3V + //AD2 AD1 AD0 +#define N_VSS_SCL_VSS 0x20 +#define N_VSS_SCL_VDD 0x22 +#define N_VSS_SDA_VSS 0x24 +#define N_VSS_SDA_VDD 0x26 +#define N_VDD_SCL_VSS 0x28 +#define N_VDD_SCL_VDD 0x2A +#define N_VDD_SDA_VSS 0x2C +#define N_VDD_SDA_VDD 0x2E +#define N_VSS_SCL_SCL 0x30 +#define N_VSS_SCL_SDA 0x32 +#define N_VSS_SDA_SCL 0x34 +#define N_VSS_SDA_SDA 0x36 +#define N_VDD_SCL_SCL 0x38 +#define N_VDD_SCL_SDA 0x3A +#define N_VDD_SDA_SCL 0x3C +#define N_VDD_SDA_SDA 0x3E +#define N_VSS_VSS_VSS 0x40 +#define N_VSS_VSS_VDD 0x42 +#define N_VSS_VDD_VSS 0x44 +#define N_VSS_VDD_VDD 0x46 +#define N_VDD_VSS_VSS 0x48 +#define N_VDD_VSS_VDD 0x4A +#define N_VDD_VDD_VSS 0x4C +#define N_VDD_VDD_VDD 0x4E +#define N_VSS_VSS_SCL 0x50 +#define N_VSS_VSS_SDA 0x52 +#define N_VSS_VDD_SCL 0x54 +#define N_VSS_VDD_SDA 0x56 +#define N_VDD_VSS_SCL 0x58 +#define N_VDD_VSS_SDA 0x5A +#define N_VDD_VDD_SCL 0x5C +#define N_VDD_VDD_SDA 0x5E +#define N_SCL_SCL_VSS 0xA0 +#define N_SCL_SCL_VDD 0xA2 +#define N_SCL_SDA_VSS 0xA4 +#define N_SCL_SDA_VDD 0xA6 +#define N_SDA_SCL_VSS 0xA8 +#define N_SDA_SCL_VDD 0xAA +#define N_SDA_SDA_VSS 0xAC +#define N_SDA_SDA_VDD 0xAE +#define N_SCL_SCL_SCL 0xB0 +#define N_SCL_SCL_SDA 0xB2 +#define N_SCL_SDA_SCL 0xB4 +#define N_SCL_SDA_SDA 0xB6 +#define N_SDA_SCL_SCL 0xB8 +#define N_SDA_SCL_SDA 0xBA +#define N_SDA_SDA_SCL 0xBC +#define N_SDA_SDA_SDA 0xBE +#define N_SCL_VSS_VSS 0xC0 +#define N_SCL_VSS_VDD 0xC2 +#define N_SCL_VDD_VSS 0xC4 +#define N_SCL_VDD_VDD 0xC6 +#define N_SDA_VSS_VSS 0xC8 +#define N_SDA_VSS_VDD 0xCA +#define N_SDA_VDD_VSS 0xCC +#define N_SDA_VDD_VDD 0xCE +#define N_SCL_VSS_SCL 0xE0 +#define N_SCL_VSS_SDA 0xE2 +#define N_SCL_VDD_SCL 0xE4 +#define N_SCL_VDD_SDA 0xE6 +#define N_SDA_VSS_SCL 0xE8 +#define N_SDA_VSS_SDA 0xEA +#define N_SDA_VDD_SCL 0xEC +#define N_SDA_VDD_SDA 0xEE + + +//PCA9674A + //VSS = GND VDD = +3.3V + //AD2 AD1 AD0 +#define A_VSS_SCL_VSS 0x10 +#define A_VSS_SCL_VDD 0x12 +#define A_VSS_SDA_VSS 0x14 +#define A_VSS_SDA_VDD 0x16 +#define A_VDD_SCL_VSS 0x18 +#define A_VDD_SCL_VDD 0x1A +#define A_VDD_SDA_VSS 0x1C +#define A_VDD_SDA_VDD 0x1E +#define A_VSS_SCL_SCL 0x60 +#define A_VSS_SCL_SDA 0x62 +#define A_VSS_SDA_SCL 0x64 +#define A_VSS_SDA_SDA 0x66 +#define A_VDD_SCL_SCL 0x68 +#define A_VDD_SCL_SDA 0x6A +#define A_VDD_SDA_SCL 0x6C +#define A_VDD_SDA_SDA 0x6E +#define A_VSS_VSS_VSS 0x70 +#define A_VSS_VSS_VDD 0x72 +#define A_VSS_VDD_VSS 0x74 +#define A_VSS_VDD_VDD 0x76 +//#define A_VDD_VSS_VSS 0x78 //This is baseboard address. It is reserved. +#define A_VDD_VSS_VDD 0x7A +#define A_VDD_VDD_VSS 0x7C +#define A_VDD_VDD_VDD 0x7E +#define A_VSS_VSS_SCL 0x80 +#define A_VSS_VSS_SDA 0x82 +#define A_VSS_VDD_SCL 0x84 +#define A_VSS_VDD_SDA 0x86 +#define A_VDD_VSS_SCL 0x88 +#define A_VDD_VSS_SDA 0x8A +#define A_VDD_VDD_SCL 0x8C +#define A_VDD_VDD_SDA 0x8E +#define A_SCL_SCL_VSS 0x90 +#define A_SCL_SCL_VDD 0x92 +#define A_SCL_SDA_VSS 0x94 +#define A_SCL_SDA_VDD 0x96 +#define A_SDA_SCL_VSS 0x98 +#define A_SDA_SCL_VDD 0x9A +#define A_SDA_SDA_VSS 0x9C +#define A_SDA_SDA_VDD 0x9E +#define A_SCL_SCL_SCL 0xD0 +#define A_SCL_SCL_SDA 0xD2 +#define A_SCL_SDA_SCL 0xD4 +#define A_SCL_SDA_SDA 0xD6 +#define A_SDA_SCL_SCL 0xD8 +#define A_SDA_SCL_SDA 0xDA +#define A_SDA_SDA_SCL 0xDC +#define A_SDA_SDA_SDA 0xDE +#define A_SCL_VSS_VSS 0xF0 +#define A_SCL_VSS_VDD 0xF2 +#define A_SCL_VDD_VSS 0xF4 +#define A_SCL_VDD_VDD 0xF6 +#define A_SDA_VSS_VSS 0xF8 +#define A_SDA_VSS_VDD 0xFA +#define A_SDA_VDD_VSS 0xFC +#define A_SDA_VDD_VDD 0xFE +#define A_SCL_VSS_SCL 0x00 +#define A_SCL_VSS_SDA 0x02 +#define A_SCL_VDD_SCL 0x04 +#define A_SCL_VDD_SDA 0x06 +#define A_SDA_VSS_SCL 0x08 +#define A_SDA_VSS_SDA 0x0A +#define A_SDA_VDD_SCL 0x0C +#define A_SDA_VDD_SDA 0x0E + +

mille feuille

mille feuille